| کد مقاله | کد نشریه | سال انتشار | مقاله انگلیسی | نسخه تمام متن |

|---|---|---|---|---|

| 5002892 | 1368458 | 2016 | 5 صفحه PDF | دانلود رایگان |

عنوان انگلیسی مقاله ISI

Image Processing of Composite Video with FPGA Programmable Logic

ترجمه فارسی عنوان

استفاده از منطق برنامهنویسی FPGA در پردازش تصویر ترکیبی

همین الان دانلود کنید

دانلود مقاله ISI انگلیسی

رایگان برای ایرانیان

کلمات کلیدی

پردازش تصویر، ITU-R BT.656، FPGA، منطق برنامهنویسی، آستانه، آشکارسازی لبه

فهرست مطالب مقاله

چکیده

کلمات کلیدی

1.مقدمه

2. منطق برنامهنویسی برای پردازش تصویری

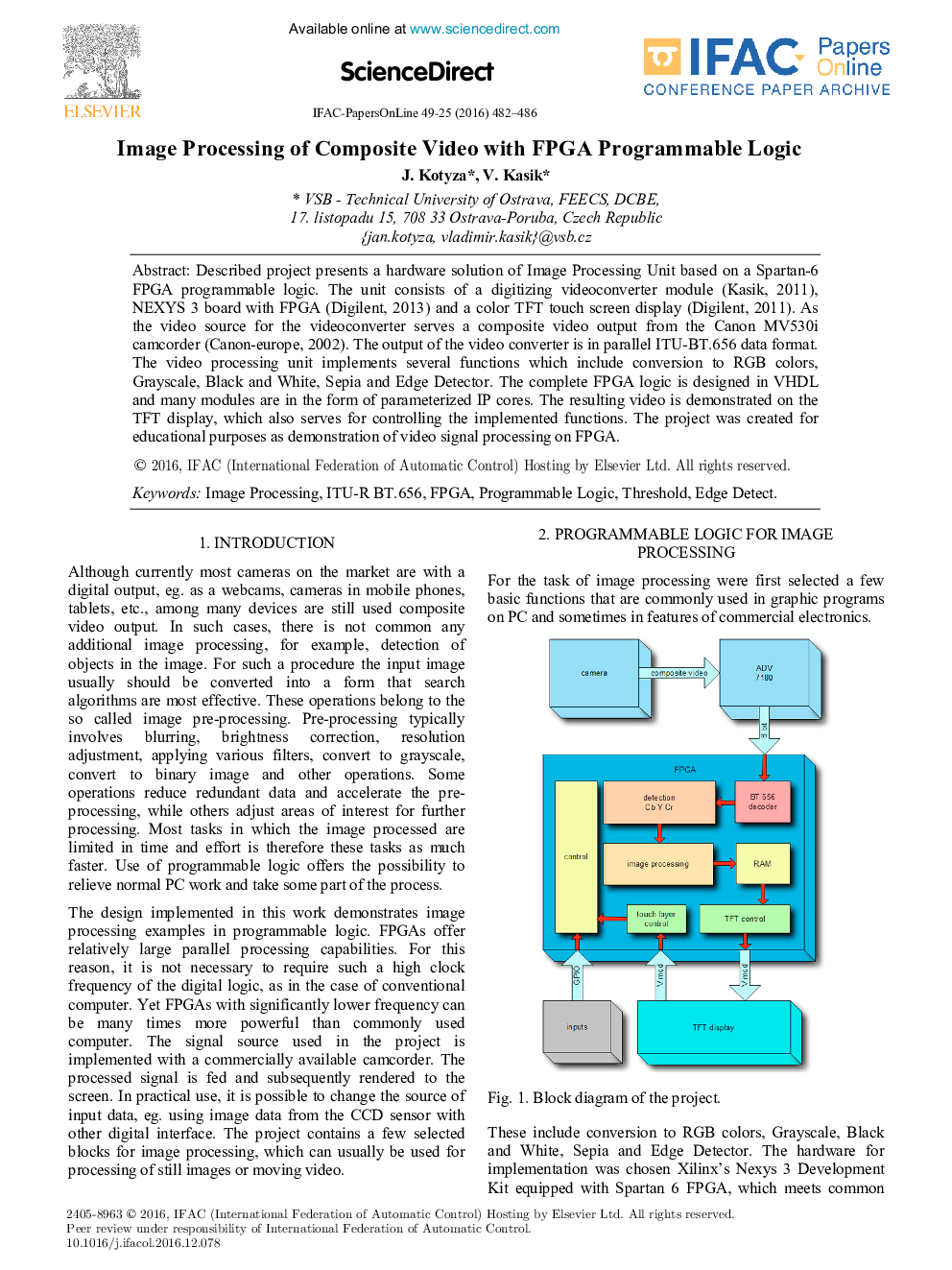

شکل1. نمایش کلی مدار این پروژه

جدول1. سیگنالهای زمانسنج این طراحی

3. منبع سیگنال تصویری

شکل2. دوربین فیلمبرداری کنون MV530.

شکل3. صفحه نمایش شبکه با سیگنالهای کنترلی

4. صفحه نمایش لمسی رنگی

4.1. لایهی لمسی صفحه نمایش

جدول2. مقاومت لایهی صفحه نمایش لمسی

جدول3. ضرایب 12 بیتی برای نقاط مرزی لایهی لمسی

شکل4. دو مرحلهی اندازهگیری مختصات لایهی لمسی

5. طراحی منطق برنامهنویسی

5.1. رمزگشای ITU-BT.656

شکل5. آشکارساز تصویری دیاگرام FSM

جدول4. مقادیر SAV و EAV

شکل6. رکورد ChipScope مربوط به آشکارساز دادهی تصویری

5.2. تبدیل به شکل RGB

شکل7. هستهی IP مبدل CbYCr به RGB

5.3. تبدیل به رنگ خاکستری و قرمز قهوهای

جدول5. رجیستر کشف-لبه

5.4.آشکارساز لبهای

شکل8. دیاگرام FSM مربوط به مدیریت توان صفحه نمایش

5.5.ناظر صفحه نمایش TFT

6. رابط کاربر

شکل9. چهار صفحهی رابط کاربر.

جدول6. تاخیر ماژول

7. نتیجهگیری

کلمات کلیدی

1.مقدمه

2. منطق برنامهنویسی برای پردازش تصویری

شکل1. نمایش کلی مدار این پروژه

جدول1. سیگنالهای زمانسنج این طراحی

3. منبع سیگنال تصویری

شکل2. دوربین فیلمبرداری کنون MV530.

شکل3. صفحه نمایش شبکه با سیگنالهای کنترلی

4. صفحه نمایش لمسی رنگی

4.1. لایهی لمسی صفحه نمایش

جدول2. مقاومت لایهی صفحه نمایش لمسی

جدول3. ضرایب 12 بیتی برای نقاط مرزی لایهی لمسی

شکل4. دو مرحلهی اندازهگیری مختصات لایهی لمسی

5. طراحی منطق برنامهنویسی

5.1. رمزگشای ITU-BT.656

شکل5. آشکارساز تصویری دیاگرام FSM

جدول4. مقادیر SAV و EAV

شکل6. رکورد ChipScope مربوط به آشکارساز دادهی تصویری

5.2. تبدیل به شکل RGB

شکل7. هستهی IP مبدل CbYCr به RGB

5.3. تبدیل به رنگ خاکستری و قرمز قهوهای

جدول5. رجیستر کشف-لبه

5.4.آشکارساز لبهای

شکل8. دیاگرام FSM مربوط به مدیریت توان صفحه نمایش

5.5.ناظر صفحه نمایش TFT

6. رابط کاربر

شکل9. چهار صفحهی رابط کاربر.

جدول6. تاخیر ماژول

7. نتیجهگیری

ترجمه چکیده

در این مقاله به بررسی راهحل سختافزاری واحد پردازش تصویری بر اساس منطق برنامهنویسی Spartan-6FPGA پرداخته شده است. این واحد حاوی یک ماژول مبدل تصویر دیجیتالی (کاسیک، سال 2011) بورد NEXYS 3 همراه با FGPA (دیجیلنت، سال 2013) و یک صفحهی نمایش رنگی TFT (دیجیلنت، سال 2011) است. بدین صورت که منبع مبدل تصویر، یک خروجی تصویر ترکیبی را از دوربین فیلمبرداری کنون MV530i (کنون، اروپا، 2002) به کار میبرد. خروجی این مبدل موازی با قالب دادههای ITU-BT.656 است. واحد پردازش تصویری توابع متعددی را ایجاد میکند که شامل تبدیل به رنگهای RGB، خاکستری، سیاه سفید، قرمز قهوهای و آشکارگر لبهها است. منطق کامل FPGA در VHDL طراحی میشود و ماژولهای زیادی در قالب هستههای پارامتریک IP حضور دارند. تصویر حاصل در نمایشگر TFT نشان داده میشود که برای کنترل توابع اجرا شده به کار برده میگردد. این پروژه در راستای اهداف علمی برای نمایش پردازش سیگنالی تصویری در FPGA تعریف شده است.

موضوعات مرتبط

مهندسی و علوم پایه

سایر رشته های مهندسی

مکانیک محاسباتی

چکیده انگلیسی

Described project presents a hardware solution of Image Processing Unit based on a Spartan-6 FPGA programmable logic. The unit consists of a digitizing videoconverter module (Kasik, 2011), NEXYS 3 board with FPGA (Digilent, 2013) and a color TFT touch screen display (Digilent, 2011). As the video source for the videoconverter serves a composite video output from the Canon MV530i camcorder (Canon-europe, 2002). The output of the video converter is in parallel ITU-BT.656 data format. The video processing unit implements several functions which include conversion to RGB colors, Grayscale, Black and White, Sepia and Edge Detector. The complete FPGA logic is designed in VHDL and many modules are in the form of parameterized IP cores. The resulting video is demonstrated on the TFT display, which also serves for controlling the implemented functions. The project was created for educational purposes as demonstration of video signal processing on FPGA.

ناشر

Database: Elsevier - ScienceDirect (ساینس دایرکت)

Journal: IFAC-PapersOnLine - Volume 49, Issue 25, 2016, Pages 482-486

Journal: IFAC-PapersOnLine - Volume 49, Issue 25, 2016, Pages 482-486

نویسندگان

J. Kotyza, V. Kasik,