Contents lists available at ScienceDirect

### Solid State Communications

journal homepage: www.elsevier.com/locate/ssc

# Metalorganic chemical vapor deposited $\rm DyScO_3$ buffer layer in $\rm Pt/Bi_{3.25}Nd_{0.75}Ti_3O_{12}/DyScO_3/Si$ metal-ferroelectric-insulator-semiconductor diodes

#### R. Thomas\*, R.E. Melgarejo, N.M. Murari, S.P. Pavunny, R.S. Katiyar\*

Department of Physics and Institute for Functional Nanomaterials, P.O. Box 23343, University of Puerto Rico, San Juan, PR 00931-3343, USA

#### ARTICLE INFO

Article history: Received 17 June 2009 Received in revised form 13 August 2009 Accepted 21 August 2009 by T. Kimura Available online 28 August 2009

PACS: 77.55.+f 77.84.Dy 81.15.Gh

Keywords: A. Bi<sub>3.25</sub>Nd<sub>0.75</sub>Ti<sub>3</sub>O<sub>12</sub> A. DyScO<sub>3</sub> D. MFIS D. Memory window

#### ABSTRACT

High-k DyScO<sub>3</sub> linear dielectric films were considered as a buffer layer for the metal-ferroelectricinsulator-semiconductor (MFIS) structures with Aurivillius Bi<sub>3.25</sub>Nd<sub>0.75</sub>Ti<sub>3</sub>O<sub>12</sub> ferroelectric films. The DyScO<sub>3</sub> films on Si substrates were amorphous and dense with a smooth surface morphology, showing negligible CV hysteresis and low leakage current. The remnant polarization of ~20  $\mu$ C/cm<sup>2</sup>, dielectric constant ~400, and the loss tangent ~0.04 were obtained for the ferroelectric Bi<sub>3.25</sub>Nd<sub>0.75</sub>Ti<sub>3</sub>O<sub>12</sub> film on Pt/TiO<sub>2</sub>/SiO<sub>2</sub>/Si substrates. The Pt/Bi<sub>3.25</sub>Nd<sub>0.75</sub>Ti<sub>3</sub>O<sub>12</sub>/DyScO<sub>3</sub>/Si MFIS capacitors showed a large memory window of 4.0 V and excellent retention up to 1000 s, encouraging results for practical applications in nonvolatile RAM.

© 2009 Elsevier Ltd. All rights reserved.

A significant amount of power is required for dynamic random access memories (DRAM) to refresh the capacitor compared to the non-volatile RAM (NVRAM). In fact, flash RAM currently dominates the market of non-volatile memories, but this memory is not as fast as DRAM and has a finite number of erase-write cycles. The polarization bistability of the ferroelectric material offers the possibility to develop high-density, low power, faster write speed, maximum write-erase cycles and radiation resistance NVRAM; alternate to both DRAM and Flash [1,2]. However, the high deposition temperature and oxidizing atmosphere required for the ferroelectric oxide thin film growth promote inter-diffusion into silicon and vice versa when a FE is integrated with the complementary metal oxide semiconductor (CMOS) process flow. This accelerates fatigue and imprint which ultimately results in device failure [3]. Hence, the Metal-Ferroelectric-Insulator-Semiconductor (MFIS) structure, 1-T FeRAM, is of great importance in nonvolatile memories, as the insulating buffer layer that prevents interdiffusion between the components of the ferroelectric material and the Si substrate [4]. Moreover, a buffer layer can reduce the lattice mismatch between the ferroelectric layer and silicon substrate [5]. However, an insulating buffer layer has some disadvantages viz. generation of a depolarization field in the ferroelectric film and increase of the operating voltage by weakening the electric field across the ferroelectric layer. In the case of the SiO<sub>2</sub> ( $\varepsilon_r = 3.9$ ) buffer layer, the saturation voltage is extremely high compared to hafnium oxide  $(\varepsilon_r \approx 25)$  [6]. Hence, it is important to find an insulating buffer layer with a high  $\varepsilon_r$  (compared to  $\varepsilon_r = 3.9$  of SiO<sub>2</sub>). Various highk materials viz. LaAlO<sub>3</sub>, HfO<sub>2</sub>, ZrO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>, SrTiO<sub>3</sub>, etc. have been studied as buffer layers in the MFIS structures. Increasing the  $\varepsilon_r$ alone does not ensure a workable solution as the band gap reduces with increasing  $\varepsilon_{r}$ ; which significantly reduces the conduction/valance band offset with Si thereby leakage through the buffer layer will be another problem. Hence, a gate-oxide with a reasonable band offset (>1 eV) may be the ideal choice as a buffer layer due to the fact that, the interface between Si and the ferroelectric is the main concern in reliable device applications. Considering these requirements of buffer layers, high-k DyScO<sub>3</sub> (DSO) gate-oxide seems to be promising for MFIS structures for nonvolatile memory applications. Also these devices are based on silicon inter connect technologies, it is important to choose an insulating layer that is amorphous and thermodynamically stable with the substrate.

Aurivillius phase Bi<sub>4</sub>Ti<sub>3</sub>O<sub>12</sub> (BTO) and its rare-earth doped derivatives have attracted much attention in recent years for non-

Solid state communications results to the test of the

<sup>\*</sup> Corresponding author. Tel.: +1 787 751 4210; fax: +1 787 764 2571. *E-mail addresses*: etreji@yahoo.com (R. Thomas), rkatiyar@uprrp.edu (R.S. Katiyar).

<sup>0038-1098/\$ –</sup> see front matter s 2009 Elsevier Ltd. All rights reserved. doi:10.1016/j.ssc.2009.08.032

volatile memory applications as lead free ferroelectric materials with large remnant polarization, less fatigue, and low processing temperatures [7]. In this article, a DSO linear dielectric film based metal-insulator-silicon (*MIS*); Bi<sub>3.25</sub>Nd<sub>0.75</sub>Ti<sub>3</sub>O<sub>12</sub>(BNT) nonlinear dielectric film based metal-ferroelectric-metal (*MFM*); and the possibility of a DSO insulator as a buffer layer for the metalferroelectric-insulator-silicon (*MFIS*) structures with BNT ferroelectric films are considered for non-volatile memory applications.

DSO films were deposited on Si (100) wafers by Metal Organic Chemical Vapor Deposition (MOCVD) whereas BNT thin films were prepared by chemical solution deposition on Pt/TiO<sub>2</sub>/ SiO<sub>2</sub>/Si and DSO/Si substrates [8]. These films were annealed at 700 °C for 20 min. The structural properties of the DSO films were examined by grazing incidence x-ray diffraction and that of Bi<sub>3.25</sub>Nd<sub>0.75</sub>Ti<sub>3</sub>O<sub>12</sub> film on Pt/TiO<sub>2</sub>/SiO<sub>2</sub>/Si and DyScO<sub>3</sub>/Si substrates were examined by the Bragg-Brentano method [XRD, Philips Analytical] using Cu-K $\alpha$  radiation. High-resolution transmission electron microscopy (HRTEM) studies were performed to understand the interface between the DSO and the Si substrate. The surface morphology was investigated by using atomic force microscopy (AFM, Digital Instruments). MIS, MFM and MFIS capacitors were processed with sputter deposited Pt top electrodes. Current-Voltage (IV) characteristics were recorded using a #6517A Keithley programmable electrometer. Small signal capacitance-voltage (CV) measurements were made with a HP4294A Precision Impedance Analyzer, using an oscillation level of 50 mV superimposed on the bias voltage. Ferroelectric properties (P-V hysteresis) were measured using a RT500V from Radiant Technologies.

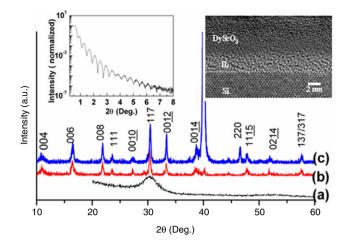

X-ray diffraction (grazing incidence and  $\theta - 2\theta$ ) patterns of the films annealed at 700 °C are given in Fig. 1. In the case of DSO on Si (grazing incidence) there was only one broad peak around 31°, which might be due to the short-range ordering (SRO). TEM (inset1, Fig. 1) clearly depicts the amorphous nature of the DSO films with an amorphous interlayer ( $\sim 2.2 \pm 0.2$  nm) SiO<sub>x</sub> between Si and DSO film. Using the x-ray reflectance spectra (inset2, Fig. 1), thickness (d) and density ( $\rho$ ) were determined from the spacing of the fringes ( $\Delta\theta$ ) and critical incidence angle for total reflection( $\theta_c$ ), respectively, using the relations [9].

$$d = \frac{\lambda}{2(\Delta \theta)}; \qquad \rho = \theta_c^2 \pi A / N_a r_0 \lambda^2 Z \tag{1}$$

where  $N_a$  is Avogadro's number,  $r_0$  is the classical electron radius,  $\lambda$  is the x-ray wavelength (CuK<sub> $\alpha$ </sub> in our case), A and Z are the atomic number and mass, respectively. The extracted thickness of the DyScO<sub>3</sub> layer was around 22 nm and the density was around 5.9 g/cm<sup>3</sup>. X-ray diffraction pattern (Fig. 1) of BNT film on Pt/TiO<sub>2</sub>/SiO<sub>2</sub>/Si and DSO/Si were obtained in the Bragg–Brentano geometry. The pyrolysed multi-layered films were amorphous and upon annealing at 700 °C films became polycrystalline without any preferred orientation for both types of substrate, similar to Bi<sub>4</sub>Ti<sub>3</sub>O<sub>12</sub> ceramic and comparable to the reported results [10,11].

The surface morphology of DSO/Si, BNT/DSO/Si and BNT/Pt/ TiO<sub>2</sub>/SiO<sub>2</sub>/Si structures is shown in Fig. 2. In the case of DSO/Si, AFM showed a surface roughness of ~0.2 nm, matching the level of Si (100) substrate surface roughness (~0.15 nm) and for BNT/DSO/Si and BNT/Pt/TiO<sub>2</sub>/SiO<sub>2</sub>/Si, morphology showed a larger grain growth with an rms roughness of around 10 and 12 nm, respectively for the film with a thickness of ~270 nm, which are very high compared to the underlying DSO (0.2 nm) and Pt layer (rms roughness ~1–1.5 nm), which may be due to grain growth at the annealing temperature. Also, the morphology of BNT on DSO/Si was different compared to the films on the Pt/TiO<sub>2</sub>/SiO<sub>2</sub>/Si substrate where the grains were more rounded compared to the flake like growth on Pt.

**Fig. 1.** X-ray diffraction patterns of (a) DSO/Si, (b) BNT/DSO/Si and (c) BNT/Pt/ TiO<sub>2</sub>/SiO<sub>2</sub>/Si. Insets show X-ray reflectance spectra and HRTEM cross-sectional view of the DSO/Si structure.

Fig. 3 shows the CV characteristics of the Pt/DSO/Si structures measured at 100 kHz by sweeping the voltage from the inversion to accumulation and back to inversion. The MIS or MFIS capacitance is given by the series combinations [12].

$$\frac{1}{C} = \frac{1}{C_f} + \frac{1}{C_i} + \frac{1}{C_{\text{SiO}_2}} + \frac{1}{C_s}.$$

(2)

where,  $C_f$  and  $C_i$  are the capacitances of the ferroelectric and insulator layers (BNT and DSO in the present case), C<sub>SiO2</sub> interlayer capacitance and C<sub>s</sub> are the voltage variable capacitance of the semiconductor (Si in the present case). At accumulation (C<sub>max</sub>) the measured capacitance is due to the insulator layers alone as  $C_s$  is infinite due to the disappearance of depletion layer. The dielectric constant  $(\varepsilon_r)$  extracted from the accumulation was 26.9 (neglecting first term in Eq. (2) and using SiO<sub>2</sub> thickness as 2.2 nm and  $\varepsilon_r$  as 3.9); close to the dielectric constant (24) of DSO calculated from the Clausius-Mosotti Equation using the molecular polarizabilities of  $Dy_2O_3$  and  $Sc_2O_3$  [13]. As can be seen from the figure the hysteresis is negligibly small (<5 mV), suggestive of low rechargeable trap density. The presence of the sharp slope at the depletion region suggested a very low fixed charge density  $(10^{11}/\text{cm}^2)$  at the interface and bulk of the film. The leakage current density as a function of voltage at the accumulation region (Fig. 3 inset) suggests a very low leakage with a current density of around  $6 \times 10^{-8}$  Å/cm<sup>2</sup> at -2 V. In nutshell, all of these features are desirable for introducing this material as a buffer layer between Si and ferroelectric thin films for NVRAM applications.

BNT thin films were deposited by chemical solution deposition on Pt/TiO<sub>2</sub>/SiO<sub>2</sub>/Si to study dielectric and ferroelectric properties of the MFM structures. The observed P-E hysteresis loop is shown in Fig. 4. The remnant polarization (Pr) and the coercive field (Ec) were 20.0  $\mu$ C/cm<sup>2</sup> and 62 kV/cm, respectively for the 270 nm film, comparable to the values reported earlier [14]. The inset of Fig. 4 shows C-V plots for the film at 100 kHz. This butterfly loop also supports the ferroelectricity in the present film. The average coercive field extracted from the capacitance maxima was 58 kV/cm, slightly lower than the one obtained from P-E hysteresis. In the case of P-E measurements, the coercive field shows measurement frequency dependence, and increases with increasing frequency. The ac signal for CV measurement in the present case was 100 mV, which is too small to switch the spontaneous polarization. As the spontaneous polarization is switched by the bias voltage, the Ec from the CV measurement depends on the sweep rate of the bias voltage, which was very slow (<1 V/s) in the present case. Therefore it is reasonable that the Ec Download English Version:

## https://daneshyari.com/en/article/1595022

Download Persian Version:

https://daneshyari.com/article/1595022

Daneshyari.com