FISEVIER

Contents lists available at ScienceDirect

### Microelectronic Engineering

journal homepage: www.elsevier.com/locate/mee

#### Research paper

## Localized porous silicon structures obtained by using shadow mask-assisted patternable illumination

Jongho Park<sup>a,b,\*</sup>, Beomjoon Kim<sup>b</sup>

- <sup>a</sup> Laboratory for Future Interdisciplinary Research of Science and Technology, Tokyo Institute of Technology, 4259 Nagatsuta-cho, Midori-ku, Yokohama, Kanagawa 226-8503. Japan

- b Institute of Industrial Science, The University of Tokyo, 4-6-1 Komaba, Meguro-ku, Tokyo 153-8505, Japan

#### ARTICLE INFO

# Keywords: Porous silicon Localized porous structure Patterning Shadow mask Illumination

#### ABSTRACT

In this work, localized porous silicon structures were fabricated using patterned illumination by shadow masks. For comparative analysis, selective formation of porous silicon structures was performed using metal (chromium) and insulating (SU-8 photoresist) masking layers. Various porous structures were fabricated and the types of silicon substrates and configurations of masking layers were investigated. Localized porous structures were successfully fabricated on n-type silicon substrates using a double-tank electrochemical cell and a patterned shadow mask. The developed fabrication method requires no deposition or pre-patterning of the masking layers. Thus, the fabrication of localized porous structures is simpler and faster than that based on conventional methods.

#### 1. Introduction

Since porous silicon was firstly reported, various studies were performed using its characteristics such as micro- and nano-sized porous structures and the high surface area-volume ratio [1,2]. Studies about optical implementations [3–5] and bioanalytical applications [6–8] using porous silicon substrates have attracted much attention. Porous silicon is generally fabricated by anodic etching of silicon substrates in electrolytes containing hydrofluoric acid. Although an exact theoretical model has not been defined, it has been proposed and discussed that hydrofluoric ions of electrolytes and holes in the silicon substrate play significant roles in the pore formation of silicon substrates [9–12]. Previously, we successfully investigated the fabrication of n- and p-type porous silicon using the double-tank electrochemical cell system [13]. In addition, we confirmed that illumination used for the generation of electron-hole pairs and its wavelength influence the porous structures.

Several applications using porous silicon substrates, such as biochips and optical devices, require the formation of porous structures in specific areas. Such localized porous structures are usually fabricated by local etching using masking layers patterned by conventional photolithography. Numerous studies have been performed to obtain localized porous structures by introducing various masking layers prior to anodic etching of silicon substrates. Masking layers include amorphous silicon [14], silicon oxide [15], silicon nitride [16–18], silicon carbide

[19,20], metal [19,21,22], ion implantation [23,24], photoresist [25–27], fluoropolymer [28,29], and other materials [30]. However, the method based on masking layers has several drawbacks. For example, the preparation of masking layers requires several steps such as the deposition and patterning of each layer before anodic etching. Moreover, the material and patterning process should be carefully chosen and arranged to avoid the undesirable formation and removal of porous structures and damage of masking layers during the subsequent process. Thus, a new method is required to fabricate localized porous silicon structures in simpler and easier steps.

Previously, we confirmed that illumination is necessary to form porous silicon structures with specific conditions in a double-tank cell system. Thus, we controlled the illumination using patterned shadow masks in this work, which resulted in limitations of illuminated area of a substrate to realize localized porous silicon structures without patterning the masking layer. At the same time, we performed local anodic etching using conventional masking methods to compare the shapes and dimensional changes of porous structures with that described in the literatures.

E-mail address: park.j.ah@m.titech.ac.jp (J. Park).

<sup>\*</sup> Corresponding author at: Laboratory for Future Interdisciplinary Research of Science and Technology, Tokyo Institute of Technology, 4259 Nagatsuta-cho, Midori-ku, Yokohama, Kanagawa 226-8503, Japan.

#### 2. Materials and methods

#### 2.1. Materials

We used p- and n-type silicon wafers with  $\langle 100 \rangle$  crystal orientation and a resistivity of 1–10  $\Omega$ ·cm as porous silicon substrates. We prepared the organic electrolyte by mixing 48% hydrofluoric acid (HF solution, Wako Pure Chemical Industries, Ltd.) with 99% *N,N*-Dimethylformamide (DMF, Wako Pure Chemical Industries, Ltd.) at a ratio of 1:5 ( $\nu$ / $\nu$ ) and used fresh electrolyte for every etching process. A light-emitting diode (LED) lamp (7 W, LED132CW/WW, Plata Inc.) was used for backside illumination during anodic etching.

#### 2.2. Preparation of masking patterns for localized anodic etching

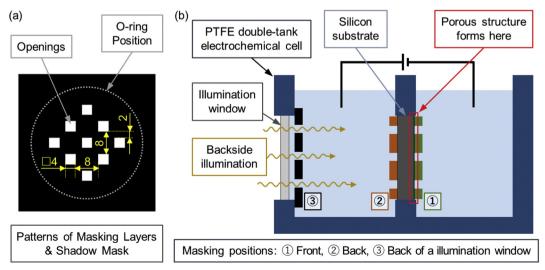

Prior to the deposition and patterning of the masking layer, all silicon substrates were cleaned with acetone, ethanol, and deionized water using an ultrasonic bath. Subsequently, the cleaned substrates were dipped in hydrofluoric acid solution to remove the native oxide layer. We prepared two types of masking layer materials in this work: 1) Chromium (Cr), as a conductive masking layer; and 2) SU-8 photoresist (SU-8 3005, MicroChem Co.), as an insulating masking layer. For Cr mask patterns, a 200 nm thick Cr layer was firstly deposited on a silicon substrate by RF sputtering (SVC-700RF-I, Sanyu Electron Co., Ltd.). The masking layers were then patterned by conventional photolithography and wet etching. We designed a masking pattern containing diagonal  $3 \times 3$  array of squares with a length of 4 mm on each side (Fig. 1(a)). The SU-8 masking patterns were fabricated in a similar manner. The SU-8 layer with a thickness of 10 µm was firstly coated on a silicon substrate by spin-coating and soft-bake processes. Masking patterns were then fabricated by photolithography and SU-8 development. In addition, dicing tapes were used to protect the side that was already patterned when the substrate needed to be patterned on both sides. The patterns designed for shadow masks were transferred on a silver bromide-coated polyethylene terephthalate (PET) film by laser exposure, fixing, and development processes (Unno Giken Co., Ltd).

## 2.3. Local anodic etching of silicon substrates using masking layers and a shadow mask

We employed the double-tank electrochemical cell system, which was also used in our previous work [13]. Briefly, the cell consists of polytetrafluoroethylene (PTFE) chambers, platinum electrodes (PT-351384, Nilaco Co.), and a sapphire wafer (Shinkosha Co., Ltd.) as the

window for illumination. The masking layers and shadow mask were positioned on the front and back of the silicon substrate and on the back of the window for illumination (Fig. 1(b)). We combined three masking positions considering the masking layer materials and type of silicon substrates.

Anodic etching of silicon was performed galvanostatically in the PTFE double-tank cell assembly. The backside of a silicon substrate was illuminated during electrochemical etching using a LED lamp 50 mm from the substrate. We applied a current of 5 mA/cm² for 30 min for all substrates during anodic etching. Once the etching process was completed, the porous silicon substrate was thoroughly rinsed with new DMF solution and hexane (Wako Pure Chemical Industries, Ltd.). Fabricated porous structures were observed using an optical microscope and scanning electron microscope (SEM; JSM-6301F, JEOL Ltd.). All SEM images were mainly taken at the boundary between an opening area and a masking area of porous silicon substrates unless otherwise stated. The representative dimensions of the pore diameters and pore depths were all measured near the center of each porous structure area.

#### 3. Results and discussion

#### 3.1. Localized porous structure using p-type silicon substrates

#### 3.1.1. Anodic etching with a chromium masking layer

Firstly, we performed local anodic etching of p-type silicon substrates using a metal masking layer (Cr) in a double-tank cell. The Cr layer was chosen as metal masking layer in this work because it can be prepared simply by using conventional photolithography and physical deposition methods such as sputtering or thermal evaporation. In addition, we adjusted the thickness of the deposited Cr layer to 200 nm to completely block the light from illumination during anodic etching [31].

Fig. 2 shows SEM images of porous structures fabricated using Cr masking layers. We confirmed that undercut etching occurs beneath the edges of the masking layer in case of front and front-back masking (Fig. 2(a and c)). The undercut porous structures beneath the masking layer faces toward the opening of the masking layer, which indicates the current flow direction. Similar undercut shapes of porous structures have been reported in the literature [14–29]. For example, Steiner et al. reported four different pore formation patterns with respect to different mask configurations and substrate types [32]. They described that the current flow changes during the anodic etching process depending on masking patterns, which results in different undercut shapes. In our work, the pore formations obtained using the metal masking layer differ

Fig. 1. (a) Design of masking patterns used in this work, (b) Schematic diagram of the local anodic etching setup with respective masking positions.

#### Download English Version:

## https://daneshyari.com/en/article/10139644

Download Persian Version:

https://daneshyari.com/article/10139644

<u>Daneshyari.com</u>