Contents lists available at ScienceDirect

## Microelectronics Journal

journal homepage: www.elsevier.com/locate/mejo

## Impact of elliptical cross-section on the propagation delay of multi-channel gate-all-around MOSFET based inverters

Subindu Kumar\*, Shankaranand Jha

Department of Electronics Engineering, Indian School of Mines, Dhanbad, Jharkhand 826004, India

#### ARTICLE INFO

Article history: Received 15 October 2012 Received in revised form 4 June 2013 Accepted 11 June 2013 Available online 4 July 2013

Metal-oxide-semiconductor field-effect transistor (MOSFFT) Gate-all-around (GAA) Effective diameter Multi-channel Propagation delay Scaling

#### ABSTRACT

Multi-channel (MC) gate-all-around (GAA) metal-oxide-semiconductor field-effect transistor (MOSFET) is one of the promising candidates for the next-generation high performance devices. However, due to fabrication imperfections the cross-section of GAA devices may be ellipse-shaped having different major (a) and minor (b) axes, instead of the theoretically ideal round shape. The aspect ratio (AR), defined as a/b, of such elliptical GAA devices can vary depending on a and b. This introduces variability in the effective diameter, which in turn affect the performance parameters of circuits based on elliptical GAA MOSFETs. In the present work we have investigated the impact of diameter variability on the transient response of MC elliptical GAA MOSFET based CMOS inverters with a novel perspective. We have modeled the spread in the effective diameter by a parameter,  $\sigma$ , the standard deviation (SD), which may be thought of as a quantitative measure of the amount of variability introduced in the device. We have elaborated the 'ON-Resistance' method for calculating the propagation delay of MC GAA MOSFET based CMOS inverters. Computations were carried out to show the dependence of the propagation delay of such inverters on some important device/circuit parameters. We have also shown that even long channel elliptical devices can offer significant reduction of circuit delay (comparable to short channel devices) by proper tuning the effective diameter and number of channels, provided the admissible small dimensional effects have been taken into account.

© 2013 Elsevier Ltd. All rights reserved.

#### 1. Introduction

Gate-All-Around (GAA) metal-oxide-semiconductor field-effect transistors (MOSFETs) are high priority research topics of the present day. The gate structure in GAA MOSFETs makes them the most efficient among 3D devices [1-3]. GAA devices offer full electrostatic control over the channel [2] and there is a significant reduction in small dimensional effects [3] which in turn enhances the performance parameters of circuits based on these devices. All these make GAA MOSFETs the most promising structures to extend the scaling of CMOS devices. In addition, silicon (Si) GAA MOSFETs with multi-channel (MC) show excellent current driving capability [4–9] and they are also compatible with conventional CMOS processes [10,11]. Recently, CMOS compatible MC GAA MOSFETs having diameters ≤5 nm have been demonstrated with excellent performance [12]. Due to limitations in the fabrication process, GAA MOSFETs having an ideal circular cross-section may not be achieved. The fabricated structure may have elliptical crosssection [13-15] with different major and minor axes. The ideally circular cross-section of GAA MOSFET may not give the optimized

circuit performance. Primary works on elliptical GAA MOSFETs include the studies of Li and Hwang [16] on the effect of geometry aspect ratio on elliptical GAA MOSFETs and circuits. Bangsaruntip et al. [17] proposed the universality of short channel effects in undoped-body silicon nanowire MOSFETs having elliptical crosssection. Zhang et al. [18] proposed the concept of effective radius to convert elliptical GAA MOSFETs into equivalent circular GAA MOSFETs for studying short channel effects.

Inverters form the basic building block of complex digital circuits. The performance of the inverter depends on the structure of the n- and p-MOSFETs. Due to the enhanced electronic properties of GAA MOSFETs, inverters based on such structures show better performance than their planar counterpart [19]. As one of the most important performance parameters in CMOS digital circuits, propagation delay is of concern to designers and users. Both the speed/frequency and dynamic power dissipation of a circuit are affected by propagation delay, so timing analysis has been investigated for several decades [20–25]. In such methods the macroscopic effect of the transistors were taken into account where both the n- and p-MOS devices furnished current through a single channel. For a MC device the total current is the sum of individual currents furnished by each channel. Incorporating such microscopic effects in determining the propagation delay may result in exhaustive and time consuming computations. One of the

<sup>\*</sup> Corresponding author. Tel.: +91 9471191160; fax: +91 326 2296622. E-mail address: subindukumar@hotmail.com (S. Kumar).

ways of analyzing the propagation delay is to replace the device with its on-resistance, extract the load capacitance and calculate the RC time constant. The ON-resistance method allows fast and straightforward delay analysis avoiding time consuming numerical simulations. Circuits based on GAA devices have been previously analyzed [26] with the help of ON-resistance method. The advantage of this method as applicable to MC devices, is the microscopic analysis of individual channels in terms of its on-resistance. This enables us to include the effect of individual channel properties in the propagation delay through a fairly straight forward way. One of the prime concerns in On-resistance method is its accuracy. which can be improved by proper evaluation of the channel on-resistance, as discussed later in our proposed algorithm. Several other approaches also use such strategy for the transient analysis [27-32]. Thus it seems reasonable to extend the use of this principle to capture the transient characteristics of MC GAA MOSFET based circuits. The propagation delay of GAA MOSFET based inverters is subject to change when the effective diameter of Si channel deviates from its ideal circular shape.

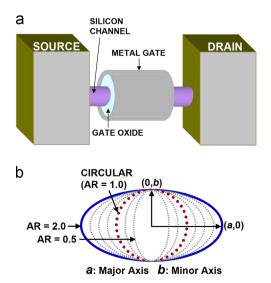

A schematic representation of a single channel GAA MOSFET is shown in Fig. 1a. The cross-section of an elliptical GAA MOSFET with major (a) and minor (b) axes is illustrated in Fig. 1b. The geometric aspect ratio (AR) of the elliptical GAA MOSFET is defined as the ratio a/b. A perfectly circular cross-section bears an AR of 1.0 when a and b are equal. Depending on a and b, the crosssection can have several elliptical geometries with varying ARs as depicted in Fig. 1b. The impact of elliptical cross-section on the propagation delay of GAA MOSFET based inverters has not been widely discussed. Owing to the persisting technological importance of long channel MOSFETs [4-6,8,33], in this paper, we have modeled the spread in effective diameter of long channel elliptical GAA MOSFET by a parameter,  $\sigma$ , the standard deviation (SD) and its impact on the propagation delay of GAA MOSFET based CMOS inverters have been investigated. To the best of our knowledge, for the first time, we have applied the 'ON-Resistance' method to calculate the propagation delay of MC GAA MOSFET based CMOS inverters. The dependence of the propagation delay of such inverters on some important parameters such as gate oxide thickness, AR, number of channels and so on, is also investigated, with emphasis on the spread in scaling parameter (SP) and device variability.

**Fig. 1.** Schematic representation of (a) single channel GAA MOSFET and (b) the cross-section of an elliptical GAA device with major and minor axes.

#### 2. Theoretical details

The threshold voltage of a long n-channel GAA MOSFET is given by [34]

$$V_{th} = V_{t0} + \Delta V_t \tag{1}$$

where  $V_{t0}$  is the threshold voltage that is similar to that of the bulk MOSFETS [35] and  $\Delta V_t$  is the additional component of the threshold voltage due to the special geometry of GAA MOSFETs given by

$$V_{t0} = \Delta \varphi + 2\phi_f + \frac{Q_{dep}}{C_{ox}} - \frac{1}{\beta} \ln \left( \frac{2\beta q N_a \varepsilon_{si}}{C_{ox}^2} \right)$$

(2)

and

$$\Delta V_t = -\left(\frac{1}{\beta}\right) \ln\left(\frac{2C_{ox}}{\beta q N_a d_{eff}}\right) \left[1 - \exp\left(-\frac{q^2 N_a d_{eff}^2}{16\varepsilon_{si} kT}\right)\right]$$

(3)

respectively. The parameters  $\Delta\phi$ ,  $t_{ox}$ ,  $\phi_f$  and  $N_a$  are the work function difference between the gate material and silicon body, thickness of the gate oxide, Fermi potential and impurity concentration in the silicon body respectively. The effective oxide capacitance and the depletion charge density per unit gate area  $C_{ox}$  and  $Q_{dep}$  are given by  $2\varepsilon_{ox}/[d_{eff}\ln(1+2t_{ox}/d_{eff})]$  and  $qN_ad_{eff}/4$  respectively, with  $n_i$ , q, k, T,  $\varepsilon_{ox}$  and  $\varepsilon_{si}$  have their usual physical meanings. The effective diameter of the elliptical silicon body,  $d_{eff}$  is given by [18]

$$\frac{8\varepsilon_{ox}}{4\varepsilon_{si}d_{eff}t_{ox}+\varepsilon_{ox}d_{eff}^2} = \frac{\varepsilon_{ox}}{2\varepsilon_{si}at_{ox}+\varepsilon_{ox}a^2} + \frac{\varepsilon_{ox}}{2\varepsilon_{si}bt_{ox}+\varepsilon_{ox}b^2}$$

(4)

To take into account the quantum mechanical effects arising due to the ultra-nanometric diameter of GAA devices, we have incorporated an additional component  $\Delta V_{QM}$  [36] in (1). The overall threshold voltage now takes the form

$$V_{th} = V_{t0} + \Delta V_t + \Delta V_{OM} \tag{5}$$

The modeling of drain current of GAA MOSFETs have been reported by several research groups [37-39]. In such models an undoped Silicon body have been used. However, fabricated GAA devices will always contain certain amount of dopants. Models developed for undoped silicon body are difficult to extend for moderately/heavily doped cases due to increased complexities in the Poisson's equation. Keeping this in mind, we have adopted a charge based drain current model [34] to analyze the performance parameters of GAA MOSFET based circuits. The model is valid for a wide range of doping concentration. Based on the inversion charge solution of Poisson's equation and integrating the current continuity equation, the drain current expression of a GAA MOSFET, including the drift and diffusion current components, can be generalized as  $I_{ds} = (\mu \pi d_{eff}/L)[f(Q_D)-f(Q_S)]$  with  $f(Q_{inv}) = (-1/2)$  $(\beta^2/C_{ox}^2)Q_{inv}^2 - (2\beta/C_{ox})Q_{inv} + (1/H)\ln(1 + (H\beta/C_{ox})Q_{inv})$ , where  $\mu$ , Land  $Q_{inv}$  are the mobility of the charge carriers under consideration, channel length of the GAA structure and inversion charge density per unit area respectively.  $Q_D$  and  $Q_S$  represent the  $Q_{inv}$ corresponding to the quasi-Fermi potential in the drain and source terminals. H is a parameter which reflects the geometry and doping concentration. This factor has to be modified to cover different operating modes such as weak, moderate and strong inversion [34]. In the linear region, above threshold,  $V_{t}$   $^{\prime\prime}$   $V_{gs} - V_{ds}$ ,  $(\beta/C_{ox})Q_S \gg 1$  and  $(\beta/C_{ox})Q_D \gg 1$ . In such a case  $f(Q_{inv})$  is dominated by the first term and the drain current of a coaxially gated nchannel GAA MOSFET now takes the form [34]

$$I_{DLin} \approx \frac{\mu(\pi d_{eff})}{L} C_{ox} \left[ V_{gs} - V_{th} - \frac{V_{ds}}{2} \right] V_{ds}$$

(6)

The saturated region occurs when  $V_{gs}$ – $V_{ds}$ « $V_{t}$ « $V_{gs}$ ,  $(\beta/C_{ox})Q_{S} \gg 1$  and  $(\beta/C_{ox})Q_{D}$ «1. Hence the first term of  $f(Q_{inv})$  dominates at the channel near the source while the channel near the drain is in

### Download English Version:

# https://daneshyari.com/en/article/10365317

Download Persian Version:

https://daneshyari.com/article/10365317

<u>Daneshyari.com</u>