SYNTKETIC METALS

Synthetic Metals 148 (2005) 87-91

www.elsevier.com/locate/synmet

# Towards all-polymer field-effect transistors with solution processable materials

Tomas G. Bäcklund<sup>a,\*</sup>, Henrik G.O. Sandberg<sup>a,b</sup>, Ronald Österbacka<sup>a</sup>, Henrik Stubb<sup>a</sup>, Tapio Mäkelä<sup>c</sup>, Salme Jussila<sup>c</sup>

<sup>a</sup> Department of Physics, Åbo Akademi University, Porthansgatan 3, FIN-20500 Turku, Finland

<sup>b</sup> Graduate School of Material Research, Turku Universities, Turku, Finland

<sup>c</sup> VTT Information Technology/Microelectronics, P.O. Box 1208, FIN-02044 VTT, Finland

Received 14 June 2004; accepted 20 August 2004 Available online 1 October 2004

#### Abstract

We have fabricated polymer field-effect transistors (FET) from solution processable polymers. Starting with an inorganic structure using only an organic semiconductor (regio-regular poly(3-hexylthiophene)), the transistor performance was studied as the inorganic materials were replaced with polymeric alternatives one at a time. We see a gradual increase in subthreshold swing and off-currents and an increased threshold voltage when substituting the inorganic materials with polymer materials. The small reduction in transistor performance when going from inorganic substrate and insulator to polymeric materials indicates that it is possible to make flexible polymer devices from solution processed materials suitable for roll-to-roll processing. The all-polymer FET was realized using two different conducting polymers, polyaniline for the source and drain electrodes and poly(3,4-ethylenedioxythiophene) poly(styrenesulfonate), PEDOT:PSS, for the gate electrode.

© 2004 Elsevier B.V. All rights reserved.

Keywords: Field-effect transistor; Organic; Solution process; Polymer insulator; All-polymer

#### 1. Introduction

There has been fast progress in the field of organic field-effect transistors (FETs) and applications such as integrated circuits and organic transistor controlled light emitting diodes have been presented [1,2]. As the organic semiconductor materials are improved, the interest in making all-organic electronic components is growing. Often the FET device is prepared using inorganic substrates [2,3] and electrodes, although its final use is envisioned in all-organic applications. It is thus of interest to know how various organic materials influence and possibly improve or degrade the transistor performance [4]. From the manufacturing point of view it is desirable to use solution processable polymers as it broadens the processing possibilities into printing and roll-to-

roll processing, which facilitates really low-cost fabrication [5].

All-polymer FETs have been presented before, e.g. Gelinck et al. [6] presented an organic FET with solution processable polymers having an on/off ratio of 10<sup>3</sup> and an active layer with mobility 0.01 cm<sup>2</sup>/Vs. Sirringhaus et al. [1] have presented ink-jet printed circuits incorporating transistors with an on/off ratio of 10<sup>5</sup> and charge carrier mobility of 0.02 cm<sup>2</sup>/Vs for the active material F8T2. Halik et al. [7] presented solution processable FETs utilizing regioregular poly(3-hexylthiophene) (RR-P3HT) with a mobility of 0.002 cm<sup>2</sup>/Vs, threshold voltage of +30 V, and on/off ratio of  $10^2$ . These are some examples of all-polymer FET devices presented earlier, however, in these papers the performance of the FET was only presented for the final all-polymer device. We have substituted inorganic materials one by one with polymeric materials, starting from a hybrid device where only the semiconductor is a conjugated polymer, ending up with

<sup>\*</sup> Corresponding author. Fax: +358 2 215 4776. E-mail address: tomas.backlund@abo.fi (T.G. Bäcklund).

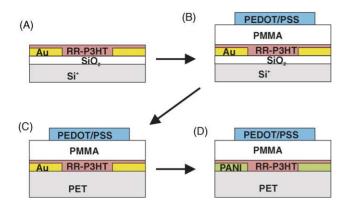

Fig. 1. Device A was fabricated with only an organic semiconductor and B is the same as A with an additional organic insulator layer and a gate electrode on top. Device C is similar to B, with the silicon substrate replaced with a PET film. The all-polymer device D is of the same device structure as C, using PANI as the source and drain electrode material.

a solution processable all-polymer FET. In this report we present device characteristics compared as a function of each transition step towards an all-polymer FET.

The fabrication of solution processable organic FETs is demanding, and it is important that the different solvents and materials are compatible so that the various layers in the FET structure do not dissolve, mix or crack during device fabrication. In this work, we have used the more conductive polyaniline for the source—drain electrodes and PEDOT:PSS for the gate electrode. Furthermore, the adhesion between the layers must be good enough so that the films do not delaminate upon drying or under mechanical stress. The interfaces formed between different polymer layers during fabrication are of crucial importance for the FET device performance, e.g. the transistor channel is formed in a layer only a few nanometers thick at the insulator interface [8].

In this work, the goal was to obtain working devices for each new material brought into the structure and to monitor the effect of the new material on device performance. A simplified picture of the structure and materials used in the different fabrication steps is seen in Fig. 1. The performance of the solution processed all-polymer FETs are comparable with the best all-polymer FETs reported for the RR-P3HT material, with an on/off ratio of  $10^4$  and a threshold voltage of +40 V and a mobility of  $0.0035\,\mathrm{cm}^2/\mathrm{Vs}$  for the active material. The source and drain electrodes were solution processed conducting polyaniline (PANI) patterned by a standard photolithography process [9]. The processing and performance of the polymer FETs have not yet been optimized for high performance.

#### 2. Experimental

The standard organic field-effect transistor (OFET) structure is an inorganic substrate with an inorganic insulator using metal source—drain electrodes. In this study the starting point was a doped silicon substrate with a 300 nm silicon

dioxide layer and patterned gold source and drain electrodes. The silicon dioxide surface was treated with hexamethyldisilazane (HMDS) to modify the surface energy, and the contact angle on HMDS treated silicon dioxide was larger than 90°. It has been shown that the HMDS treatment improves the insulator–semiconductor interface leading to higher field-effect mobility and also improved device stability [10,11].

The performance of device A serves as a reference to the performance of the devices using polymer insulators, substrates and electrodes. Device B uses the inorganic doped silicon with silicon dioxide (Si<sup>+</sup>/SiO<sub>2</sub>) as substrate, with the FET employing an organic insulator, poly(methyl methacrylate) (PMMA), and a gate of poly(3,4-ethylenedioxythiophene) poly(styrenesulfonate) (PEDOT:PSS). The substrate material was substituted to a flexible poly(ethylene terephthalate) (PET) film for device C with vacuum evaporated gold source—drain electrodes. The source and drain electrodes of the final all-polymer FET, device D, were patterned from polyaniline films on PET substrates.

The active material, RR-P3HT, was spin-coated at 1000 rpm for devices A, B, and D but device C was spin-coated at 2000 rpm in a dry nitrogen atmosphere from a 2 mg/ml p-xylene solution, and dried at 70 °C for 20 min on a hotplate to remove residual solvent from the film. The organic insulator, PMMA, was spin cast at 2000 rpm in a dry nitrogen atmosphere from a 50 mg/ml ethyl acetate solution and dried on a hotplate at 70 °C for 20 min. Both the RR-P3HT and the PMMA solutions were filtered with a 0.2  $\mu$ m filter after dissolving the material.

Devices A and C have gold source and drain electrodes vacuum evaporated using a shadow mask to define the transistor channel. Device B has predefined interdigitated gold source—drain electrodes on a doped silicon substrate with SiO<sub>2</sub> insulator. The organic gate electrode was made with top gate geometry in air from a water dispersion of PEDOT:PSS, after the surface of PMMA was briefly treated with oxygen plasma to make it hydrophilic. Devices were reintroduced into the nitrogen atmosphere after fabricating the gate electrode, and further annealed in order to remove the moisture from the structure after which the device was measured.

UV lithography process parameters are:

- 1. Spin coating electrically conducting PANI (3000 rpm) and curing of the spin-coated PANI films at 120 °C for 15 min.

- 2. Spin coating the adhesion promoter HMDS (1500 rpm, 35 s) and spin-coating the positive photoresist (AZ5214E) layer (4000 rpm, 35 s) and curing of the resist (90 °C, 20 min).

- 3. Exposure with UV light through the shadow mask (275 W, 13 s).

- 4. Development (AZ351 mixed 1:3 deionized water) of the resist (45 s at room temperature).

- 5. Etching the deprotonated PANI (reactive ion etching (RIE) 30 s, O<sub>2</sub>).

- 6. Removal of resist by flushing with isopropanol and water.

### Download English Version:

## https://daneshyari.com/en/article/10618978

Download Persian Version:

https://daneshyari.com/article/10618978

Daneshyari.com