Materials Science and Engineering B 147 (2008) 239-244

www.elsevier.com/locate/mseb

# A neural approach to study the scaling capability of the undoped Double-Gate and cylindrical Gate All Around MOSFETs

F. Djeffal<sup>a,\*</sup>, M.A. Abdi<sup>a</sup>, Z. Dibi<sup>a</sup>, M. Chahdi<sup>b</sup>, A. Benhaya<sup>a</sup>

<sup>a</sup> LEA, Department of Electronics, University of Batna, Algeria <sup>b</sup> LEPCM, Department of Physics, University of Batna, Algeria

Received 12 June 2007; received in revised form 19 July 2007; accepted 31 August 2007

#### Abstract

The Double-Gate and Gate All Around MOSFETs are two of the most promising candidates for the scaling of CMOS technology down to nanometer range. The excellent electrostatic control of the channel by the gate reduces dramatically short channel effects, such as charge sharing and DIBL. So, the objective of this work is to investigate and compare the scaling capability of the undoped DG and GAA MOSFETs using the artificial neural networks (ANNs). The optimization of this latter is based on the development of numerical models of subthreshold swing (*S*) for short channel Double-Gate and Gate All Around MOSFETs under various modes of operation based on a two-dimensional analysis of electrostatics in the channel region by solving the two-dimensional Poisson equation with the mobile charge term included, and apply the physical insights gained from these models to investigate the impact of process variations on device characteristics. This study leads to the conclusion that cylindrical geometry is superior to the equivalent Double-Gate structure both in terms of the electrostatic control of the channel and the current ratio  $I_{on}/I_{off}$ , indicating that the subthreshold slope is better controlled by the GAA MOSFET. © 2007 Elsevier B.V. All rights reserved.

Keywords: Artificial neural network; DG MOSFET; GAA MOSFET; Subthreshold swing; Scaling capability; Graphical abacus

### 1. Introduction

Multi-gate MOS transistors are widely recognized as one of the most promising solution for meeting the roadmap requirements for ultimate nanometer scale [1]. A wide variety of multi-gate architectures, including Double-Gate (DG), Gate All Around MOSFETs (GGA), have been proposed in the recent literature [2]. The Double-Gate MOSFET architecture is a potential solution to overcome short channel effects (SCE) in the 65-nm International Technology Roadmap for Semiconductors (ITRS) node [1,2]. The advantages advocated for DG MOS-FETs include: ideal subthreshold slope; volume inversion [3] (for symmetric DG); setting of threshold voltage by the gate work function thus avoiding dopants and associated number fluctuation effects; etc. There are two main types of DG MOSFETs: (1) a symmetric type with both gates of identical work functions so that the two surface channels turn on at the same gate voltage and (2) an asymmetric type with different work functions for

$0921{\text -}5107/\$$  – see front matter @ 2007 Elsevier B.V. All rights reserved. doi:10.1016/j.mseb.2007.08.034

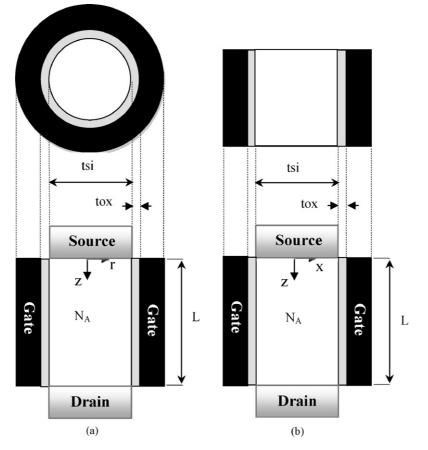

the gates and only one channel turns on at the threshold voltage [4]. The Gate All Around MOSFETs in which the gate oxide and the gate electrodes wrap around the channel region exhibit excellent transconductance and short channel behaviour because the strong confinement of the electric field from the Gate All Around the channel [5]. This device is particularly beneficial when it is used as a switching device in arrayed structures such as high-density dynamic random access memory (DRAM) and static random memory (SRAM) cells where a small device geometry and low leakage current are essential [6]. If the design parameters of GAA MOSFETs are optimized, it is expected that the short channel effects are adequately suppressed. Schematic representations of different multi-gate architectures are shown in Fig. 1.

Basing on the importance of these both architectures, in this paper we investigate the fully-depleted DG and GAA MOS-FETs at miniaturization limits compatible with the 45 nm ITRS node and, in doing so, we tackle the coupled Boltzmann–Poisson equations within both a 2D box and a cylindrical domain. More specifically, we solve a 2D Poisson equation coupled with as many Boltzmann equations as the number of mesh points within the domain of modelling. Assuming a concept of effective conducting path [7], the numerical model explains the dependence

<sup>\*</sup> Corresponding author. Tel.: +213 73796503; fax: +213 33 924540. *E-mail address:* faycaldzdz@hotmail.com (F. Djeffal).

Fig. 1. Cross sections structures and coordinates. (a) Gate All Around and (b) Double-Gate structures are shown. Uniform channel doping and metal-like source/drain regions are used in all simulations.

of subthreshold swing (*S*) according to the doping of the channel and the effect of the various electrical and geometrical parameters. The database used for the optimization of the neural network is built based on a numerical model of the subthreshold swing (*S*) developed using the finite elements method (FEM). ANN structure obtained from this optimization will be used to study the scaling capability of both architectures DG and GAA MOS-FETs.

## 2. Modelling mythology

#### 2.1. Numerical computations

Refer to Fig. 1 by accounting for the angular symmetry of the GAA MOSFET, the Poisson equations for potential  $\phi$  in the above structures take the form

DG structure :  $\frac{\partial^2 \phi}{\partial x^2} + \frac{\partial^2 \phi}{\partial z^2} = \frac{q(N_A + n(x, z))}{\varepsilon}$  (1)

GAA structure :

$$\frac{1}{r}\frac{\partial}{\partial r}\left(r\frac{\partial\phi}{\partial r}\right) + \frac{\partial^2\phi}{\partial z^2} = \frac{q(N_A + n(r, z))}{\varepsilon}$$

(2)

where the electrostatic potential  $\phi$  is referenced to the Fermi level. The free electron concentration *n* follows the classic Boltzmann distribution as  $n = n_i e^{(\phi - \phi_F)/V_T}$  where  $V_T$  is the thermal voltage (*KT*/*q*),  $n_i$  represents the intrinsic electron concentration and  $\phi_F$  is the difference between the Fermi level and the electron quasi-Fermi level to account for the non-equilibrium condition, satisfying the following boundary conditions for both cases (DG and GAA):

DG structure:

$$\phi_{\rm F}(0,x) = 0 \tag{3a}$$

$$\phi_{\rm F}(L,x) = V_{\rm DS} \tag{3b}$$

GAA structure:

$$\phi_{\rm F}(0,r) = 0 \tag{4a}$$

$$\phi_{\rm F}(L,r) = V_{\rm DS} \tag{4b}$$

$V_{\rm DS}$  being the drain voltage.

The boundary conditions for  $\phi$  are found by satisfying the continuity of both the potential and the normal component of the electric displacement at the Si/SiO<sub>2</sub> interfaces; and continuity of the potential at the source/drain sides:

DG structure:

$$\varepsilon_{\rm ox} \frac{V_{\rm Feff} - \phi(z, t_{\rm Si/2})}{t_{\rm ox}} = \varepsilon_{\rm Si} \frac{\partial \phi(z, x)}{\partial x} | x = t_{\rm Si/2}$$

(5a)

$$\varepsilon_{\rm ox} \frac{V_{\rm Beff} - \phi(z, t_{-\rm Si/2})}{t_{\rm ox}} = \varepsilon_{\rm Si} \frac{\partial \phi(z, x)}{\partial x} | x = t_{-\rm Si/2}$$

(5b)

Download English Version:

https://daneshyari.com/en/article/1531359

Download Persian Version:

https://daneshyari.com/article/1531359

Daneshyari.com