ELSEVIER

Contents lists available at ScienceDirect

# Thin Solid Films

journal homepage: www.elsevier.com/locate/tsf

# Self-forming barrier layer from CuMnTi alloy layer on SiO<sub>2</sub> substrate

## Jinlong Li \*, Hongbo Li, Feng Huang

Key Laboratory of Marine Materials and Related Technologies, Zhejiang Key Laboratory of Marine Materials and Protection Technologies, Ningbo Institute of Materials Technology and Engineering, Chinese Academy of Sciences, Ningbo 315201, China

#### ARTICLE INFO

Article history:

Received 31 January 2016

Received in revised form 24 June 2016

Accepted 24 June 2016

Available online 25 June 2016

Keywords: CuMnTi alloy Magnetron sputtering Self-forming barrier layer Electrical resistivity Mechanical property

#### ABSTRACT

Advancement of large-scale integrated interconnect structure requires an ultra-thin and uniform diffusion barrier layer between Cu interconnect and insulating layers. As a promising alternative barrier to the conventional Ta/TaN, the self-forming barrier layer from the CuMnTi alloy layer was investigated in this work. In order to achieve the self-forming barrier layer, the CuMnTi alloy layer first was deposited on SiO<sub>2</sub> substrate by magnetron sputtering. Second, the alloying elements were driven and migrated to the interface, and moreover, reacted with SiO<sub>2</sub> to form the self-forming barrier layer. The self-forming barrier layer has a thickness of about 5 nm. The annealing leads to an obvious decrease of resistivity from  $50.10\,\mu\Omega$  cm to  $4.23\,\mu\Omega$  cm for the CuMnTi alloy layer. The self-forming barrier can improve the adhesion of Cu interconnect layer and effectively prevent element diffusion between Cu interconnect and insulating SiO<sub>2</sub> substrate.

© 2016 Elsevier B.V. All rights reserved.

#### 1. Introduction

With the development of large-scale integration (LSI), the devices performance is affected mainly by the interconnect resistivity [1]. In order to decrease the resistivity of the interconnect, Cu has been employed as conducting metallic materials. In addition, various low- $\kappa$  materials have been used as insulating dielectric materials for advance LSI devices [2–4]. Since inter-diffusion occurs between Cu and insulating dielectric materials, Ta and TaN as diffusion barrier layers are deposited at the interface between Cu and dielectric materials [5]. However, as the feature size of the LSI devices decreases to 70 nm or less, the conventional Ta and TaN have difficulty in forming ultra-thin uniform barrier layer on the walls of trenches and vias [6].

The diffusion barrier layer has been recognized as a promising method to prevent the element migration [7–10]. For the conducting materials in LSI device, the alloy elements were incorporated into Cu material and the elements can migrate to the interface with insulating dielectric material, and self-form the diffusion barrier layer by annealing. Among alloying elements investigated, Mn was found to be a very promising candidate due to its higher diffusivity and large activity coefficient in Cu [9]. In addition, the self-formed barrier (SFB) layer has excellent resistance to electro-migration and stress-induced failure [10–12]. Another very attractive element is Ti, which has a small solubility limit in Cu (<0.5 at.% at 500 °C), small increment of resistivity in Cu

metallization (5  $\mu\Omega$  cm/at.% Ti), relatively high reactivity with the low- $\kappa$  materials [13–18]. Although many researchers have reported the information on the SFB layer from CuMn layers, but there has been lack of work on the SFB layer from Cu interconnect incorporated with both Mn and Ti alloy elements. The titanium element may affect the formation of SFB layer from CuMn alloy and improve the adhesion of Cu interconnect layer.

In this paper, the SFB layer was fabricated from the CuMnTi alloy layer by magnetron sputtering and followed annealing. In addition, the structure, resistivity and mechanical properties have been investigated for the CuMnTi alloy layer before and after annealing.

### 2. Experimental details

The SiO $_2$  layer with a thickness of 500 nm was deposited on p-type Si (100) wafer by thermal oxidation. Before deposition, the surface of the SiO $_2$  layer was cleaned by argon ion sputtering with negative bias of 400 V for 5 min. The CuMnTi alloy layer was fabricated on SiO $_2$  substrates with a thickness of 150 nm by magnetron sputtering with CuMn (8 at.% Mn) target and Ti (purity of 99.9%) target. The chamber was pumped to a base pressure of 5  $\times$  10 $^{-6}$  Pa. The working pressure was fixed at 0.6 Pa during sputtering. The CuMn target power is 50 W and Ti target power is 15 W. The deposition temperature is 200 °C and deposition time is 10 min. Annealing was performed at 450 °C in gases of Ar + 3% H $_2$  for 0.5 h.

Cross-sectional images of the annealed sample were observed by a JEOL2100 transmission electron microscope (TEM) with a working voltage of 200 kV. The chemical composition was measured using an X-ray

<sup>\*</sup> Corresponding author. E-mail address: lijl@nimte.ac.cn (J. Li).

energy-dispersive spectrometer (EDS) attached to TEM facility. The TEM samples were prepared by grinding to  $<80~\mu m$  from cross-section of the CuMnTi alloy layer, and then thinning by argon ion. Element depth profile were measured by X-ray photoelectron spectroscopy (XPS) with a type of AXIS ULTRA DLD, and working function was calibrated using a silver specimen and the Ag 3d peak positioned at 368.25 eV. The XPS depth profiles were obtained by sputtering with Ar $^+$  ion beam of 3 kV and 30  $\mu A/cm^2$ , and the sputtering rate is 3 nm/min.

Hardness and scratch test were carried out by MTS G200 nanoindentation system. The hardness was obtained using the Oliver-Pharr method with the continuous stiffness measurement option, and 12 indentations in each sample configured on different areas were performed to have reliable statistics. For the hardness test, allowable drift rate is <0.1 nm/s, poisons ratio is 0.25 and Berkovich tip was employed. However, the

scratch test was performed using the Cube Corner tip. The scratch involves three steps, i.e. the pre-scan, scratch-scan and post-scan. The scratch begins the ramp-load process from 20 µN to 10 mN for 200 µm.

#### 3. Results and discussions

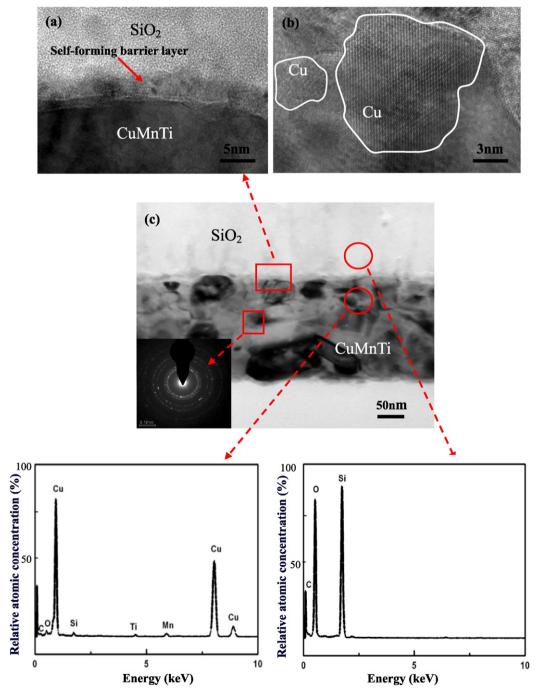

Fig. 1 shows the cross-section TEM image for the CuMnTi alloy layer after annealing. The as deposited CuMnTi layer has the characteristics of multi crystalline structure, and this can be identified by diffraction ring feature from the insert of Fig. 1c, moreover, the clear Cu crystal lattice can be observed from Fig. 1b. In the as-deposited CuMnTi alloy layer, the element contents are 88.8 at.% Cu, 6.1 at.% Mn and 5.1 at.% Ti by XPS analysis. The elements of Ti and Mn were supersaturated in the CuMnTi alloy layer. The TEM image clearly reveals the formation of

Fig. 1. Cross-section TEM image and EDS spectra for CuMnTi alloy layer after annealing in Ar +3% H<sub>2</sub> at 450 °C for 30 min.

# Download English Version:

# https://daneshyari.com/en/article/1663853

Download Persian Version:

https://daneshyari.com/article/1663853

<u>Daneshyari.com</u>