FISEVIER

Contents lists available at SciVerse ScienceDirect

# Thin Solid Films

journal homepage: www.elsevier.com/locate/tsf

# Ultrathin HfON/SiO<sub>2</sub> dual tunneling layer for improving the electrical properties of metal–oxide–nitride–oxide–silicon memory

L. Liu a, J.P. Xu a,\*, J.X. Chen a, F. Ji a, X.D. Huang b, P.T. Lai b,\*

- a Department of Electronic Science & Technology, Huazhong University of Science and Technology, Wuhan 430074, People's Republic of China

- <sup>b</sup> Department of Electrical & Electronic Engineering, the University of Hong Kong, Pokfulam Road, Hong Kong

#### ARTICLE INFO

Article history:

Received 14 August 2011

Received in revised form 29 September 2012

Accepted 9 October 2012

Available online 30 October 2012

Keywords: MONOS memory High-k gate stack Charge storage layer Tunneling layer Blocking layer

#### ABSTRACT

A high-k gate stack structure with ultrathin  $HfON/SiO_2$  as dual tunneling layer (DTL), AlN as charge storage layer (CSL) and HfAlO as blocking layer (BL) is proposed to make a charge-trapping-type metal-oxide-nitride-oxide-silicon non-volatile memory device by employing in-situ sputtering method. The validity of the structure is examined and confirmed by transmission electron microscopy. The memory window, program/erase, endurance and retention properties are investigated and compared with similar gate stack structure with  $Si_3N_4/SiO_2$  as DTL,  $HfO_2$  as CSL and  $Si_2N_3$  as BL. Results show that a large memory window of  $Si_2N_3$  as a program/erase (P/E) voltage of  $Si_2N_3$  as BL. Results show that a large memory window of  $Si_2N_3$  as a program/erase (P/E) voltage of  $Si_2N_3$  as BL. Results show that a large memory window of  $Si_2N_3$  as BL. Results show that a large memory window of  $Si_2N_3$  as BL. Results show that a large memory window of  $Si_2N_3$  as BL. Results show that a large memory window of  $Si_2N_3$  as BL. Results show that a large memory window of  $Si_2N_3$  as BL. Results show that a large memory window of  $Si_2N_3$  as BL. Results show that a large memory window of  $Si_2N_3$  as BL. Results show that a large memory window of  $Si_2N_3$  as BL. Results show that a large memory window of  $Si_2N_3$  as BL. Results show that a large memory window of  $Si_2N_3$  as BL. Results show that a large memory window of  $Si_2N_3$  as BL. Results show that a large memory window of  $Si_2N_3$  as BL. Results show that a large memory window of  $Si_2N_3$  as BL. Results show that a large memory window of  $Si_2N_3$  as BL. Results show that a large memory window of  $Si_2N_3$  as BL. Results show that a large memory window of  $Si_2N_3$  as BL. Results show that a large memory window of  $Si_2N_3$  as BL. Results show that a large memory window of  $Si_2N_3$  as BL. Results show that a large memory window of  $Si_2N_3$  as BL. Results show that a large memory window of  $Si_2N_3$  as BL. Results show that a large memory window

© 2012 Published by Elsevier B.V.

## 1. Introduction

The challenges for non-volatile memory devices are to achieve high program/erase (P/E) speed at low operating voltage, large memory window and good 10-year data retention simultaneously [1]. Because of the advantages in scaling, simple fabrication process and robustness against defect-related leakage, metal-oxide-nitrideoxide-silicon (MONOS) memory devices become attractive candidates [2]. Extensive researches have been performed in recent years, involving the use of high-k HfO<sub>2</sub> [2,3] or AlN [1,4,5] as charge storage layer (CSL), the use of Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> [2] or ZrO<sub>2</sub>/SiO<sub>2</sub> [6] as dual tunneling layer (DTL) to enhance the tunneling current, the use of Al<sub>2</sub>O<sub>3</sub> instead of SiO<sub>2</sub> as the blocking layer (BL) [7,8] and the use of highwork-function metal gate [9,10] for suppressing electron injection from gate electrode. Bandgap-engineered MONOS with dual tunneling layer can offer a compromise among the improvements of memory window, program/erase speeds and retention, due to the increased conduction-band offset ( $\Delta E_C$ ) and valence-band offset ( $\Delta E_V$ ) of the high-k layer relative to SiO<sub>2</sub>. However, little work concentrated on combining the advantages of high-k BL and CSL with the band-engineered dual tunneling layer of high-k/SiO<sub>2</sub>. In this work, we propose a high-k gate stack structure - Au/HfAlO/AlN/(HfON/SiO<sub>2</sub>)/Si for MONOS memory applications which combines an ultrathin DTL of HfON/SiO2 with the high-k HfAlO BL [11,12] and AlN CSL to comprehensively improve the performances of the devices. Here, the use of HfAlO instead of Al<sub>2</sub>O<sub>3</sub> as BL is because a higher dielectric constant can be obtained due to combination of HfO<sub>2</sub> with Al<sub>2</sub>O<sub>3</sub>. As a result, a high coupling ratio under the same physical thickness can be generated due to the smaller equivalent oxide thickness (EOT), and also, the large barrier height and good thermal stability of HfAlO can be obtained by controlling the amount of Al<sub>2</sub>O<sub>3</sub> in the film at reasonable value. The electrical characteristics of the proposed device are evaluated through comparison with a similar high-k gate stack structure of Au/Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/(Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>)/Si as reported in [2], because many researchers used the Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>, HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> as DTL [13–15], CSL [2,3] and BL [16,17] respectively, demonstrating good performances and their combination could be expected as one of the promising bandgap-engineered candidates to improve the program/erase speed, memory window and charge retention characteristics. Experimental results indicate that the large memory window, high program/erase speed at low operating voltage and good retention property can be obtained by using the proposed high-k gate stack structure.

#### 2. Experiments

To improve the P/E characteristics of MONOS flash memory device, a high-k stack gate dielectric structure of Au/HfAlO/AlN/(HfON/SiO\_2)/Si is proposed, with ultrathin HfON/SiO\_2 as double tunneling layer, AlN as charge-storage layer and HfAlO as blocking layer, as shown in Table 1. These high-k dielectrics were consecutively deposited in-situ by reactive sputtering (or co-sputtering) method using Denton Vacuum Discovery Deposition System at room temperature. A 2-nm thick SiO\_2 was thermally grown in dry  $\rm O_2$  at 900 °C on

<sup>\*</sup> Corresponding authors. E-mail addresses: jpxu@mail.hust.edu.cn (J.P. Xu), laip@eee.hku.hk (P.T. Lai).

**Table 1** High-k gate dielectric stack structure.

|                      | Proposed device         | Control device          |

|----------------------|-------------------------|-------------------------|

| Gate electrode       | Au                      | Au                      |

| Blocking layer       | HfAlO (12 nm)           | $Al_2O_3$ (12 nm)       |

| Charge-storage layer | AlN (3 nm)              | $HfO_2$ (3 nm)          |

| Dual tunneling layer | HfON (2 nm)             | $Si_3N_4$ (2 nm)        |

|                      | SiO <sub>2</sub> (2 nm) | SiO <sub>2</sub> (2 nm) |

p-type Si substrate with a resistivity of 5–10  $\Omega$  cm. Then, a 2-nm HfON was deposited by reactive sputtering of HfO2 in an Ar/N2 (24:6) ambient, followed by a deposition of a 3-nm AlN by reactive sputtering of Al in an Ar/N2 (24:6) ambient, and then a deposition of a 12-nm HfAlO by reactive co-sputtering of HfO<sub>2</sub> and Al in Ar ambient. A post-deposition annealing (PDA) was carried out in N2 at 700 °C for 60 s to improve the dielectric quality. For obtaining densification and high-quality tunneling layer and especially blocking layer, their deposition rates were set at a lower value of 0.125 nm/min and 0.1 nm/min respectively. On the contrary, the charge-storage layer was deposited at a higher rate of 2 nm/min so that more deep-level traps can be formed during deposition. For comparison, a normal high-k gate stack of Au/Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/(Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>)/Si (as control sample) was prepared using the same deposition procedure, with Si<sub>3</sub>N<sub>4</sub> RF-deposited using Si<sub>3</sub>N<sub>4</sub> target at a rate of 0.1 nm/min in Ar, HfO<sub>2</sub> RF-deposited using HfO<sub>2</sub> target at a rate of 0.17 nm/min in Ar, and Al<sub>2</sub>O<sub>3</sub> RF-sputtered using Al target at a rate of 0.084 nm/min in Ar/O<sub>2</sub> (24/6) ambient. Each dielectric layer had the same physical thickness as the corresponding layer in the proposed device. For avoiding the crystallization of HfO<sub>2</sub>, the PDA was performed at a low temperature of 500 °C for 120 s in N<sub>2</sub>. Finally, highwork-function Au was evaporated and patterned as gate electrode and then Al was evaporated as back electrode, followed by forminggas annealing which was completed in H<sub>2</sub>/N<sub>2</sub> (5% H<sub>2</sub>) for 20 min at 400 °C.

To examine the physical thickness of each dielectric layer and the interface quality between adjacent dielectric layers after the fabrication processes, transmission electron microscopy (TEM, Model: FEI Tecnai G2 20 Scanning TEM, operating voltage: 200 kV) was used to take cross-sectional images. For evaluating the memory window and programming/erasing characteristics, high-frequency (1-MHz) capacitor-voltage (C-V) curves were measured using HP4284A precision LCR meter at room temperature, and the programming/erasing voltages were applied by HP4156A precision semiconductor parameter analyzer.

### 3. Results and discussion

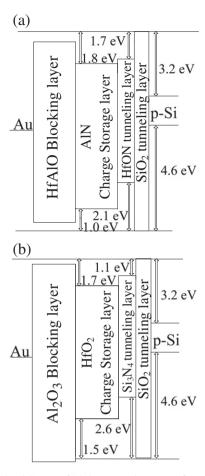

In Fig. 1(a) and (b), the schematic band diagrams of the two samples are compared. The values of the bandgap,  $\Delta E_C$  and  $\Delta E_V$  with respect to the conduction and valence bands of SiO<sub>2</sub> respectively are from Refs [11,18–20]. The  $\Delta E_C$  of HfON is larger than that of Si<sub>3</sub>N<sub>4</sub>. The barrier height of HfAlO and the electron affinity of AlN can be adjusted by changing the Hf/Al ratio and Al/N ratio respectively, making them as promising materials for application in bandgapengineered MONOS memory. For the proposed structure, the combination of AlN with high electron affinity [21] and HfAlO with appropriate Al content [12] could reach a good compromise in terms of thermal stability, dielectric constant and barrier height.

Fig. 2 shows the cross-sectional TEM image of the proposed gate stack structure. The clear interface between adjacent layers indicates that inter-diffusions between the layers can be effectively suppressed because the nitride (AlN) and oxynitride (HfON) layers located at the middle of the stacked gate dielectric can play a role of blocking impurity inter-diffusions due to nitrogen-related barrier [22,23]. From the TEM image, it can be clearly seen that the physical thickness of the

Fig. 1. Schematic band diagram of (a) the proposed structure of Au/HfAlO/AlN/(HfON/SiO<sub>2</sub>)/Si and (b) the control structure of Au/Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/(Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>)/Si.

stacked HfAlO/AlN/(HfON/SiO<sub>2</sub>) is 12.5 nm/3.2 nm/(1.7 nm/2.0 nm) (an ultrathin DTL), very close to the design values, indicating the feasibility of sputtering and anneal processing for both the proposed device and the control device.

According to the physical thickness from TEM image and the relative permittivity of each dielectric layer in the proposed sample and control sample [12,21,24], the values of accumulation capacitance could be calculated to be 38 pF and 30 pF respectively, larger than the values extracted from the measured C–V curves of the two samples (31 pF and 25 pF respectively). This could be because the k values of the deposited dielectrics are smaller than those given in the above literature, due to the amorphous state of the films and difference in elemental composition. Based on the same reduction trend of accumulation capacitance of the two samples, it is believed that the values of accumulation capacitance are basically consistent with the dielectric thicknesses.

To study the quality of the HfON/SiO $_2$  and Si $_3$ N $_4$ /SiO $_2$  dual tunneling layers, MIS capacitors with HfON/SiO $_2$  and Si $_3$ N $_4$ /SiO $_2$  as gate dielectric were also fabricated under the same processing conditions as the two samples. Fig. 3 shows the C–V curve of the MIS capacitors swept in two directions under +/-8 V sweeping voltage. Small C–V hysteresis (<50 mV) is observed, indicating almost trap-free dual tunneling layers. Moreover, the elemental percentage is determined to be 53.5% for Al and 46.4% for O in the Al $_2$ O $_3$  blocking layer by X-ray photoelectron spectroscopy, close to the stoichiometry of ideal Al $_2$ O $_3$  (52.9% for Al and 47.0% for O).

The memory window is determined from the shift of the flat-band voltage, extracted from the measured C–V curves under different P/E voltages. As can be seen from Fig. 4, the memory window of the proposed device at P/E voltages of +8 V/-10 V, +8 V/-12 V,

# Download English Version:

# https://daneshyari.com/en/article/1666588

Download Persian Version:

https://daneshyari.com/article/1666588

**Daneshyari.com**