FISHVIER

Contents lists available at ScienceDirect

## Thin Solid Films

journal homepage: www.elsevier.com/locate/tsf

# Non-aqueous solution processed ZnO thin film transistors

Gang Xiong \*, G.A.C. Jones, R. Rungsawang, D. Anderson

Semiconductor Physics Group, Cavendish Laboratory, Department of Physics, University of Cambridge, Cambridge, CB3 0HE, United Kingdom

#### ARTICLE INFO

Article history: Received 2 February 2009 Received in revised form 19 December 2009 Accepted 19 January 2010 Available online 25 January 2010

Keywords:

Zinc oxide

Thin film transistors

Solution process

Structural properties

Electrical properties and measurements

#### ABSTRACT

Zinc oxide based thin film transistors (TFT) fabricated by a non-aqueous sol-gel solution process with a zinc neodecanoate precursor are demonstrated. X-ray diffraction measurement reveals that the ZnO films adopt a hexagonal structure with a random crystal orientation. Atomic force microscope and scanning electron microscope characterizations show that the films are closely packed and consisted of particles with an average size of 45 nm. The devices exhibit an n-channel enhancement mode behavior, with saturation mobility in the range of  $0.95-1.29~{\rm cm}^2~{\rm V}^{-1}~{\rm s}^{-1}$ , drain current on-to-off ratios higher than  $10^7$  and threshold voltages between 5.3 and  $16.8~{\rm V}$  in an ambient environment. The results imply that high-performance ZnO TFTs produced by a simple and low-cost technique could be applicable to electronic devices.

© 2010 Elsevier B.V. All rights reserved.

#### 1. Introduction

Oxide semiconductor based thin film transistors (TFTs) have recently been extensively investigated for various applications, such as photo-detecting devices, biosensors, and flat panel displays, etc [1–9]. Among them, the ZnO-based TFTs are of significant interest as ZnO is a nontoxic semiconductor, and may also offer salient features such as high mobility, excellent environment stability, and high optical transparency. Great efforts are being made in investigating the fabrication and performance of ZnO-based TFTs. The fabrication methods that have been reported include radiofrequency (RF) magnetron sputtering [10–13], pulsed-laser deposition [14], and solution process, [15–18] etc. The advantages of the first two methods are generally higher mobility of the devices and lower growth temperature, while the solution process can potentially enable low-cost TFT arrays/circuits via mass-manufacturing, roll-to-roll processes using a combination of conventional coating and printing techniques.

Most of the reported solution processes are performed in an aqueous system. In a reaction system in which  $H_2O$  is present in the precursor, hydrolysis reactions may occur during the processing, which results in different types of intermediate species  $(Zn_xO_yH_z)$  and influences the ZnO film growth [19]. For processing on the glass and hydrophobic substrates, the polar nature of aqueous system can be problematic and quite often it is required to adopt complicated surface treatments during the processes. In this work, we report our approach of a non-aqueous solution process, with a zinc neodecano-

\* Corresponding author.

E-mail address: ganxiong@hotmail.com (G. Xiong).

ate precursor as the zinc source, to fabricate ZnO TFTs on glass substrates. The device fabrication processes and characterizations are all conducted in air, and the device performances are comparable to or better than those of amorphous silicon and other solution processed oxide semiconductor TFTs.

#### 2. Experimental details and discussions

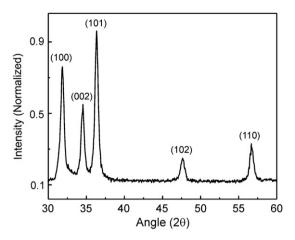

A zinc neodecanoate precursor solution is prepared by mixing 1 part by volume of 99.9% zinc neodecanoate ([CH<sub>3</sub>(CH<sub>2</sub>)<sub>5</sub>C(CH<sub>3</sub>)<sub>2</sub>COO]<sub>2</sub>Zn) with 20 parts of 99.9% toluene. The solution is then placed in an 80 °C hot water bath for 3 h to allow a uniformly mixing. The TFT devices were prepared on glass substrates which were coated with a 200 nm thick layer of sputtered indium tin oxide (ITO) and a 220 nm thick of aluminum-titanium oxide (ATO) deposited by atomic layer deposition [20]. The ITO and ATO layers act as the TFT bottom gate and gate insulator, respectively. The zinc neodecanoate precursor solution was spin-coated on the substrate at a speed of 2000 rpm for 60 s and immediately placed on a 100 °C hot plate, to allow the solvent to evaporate. This process was repeated three times to increase the film thickness. The film was then annealed in air for 1 h at 500 °C. X-ray diffraction spectra were recorded with a Philips X'Pert Pro diffractometer (Panalytical), using the copper Kα-line, at 40 kV, 40 mA in linefocus mode. The diffractometer was set up with the PW3050/65 goniometer, and the data were collected from  $2\theta = 30^{\circ}$  to  $80^{\circ}$  with a step size of 0.05° and a scan rate of 1° per minute. Experiments were run under atmospheric conditions at room temperature. The result shows that the ZnO film adopts a hexagonal structure with lattice parameters a=3.26 and c=5.19 Å (Fig. 1). It can be seen in Fig. 1 that crystal orientations are random in the film as distinct peaks of the (100), (002),

Fig. 1. XRD pattern of the ZnO film.

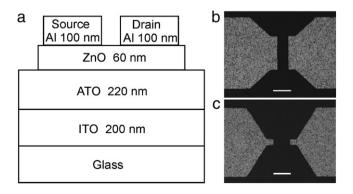

(101), (102) and (110) ZnO crystal planes were observed. Ellipsometry measurements were carried out on a Rudolph Research/Auto EL system, with an operation wavelength of 632.8 nm, using a refractive index of 1.98 for ZnO and the film thickness was assumed to be less than 500 nm. It is estimated that the film has a thickness of 60 nm. Al source and drain electrodes of 100 nm thick were then patterned on top of the ZnO film by a standard lithography process. To evaluate the performance of the TFT devices, 5 sets of devices with different channel widths (W) and channel lengths (L) were used, namely 15  $\mu$ m (W)/45  $\mu$ m (L), 25  $\mu$ m  $(W)/50 \mu m$  (L),  $50 \mu m$  (W)/50  $\mu m$  (L),  $84 \mu m$  (W)/28  $\mu m$  (L), and  $90 \, \mu m$  (W)/18  $\mu m$  (L), thus varying the W/L ratio from 1:3 to 5:1. A schematic illustration of the TFT structure is shown in Fig. 2(a). Images of devices with W/L ratios of 3:1 and 1:3 are shown in Fig. 2(b) and (c), respectively. Contact to the ITO bottom gate was achieved by scratching through the ZnO and ATO layer, evaporating a thin Al metal layer onto the scratches which is near the corner of the substrates. Device isolation was then achieved by patterning strip lines of 10 µm width between devices using focused-ion-beam (FIB) milling with a FEI-200 THP system operated at 30 kV and 150 nA beam, thus, the devices are separated and can be measured individually.

The devices were electrically characterized in air, at room temperature, and in the dark using a microprobe station connected to a semiconductor parameter analyzer (Hewlett-Packard 4156B). A persistent photoconductivity is observed, and measurements show that there is a 6% increase on the current under a white light illumination. The initial (dark current) level of the conductivity is observed after turning the light off and keeping the sample at room temperature in dark for 30–40 mins. The underlying mechanism of the persistent photoconductivity is complicated and may be attributed to a lattice relaxation process of surface states, immediately after the electrons have been photo-excited into distributed surface states

**Fig. 2.** (a) Schematic illustration of a typical ZnO-TFT structure; (b) and (c) images of two TFT devices with W/L ratios of 3:1 and 1:3, respectively. Scale bar is  $50 \,\mu m$ .

located inside the band gap of the ZnO thin film [21,22]. To accurately assess the dark current characteristics of these devices, an electrical pre-stress procedure was employed to minimize the effects of persistent photoconductivity, in which the recombination of electrons and holes are facilitated by the pre-applied gate and source-drain voltages, thus minimize the effects of persistent photoconductivity, reproducibly establish the initial state of the devices, and stabilize electrical characteristics. The useful pre-stress bias range generally depends on the zinc oxide layer thickness, active area and pre-stress time [23]. For the devices presented here, the pre-stress procedure consists of (a) applying a constant gate voltage of 60 V and sweeping the drain voltage from 0 to 70 V then back to 0 V at 5 V/min and (b) reducing the gate voltage to 0 V and again sweeping the drain voltage from 0 to 70 V then back to 0 V. The reproducibility and stability of the device characteristics were confirmed by measuring 30 devices, each one more than twenty times. Typical drain current-drain voltage ( $I_{DS}$ - $V_{\rm DS}$ ) curves of a ZnO TFT device with width-to-length ratio of 1:2 are shown in Fig. 3(a). It is observed that the ZnO TFT operates as an nchannel enhancement mode device, because a positive gate voltage is required to induce a conducting channel, and that the channel conductivity increases with increasing positive gate bias. Enhancement mode is preferable to depletion mode behavior, as it is not necessary to apply a gate voltage to switch off the transistor, the circuit design is simpler, and power dissipation is lower. The device exhibits 'hard saturation', as evidenced by the fact that the slope of each  $I_{DS}$  curve is flat for large  $V_{DS}$  as a result of pinch-off of the accumulation layer. Hard saturation indicates that the entire thickness of the ZnO channel can be depleted of free electrons, which is highly desirable for most circuit applications, as transistors exhibiting this property possess a large output impedance.

TFT dc transfer characteristics  $[\log(I_{DS})-V_{GS}]$  and gate leakage current  $[\log(|I_G|)-V_{GS}]$ , from the same device, are shown in Fig. 3(b). The saturation mobility  $(\mu_{\rm sat})$  and the threshold voltage  $(V_{\rm th})$  were calculated by fitting a straight line to the plot of the square root of  $I_{\rm DS}$  vs.  $V_{\rm GS}$ , according to the expression:

$$I_{\rm DS} = \left(\frac{C_{\rm i}\mu_{\rm sat}W}{2L}\right) (V_{\rm GS} - V_{\rm th})^2 \quad {\rm for} \ V_{\rm DS} \ >> \ V_{\rm GS} - V_{\rm th}, \eqno(1)$$

where  $C_i$  is the capacitance per unit area of the gate insulator. The obtained  $\mu_{sat}$  is 1.16 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, and an on-to-off ratio of 8.2×10<sup>7</sup> is achieved. These are important features of a TFT device—in the activematrix liquid-crystal display (AMLCD) selective transistor application, for example, a saturation mobility of at least 1 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and an onto-off ratio of greater than  $10^6$  are essential [1,10]. Fig. 3(c) is the saturation mobility statistical distribution measured from our devices. It can be seen that among the 30 devices, the saturation mobility is in the range of 0.95 to  $1.29 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , with a normal distribution centred at  $1.1 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ . The saturation mobility of our device is comparable to or better than that of most of the other solution processed ZnO TFT devices, which are typically in the range of 0.2- $0.7 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  [15–18]. Recently there are a couple of reports on improving the channel mobility for some solution processed ZnO TFTs by adjusting the process parameters: one by varying the concentration of the precursor solution and heat profile, in which a mobility of 7.2 cm $^2$  V $^{-1}$  s $^{-1}$  is reported [24]; the other one by using a less stable, more difficult to deposit source-drain metal in which a mobility of  $5.25 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  is achieved [25]. These processes however obtain relatively low on-to-off ratios, 70 and 1.6×10<sup>5</sup>, respectively. RF magnetron sputtering fabricated ZnO TFTs were reported to achieve mobility higher than  $20 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , with on-to-off ratio of  $2 \times 10^5$ [11]. The relative lower mobility of solution processed ZnO TFTs is likely arise from different crystal orientations, a poorer crystallinity, film porosity or more pronounced grain boundary scattering and defects scattering. For example, it is believed that for efficient charge transport in ZnO TFTs along the semiconductor channel length, the

### Download English Version:

# https://daneshyari.com/en/article/1670498

Download Persian Version:

https://daneshyari.com/article/1670498

<u>Daneshyari.com</u>