FISEVIER

Contents lists available at ScienceDirect

## Thin Solid Films

journal homepage: www.elsevier.com/locate/tsf

# Charge trapping characteristics in high-k gate dielectrics on germanium

C. Mahata <sup>a,\*</sup>, M.K. Bera <sup>b</sup>, P.K. Bose <sup>c</sup>, C.K. Maiti <sup>a</sup>

- <sup>a</sup> Department of Electronics and ECE, Indian Institute of Technology Kharagpur, India

- <sup>b</sup> Department of Electronic Engineering, City University of Hong Kong, Hong Kong

- <sup>c</sup> Mechanical Engineering Departments, Jadavpur University, Jadavpur, Kolkata 700032, India

#### ARTICLE INFO

Available online 17 August 2008

Keywords: High-k gate dielectric Ge Charge trapping

#### ABSTRACT

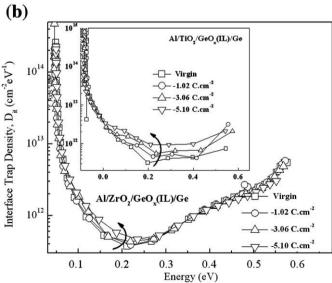

The results of a comparative study on the charge trapping/detrapping behavior in thin ZrO<sub>2</sub> and TiO<sub>2</sub> high-k gate dielectrics on p-Ge (100) under stressing in constant current (CCS, 1.02–5.1 C cm<sup>-2</sup>) and voltage (CVS, -5 V to -7 V) at gate injection mode are presented. Stoichiometric thin films of ZrO<sub>2</sub> and TiO<sub>2</sub> have been deposited on p-Ge (100) using organometallic sources at relatively low temperature (<200 °C) by plasma enhanced chemical vapor deposition (PECVD) technique in a microwave (700 W, 2.45 GHz) plasma discharge at a pressure of 66.67 Pa. The effect of stressing on several important interfacial parameters, like, interface state density, fixed oxide charge, oxide charge centroids, and capture cross-section of traps etc. is reported.

© 2008 Elsevier B.V. All rights reserved.

#### 1. Introduction

The continued scaling of Si CMOS devices has led to an increased attention to high-k gate dielectrics as replacements for  $SiO_2$ , where eventually the physical thickness (<10 A) of  $SiO_2$  cannot be scaled further before gate oxide leakage becomes prohibitively large. As per the International Technology Roadmap for Semiconductors (ITRS) published in 2005, by the year 2010, the equivalent oxide thickness of 19 Å and gate leakage currents less than 7 pA/ $\mu$ m, will be required for the MOSFET devices for low standby power applications.

High-k dielectrics will be needed for high performance applications, which require very low equivalent oxide thicknesses of less than 1 nm. Much attention has been focused on various high-k dielectrics such as aluminum oxide (Al<sub>2</sub>O<sub>3</sub>), zirconium oxide (ZrO<sub>2</sub>) and hafnium oxide (HfO<sub>2</sub>) as possible replacements for SiO<sub>2</sub>, and various research groups have demonstrated high-k dielectrics scaled down to approximately  $t_{\rm eq} \sim 10~{\rm \AA}$  with gate leakage currents significantly reduced compared to conventional SiO<sub>2</sub>-based gates.

A major challenge of replacing SiO<sub>2</sub> with a high-k gate dielectric is the degraded channel mobility. Various approaches which enhance electron and hole mobilities, such as the use of strained silicon–germanium (SiGe) on Si, [1] or strained-Si on relaxed buffer SiGe layers [2] are now available. However, bulk Ge has recently received renewed attention as a possible replacement for Si in high-k CMOS devices, because of its higher electron (2.5X) and hole (4X) bulk mobility relative to that of Si allows for the prospect of improved MOSFET channel mobility, while maintaining the potential to continue aggressive device scaling.

However, many challenges remain to make high-k on Ge work, such as (i) the presence of traps and fixed charges in the film or at the

\* Corresponding author. Fax: +91 3222 255303. E-mail address: chandreswar@gmail.com (C. Mahata). interfaces, leading to significant flat-band voltage shifts and voltage bias instability; (ii) reliability issues as channel hot carriers and carriers from gate tunneling traverse the gate dielectric resulting in trap generation; and (iii) the degradation of carrier mobility of carriers in the MOSFET channel.

In this work, we have made a comparative study on the charge trapping/detrapping behavior in thin  $\rm ZrO_2$  and  $\rm TiO_2$  high-k gate dielectrics on p-Ge (100). Ultra thin layers of high-k dielectrics have been deposited using organometallic sources at a relatively low temperature (<200 °C) by plasma enhanced chemical vapor deposition (PECVD) technique in a microwave (700 W, 2.45 GHz) plasma discharge. MIS capacitors fabricated using the high-k dielectrics have electrically characterized for reliability studies under both the constant current (CCS at 1.02 C.cm $^{-2}$  to 5.10 C.cm $^{-2}$ ) and voltage (CVS at -5 V to -7 V) stressing in gate injection mode. The effect of stressing on several important interfacial parameters, like, interface state density, fixed oxide charge, and capture cross-section of traps etc. have been studied.

#### 2. Experimental

The Ge substrate (100) used was B-doped p-type wafers with a resistivity of 25–29  $\Omega$ -cm. We have used dry chemical process for Gesurface cleaning following reference [3]. Prior to loading in the deposition chamber, samples were cleaned by holding it in highly concentrated HF vapor for 10 to 15 s. High-k TiO<sub>2</sub> and ZrO<sub>2</sub> films (~14 nm) were then deposited using metallorganic compounds titanium tetrakis isopropoxide [Ti(OC<sub>3</sub>H<sub>7</sub>)<sub>4</sub>] and zirconium tetratert butoxide [Zr(OC(CH<sub>3</sub>)<sub>3</sub>)<sub>4</sub>] in a microwave (700 W, 2.45 GHz) PECVD system at 500 mTorr for 1 min. No external biasing or heating of the substrate was employed; although the plasma discharge itself raised the substrate temperature to about 150 °C. For electrical measurements, metal insulator semiconductor (MIS) capacitors were

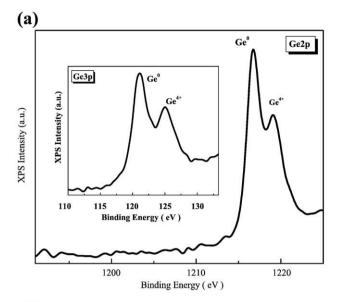

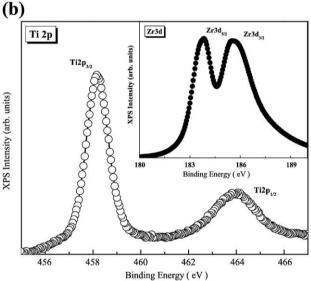

**Fig. 1.** High-resolution XPS spectra of (a) Ge 2p, Ge 3p (inset) and (b) Ti2p and Zr3d (inset) spectra of deposited  $TiO_2$  and  $ZrO_2$  films on Ge.

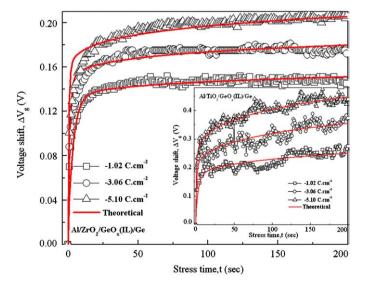

**Fig. 2.** Time dependent gate voltage shift  $(\Delta V_g)$  during CCS for  $ZrO_2/GeO_x(IL)/Ge$  structure and  $TiO_2/GeO_x(IL)/Ge$  structure (inset).

fabricated by evaporating circular Al metal dots (area: 0.196 mm², thickness: 100–200 nm) through a shadow mask. Electrical characterization was done by HP 4145B and HP 4061A semiconductor parameter analyzer.

#### 3. Result discussion

#### 3.1. Chemical characterization

The high-resolution XPS measurement used for chemical composition analysis was performed under UHV condition ( $\sim\!2\times10^{-9}$  mbar) using monochromatic Al  $K_\alpha$  source (1486.7 eV) at room temperature. All data were recorded at 45° take-off angle that is in normal emission geometry. To get the composition of the stack layers the sputter profiling of the films was accomplished using an argon ion (Ar $^+$ ) beam with energy of 3 keV. The chamber pressure was kept at  $1\times10^{-6}$  mbar during sputtering. Fig. 1(a) shows the core-level spectra of Ge 2p and Ge 3p taken after etching. From XPS spectra both metallic Ge (Ge $^0$ ) peak at 121.3 eV for 2p and 121.3 eV for 3p and fully oxidized state of

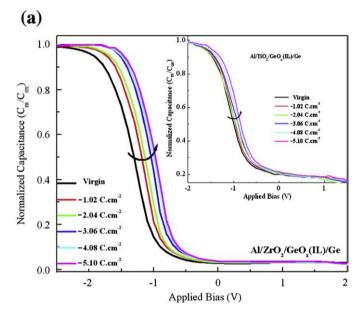

**Fig. 3.** (a) High frequency (400 kHz) normalized C–V characteristics ZrO<sub>2</sub>/GeO<sub>x</sub>(IL)/Ge structure and TiO<sub>2</sub>/GeO<sub>x</sub>(IL)/Ge MIS capacitors before and after stressing and (b) Energy distribution of density of interface states before and after stressing.

### Download English Version:

# https://daneshyari.com/en/article/1670557

Download Persian Version:

https://daneshyari.com/article/1670557

<u>Daneshyari.com</u>