EI SEVIED

Contents lists available at ScienceDirect

# Thin Solid Films

journal homepage: www.elsevier.com/locate/tsf

# Comprehensive studies on the stabilities of a-In-Ga-Zn-O based thin film transistor by constant current stress

Kenji Nomura a,\*, Toshio Kamiya a,b, Yutomo Kikuchi b, Masahiro Hirano a, Hideo Hosono a,b,c

- <sup>a</sup> ERATO-SORST, JST, in Frontier Research Center, Mailbox S2-13, Tokyo Institute of Technology, 4259 Nagatsuta, Midori-ku, Yokohama 226-8503, Japan

- b Materials and Structures Laboratory, Mail Box R3-1, Tokyo Institute of Technology, 4259 Nagatsuta, Midori-ku, Yokohama 226-8503, Japan

- <sup>c</sup> Frontier Research Center, Mail Box S2-13, Tokyo Institute of Technology, 4259, Nagatsuta, Midori-ku, Yokohama 226-8503, Japan

#### ARTICLE INFO

Available online 28 October 2009

Keywords: Amorphous oxide semiconductor a-In-Ga-Zn-O Thin film transistor Constant current stress Wet thermal annealing

#### ABSTRACT

Stability under constant current stress, along with hysteresis characteristics, was studied for a-In-Ga-Zn-O thin-film transistors (TFTs) in several atmospheres and at several temperatures. Unannealed TFTs showed rather large instability; i.e., large hysteresis in transfer curves ( $\Delta V_{\rm G} > 0.8~\rm V$ ) and large positive threshold voltage shift ( $\Delta V_{\rm th} > 10~\rm V$  for 50 h tests at 5  $\mu$ A) with deterioration of subthreshold voltage swing was observed. The instability for the unannealed TFT had a strong dependence on the stress atmosphere and the stress temperature, which suggests that trap states generated by the stress test is related to oxygen vacancy formed by breaking weak chemical bonds. Wet annealing improved stability; the hysteresis disappeared and the  $\Delta V_{\rm th}$  was reduced to <2 V. The improvement is considered to be related to the reduction of weak chemical bonds by wet annealing with the strong oxidation power of water molecules.

© 2009 Elsevier B.V. All rights reserved.

# 1. Introduction

Transparent amorphous oxide semiconductors (TAOSs) such as a-In-Ga-Zn-O (a-IGZO) are expected for channel materials of thin-film transistors (TFTs) because they exhibit better TFT characteristics than those of hydrogenated amorphous silicon (a-Si:H) and organic TFTs; e.g. a field-effect mobility exceeds  $\sim 10~{\rm cm}^2({\rm Vs})^{-1}$  and off current is easily suppressed to  $<10^{-13}$  A even fabricated at room temperature (RT) with ohmic metal contacts [1–3]. Therefore, several applications to flat-panel displays and flexible devices such as active-matrix liquid-crystal displays (AMLCD), organic light-emitting diode displays (AMOLED) and electronic papers (e-paper) have been demonstrated using a-IGZO-TFTs as a driving/switching TFT [4,5].

It is widely known that a post-thermal annealing is effective to improve not only TFT characteristics (i.e., mobility and small subthreshold voltage swing (S)), but also their stability, which would originate from the reduction of subgap defect states in a-IGZO channel layer [6]. Recently, we have reported that wet  $O_2$  annealing is more effective than dry  $O_2$  annealing to improve TFT characteristics including their uniformity [7]. Therefore, most of the a-IGZO TFTs reported to date by companies are subjected to post-thermal annealing, and these exhibit good device characteristics such as a large mobility  $> 10 \ \rm cm^2(Vs)^{-1}$ , a small S value  $\sim 0.1 \ \rm V/decade$ , and a large ON/OFF current ratio  $> 10^{10}$ , which satisfy the requirements for practical high-resolution AM-OLED and large-size AMLCD. Several

prototype displays such as 12.1" AM-OLED and 15" AMLCD have already been demonstrated using a-IGZO TFTs for driving TFTs [8,9].

To date, the focus of the development research is shifting to more practical issues such as stability and reliability of TFT characteristics. In particular, threshold voltage ( $V_{\rm th}$ ) stability under voltage/current stress is important for flat-panel display applications because driving current is changed by  $V_{\rm th}$  shifts and consequently pixel signal level/emission intensity is altered [10]. Therefore,  $V_{\rm th}$  stability against voltage/current stress for a-IGZO TFTs have been intensively studied [11–14]. Recently, we have found that the  $V_{\rm th}$  shifts induced by constant current stress have multiple origins and large  $V_{\rm th}$  shifts >10 V in unannealed a-IGZO TFTs are related to shallow subgap traps, which are annihilated by thermal annealing at 400 °C. Deep charged trap states remain even after the thermal annealing and cause small  $V_{\rm th}$  shifts less than 2 V [15].

To further understand the origin of instability in a-IGZO TFTs under current stress, it is important to investigate the stability in a wide range of conditions such as different atmospheres and temperatures, because defects such as oxygen deficiency often cause electron trapping and doping in oxide semiconductors and their formation is sensitive to an atmosphere and temperature. In this work, we have investigated stability of a-IGZO (In:Ga:Zn=1:1:1) TFT under constant current stress with several atmospheres and at different temperatures.

# 2. Experimental detail

# 2.1. TFT fabrication

All the a-IGZO (In:Ga:Zn=1:1:1) films with thickness ~40 nm were deposited on thermal SiO<sub>2</sub> (t ~150 nm)/n<sup>+</sup>-Si substrates by

<sup>\*</sup> Corresponding author. Tel.: +81 45 924 5628; fax: +81 45 924 5339. E-mail address: nomura@lucid.msl.titech.ac.jp (K. Nomura).

pulsed laser deposition with a KrF excimer laser ( $\lambda$  = 248 nm) at room temperature (RT). A sintered body of crystalline InGaZnO<sub>4</sub> was used as a target. Oxygen partial pressure during deposition was set to ~6.1–6.7 Pa. The a-IGZO channel regions were patterned by photolithography and lift-off. Then, thermal annealing was carried out at 400 °C for 1 h in dry or wet O<sub>2</sub> atmospheres (hereafter referred to as 'dry annealing' and 'wet annealing', respectively). The wet O<sub>2</sub> gas was generated through deionized water at 60 °C, which temperature corresponds to the H<sub>2</sub>O partial pressure of 19.7% [7]. Then source/drain electrode areas were defined by photolithography, and a stacked layer of Au and Ti was deposited by electron-beam evaporation at RT. The channel width (W) and length (L) were 300 and 50 µm, respectively.

## 2.2. TFT characterization

TFT characteristics were measured by a semiconductor parameter analyzer at RT in dark. Saturation mobility ( $\mu_{\rm sat}$ ) is extracted from  $I_{\rm DS} = W \mu_{\rm sat} C_{\rm OX}/2 \ L (V_{\rm GS} - V_{\rm th})^2$ , where  $I_{\rm DS}$  is drain-source current,  $V_{\rm GS}$  is gate-source voltage, and  $C_{\rm OX}$  is the gate insulator capacitance per unit area; while a S value is evaluated using  $S = (d \log I_{\rm DS}/dV_{\rm GS})^{-1} = 2.3 k_{\rm B}T/e (1 + C_{\rm sg}/C_{\rm OX})$ , where  $k_{\rm B}$  denotes the Boltzmann constant, T the temperature, e the elementary electric charge and  $C_{\rm sg}$  the equivalent capacitance contributed by the subgap states both in bulk and interfaces [16].  $V_{\rm th}$  is determined by extrapolating a straight line in a  $(I_{\rm DS})^{1/2} - V_{\rm GS}$  plot to the  $V_{\rm GS}$  axis. Constant current stress tests at a current of 5  $\mu$ A, in which the drain electrode was connected to the gate electrode, were performed in air, dry  $O_2$  and vacuum ( $\sim 10^{-1}$  Pa) atmospheres at RT. The temperature dependences of constant current stress tests were also observed in the temperature range from 25 to 110 °C in air.

### 3. Result and discussions

#### 3.1. Hysteresis characteristics and stability against ambient air

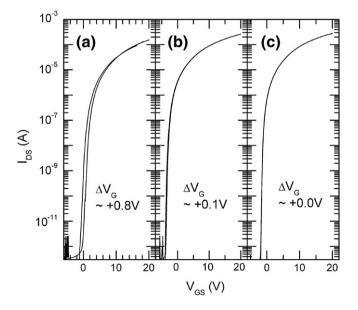

Fig. 1 shows typical transfer curves for the unannealed (a), dry annealed (b), and wet annealed (c) TFTs with the a-IGZO channels deposited at  $P_{O2}\sim6.7$  Pa. The unannealed TFTs exhibit moderately good saturation mobilities ( $\mu_{\rm sat}$ ) of  $\sim7.2$  cm<sup>2</sup>(Vs)<sup>-1</sup>, but the S value is somewhat large,  $\sim0.42$  V decade<sup>-1</sup>, which suggests that high-density electron traps exist in the unannealed a-IGZO channel and/or interface. Correspondingly, the unannealed TFTs have a relatively large clockwise hysteresis in the transfer characteristics  $\Delta V_{\rm G} \sim+0.8$  V

**Fig. 1.** Hysteresis in transfer characteristics at  $V_{DS}\!=\!10\,V$  for (a) unannealed, (b) dry annealed, and (c) wet annealed a-IGZO TFTs. The sweep rate was ~3 V/s.

(measured at a sweep rate of ~3 V/s), which is explained by trap filling by accumulated electrons. Thermal annealing improved not only TFT characteristics but also the hysteresis characteristics. For example, the dry annealed TFTs improved  $\mu_{\rm sat}$ , S and  $\Delta V_{\rm G}$  to ~9 cm<sup>2</sup> (Vs)<sup>-1</sup>, ~0.18 V decade<sup>-1</sup>, and ~+0.1 V, respectively. The wet annealed TFT exhibited further improved characteristics such as  $\mu_{\rm sat}$  ~12 cm<sup>2</sup>(Vs)<sup>-1</sup>, S ~0.11 V decade<sup>-1</sup>, and  $\Delta V_{\rm G}$  ~0.0 V. These indicate that electron traps are reduced by the thermal annealing, and the wet annealing is more effective to reduce them than the dry annealing is.

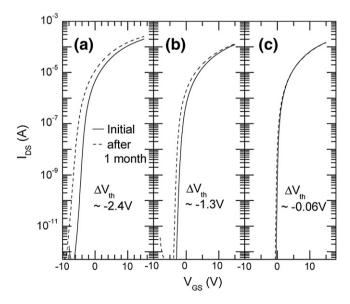

Next, we examined the influences of ambient air on the TFT characteristics such as stability of  $V_{\rm th}$ . Fig. 2 shows the transfer curves of the initial states and after keeping them in air for 1 month. All the TFTs exhibited negative  $V_{\rm th}$  shift ( $\Delta V_{\rm th}$ ). The  $\Delta V_{\rm th}$  values were as small as -0.06 V for the wet annealed TFT, while the unannealed and dry annealed TFTs exhibited large negative  $\Delta V_{\rm th}$  of  $\sim -2.4$  V and -1.3 V, respectively. It is in general known that the  $V_{\rm th}$  is largely affected by several causes such as the donor density in a semiconductor channel, and the existence of charged states in a channel/interface region, and negative  $\Delta V_{\rm th}$  is explained both by the increase in donor density and the decrease in positively-charged states.

The transfer characteristics in the unannealed TFTs also showed large deterioration in the S value from ~0.52 to ~0.66 V decade  $^{-1}$  after 1 month (Fig. 2(a)), although  $\mu_{\rm sat}$  was nearly unchanged (~8.7 to ~8.9 cm²(Vs) $^{-1}$ ). In contrast, both the dry and wet annealed TFTs exhibited no degradation in the TFT characteristic parameters after 1 month (from  $S \sim 0.23 \, \text{V} \, \text{decade}^{-1}$  and  $\mu_{\rm sat} \sim 8.6 \, \text{cm}^2 (\text{Vs})^{-1}$  to ~0.22 V decade  $^{-1}$  and ~8.3 cm²(Vs) $^{-1}$  for the dry annealed TFTs, from ~0.12 V decade  $^{-1}$  and ~11.7 cm²(Vs) $^{-1}$  to ~0.12 V decade  $^{-1}$  and ~11.9 cm²(Vs) $^{-1}$  for the wet annealed TFTs). The S value is very sensitive to subgap trap states around the Fermi level of a semiconductor channel and is deteriorated by increase in the subgap trap density [17]. Therefore, these results suggest that donor states and extra subgap trap states are formed for the unannealed TFTs even if simply placed in air at room temperature.

First-principles calculations showed that oxygen deficiency in a-IGZO plays important roles for both the electron doping and the formation of trap states, which depend on the local atomic configurations around an oxygen deficiency; i.e. an oxygen deficiency having a large free space forms both a deep occupied state and a shallow electron trap. While, if an oxygen deficiency does not have a large free space, it

**Fig. 2.** Transfer characteristics of (a) unannealed, (b) dry and (c) wet annealed a-IGZO-TFTs at initial (solid lines) and after one month (dashed lines). The devices kept in air with 40–50% of humidity at RT. The unannealed a-IGZO channels were deposited at  $P_{02}\sim6.1$  Pa.

# Download English Version:

# https://daneshyari.com/en/article/1671067

Download Persian Version:

https://daneshyari.com/article/1671067

Daneshyari.com