ELSEVIER

Contents lists available at ScienceDirect

## Solid State Electronics

journal homepage: www.elsevier.com/locate/sse

# Investigation on the variation of channel resistance and contact resistance of SiZnSnO semiconductor depending on Si contents using transmission line method

Byeong Hyeon Lee, Sangmin Han, Sang Yeol Lee\*

Department of Semiconductor Engineering, Cheongju University, Cheongju 28503, Republic of Korea

#### ARTICLE INFO

The review of this paper was arranged by Dr. Y. Kuk

Keywords: Amorphous oxide semiconductor Thin film transistor Transmission line method Resistance Si suppressor

#### ABSTRACT

Amorphous silicon-zinc-tin-oxide (a-SZTO) thin film transistors (TFTs) have been fabricated depending on the silicon ratio in channel layers. The a-SZTO TFT exhibited high electrical properties, such as high mobility of  $23~{\rm cm^2~V^{-1}~s^{-1}}$ , subthreshold swing of  $0.74~{\rm V/decade}$  and  $I_{\rm ON/OFF}$  of  $2.8\times10^8$ , despite of the addition of Si suppressor. The physical mechanism on the change of the sheet resistance and the contact resistance in a-SZTO TFT has been investigated and proposed closely related with the Si ratio. Both resistances were increased as increasing Si ratio, which clearly indicated that the role of Si is a carrier suppressor directly leading to the increase of channel and contact resistances. To explain the role of Si as a carrier suppressor, the conduction band offset mechanism has been also proposed depending on the change of carrier concentration in channel layer and at the interface between electrode and channel layer.

#### 1. Introduction

For amorphous oxide semiconductors (AOSs) based thin film transistors (TFTs) have attracted much attention for the application to integrated circuit and backplane device of active matrix display in a decade. Because they showed high electrical property, e.g. higher mobility than  $10 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , low temperature process and high transparency due to their wide bandgap > 3 eV compared with those of traditional Si-based and organic-based semiconductors [1-4]. Among them, the most extensively used materials is amorphous indium-gallium-zinc-oxide (a-IGZO) so far [5]. However, indium is an expensive and rare earth material. Therefore, it is very important to investigate indium-free materials, such as zinc-tin-oxide (ZTO) and silicon-zinc-tinoxide (SZTO), which have been studied intensively in these days [6,7]. At the same time, the instability of amorphous oxide structure has been emerged as a major to be solved. According to continuous random network mode, an amorphous structure made inter-atomic bond having SRO (short range order) similar to the crystal, but the structure of LRO (long range order) is made of an infinite three-dimensional arrangement. Existing tail state from band edge to forbidden gap in the form of an exponential is made by expanding the distribution of electronic states, due to the structural disorder of inter-atomic bond distance and the distribution of bond angle. These tail states despite relatively low density have a significant effect on electrical performance of amorphous

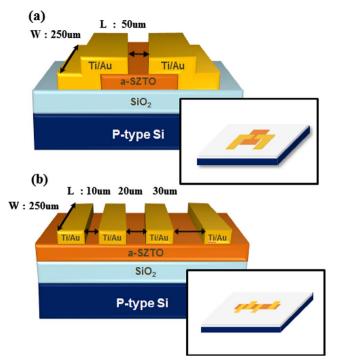

materials because the movement of carriers occurs at near band edge [8]. Defect states, such as dangling bonds which have shortage of a number of inter-atomic bond combination dissatisfied coordination number in an ideal structure also exist at deep region inside band gap. These defect states are being reported to influence the stability and the electrical property in the device [9-12]. These drawbacks should be resolved for the application of integrated circuits and backplane devices. Among the way of the improvement of device stability, suppressor materials, such as hafnium (Hf), zirconium (Zr) and gallium (Ga) have been used to control the defect states in deep level [13-16]. However, these materials are high cost and not abundant resources. For this reason, silicon has been reported as an excellent suppressor with high oxygen binding energy and abundant reserves with low cost [17-19]. In this work, we have fabricated amorphous silicon-zinc-tinoxide (a-SZTO) TFTs and extracted electrical property depending on different silicon ratio. Also, we have investigated the physical mechanism of the sheet resistance and the contact resistance using the transmission line method (TLM) model. Fig. 1(a) and (b) show a-SZTO TFT and TLM structure, respectively. For the confirmation of silicon ratio dependency of oxygen deficiency in a-SZTO channel layer, we have used X-ray photoelectron spectroscopy (XPS). In order to derive direct band diagram of SZTO thin films, we have combined the results of various measurements, such as UPS, EELS, and Kelvin Probe and derived the band diagram directly by using all the measurement results.

E-mail address: sylee@cju.ac.kr (S.Y. Lee).

<sup>\*</sup> Corresponding author.

B.H. Lee et al. Solid State Electronics 139 (2018) 15-20

Fig. 1. Schematic view of an a-SZTO (a) thin film transistor and (b) transmission line method structures.

X-ray diffraction (XRD) data of a-SZTO thin films showed amorphous structure irrespective of Si ratio as we reported before [20]. It is interesting to note that most of a-SZTO TFTs showed to maintain high electrical property, despite of the fact that device reliability has been improved by increasing the Si ratio through the stability test like bias temperature stress (BTS) [21]. Even though a-SZTO TFT shows high performance, the relationship between the Si contents and the change of channel and contact resistance has not been reported yet. In this study, we proposed the enhancement mechanism of device reliability with silicon as a suppressor using TLM by investigating the relationship between the Si contents and the change of the sheet resistance of the channel layer and the contact resistance at the interface between electrodes and channel layers.

### 2. Experimental details

The a-SZTO TFTs were fabricated by radio frequency (RF) magnetron sputtering on a  $SiO_2$  (200 nm)/p $^+$ -type Si substrate at room temperature with bottom gate structure. We have used 2" diameter a-SZTO (Zn:Sn ratio = 65:35) ceramic target with various Si ratio, such as 0, 0.1, 0.2 and 0.3 wt.% (ZTO, 0.1, 0.2 and 0.3SZTO) and deposited 40 nm

thick a-SZTO channel layer, at a working pressure of 5 mTorr and a mixed gas ambient of Ar and  $O_2$  (gas flow ratio = 48:2), by supplying RF power of 50 W. After deposition, the a-SZTO thin films were post-annealed for 2 h at 500 °C. The a-SZTO channel layers were patterned by using traditional photolithography process. The source/drain electrodes (Ti/Au = 10 nm/50 nm were deposited by e-beam/thermal evaporation sequentially without breaking the vacuum, and patterned by a lift-off process. The channel width and length are 250  $\mu m$  and 50  $\mu m$ , respectively. The fabrication process of a-SZTO TLM devices is the same as the TFT process. The TLM model on a-SZTO were patterned with various lengths of 10  $\mu m$ , 20  $\mu m$  and 30  $\mu m$  and fixed width of 250  $\mu m$ . The electrical property of a-SZTO TFTs and TLMs were measured by using a semiconductor parameter analyzer (EL 423, ELECS co.)

#### 3. Results and discussion

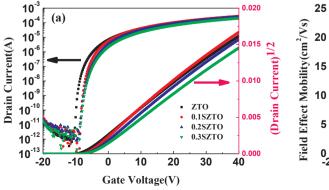

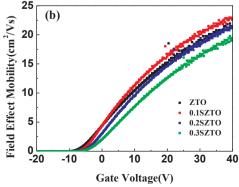

Fig. 2(a) shows the transfer curves of a-SZTO TFTs with various Si ratios of ZTO, 0.1, 0.2 and 0.3 wt.%. We extracted the electrical parameters, such as field-effect mobility ( $\mu_{FE}$ ), threshold voltage ( $V_{th}$ ), current on/off ratio ( $I_{ON/OFF}$ ) and subthreshold swing (SS) based on the measurement results of transfer characteristics, as shown in Fig. 2(b) and as summarized in Table 1. The  $\mu_{FE}$  was calculated by using the following relation [22,23]:

$$\mu_{FE} = \frac{Lg_m}{WV_{DS}C_{OX}} \tag{1}$$

where  $g_m$  is the transconductance,  $C_{ox}$  is the oxide capacitance of the gate insulator, and W and L are channel width and length, respectively. The ZTO TFT shows high electrical property compared with that of 0.1, 0.2 and 0.3SZTO TFTs. Also, we confirmed that the positive shift of V<sub>th</sub> and a little decrease of on state current. These results clearly indicate that carrier concentration has been decreased by increasing Si ratio. This change can be explained by deriving energy band diagram of various Si doped SZTO thin films. Fig. 3(a) shows ZTO and 0.3SZTO thin films band diagram of metal-insulator-semiconductor structure in equilibrium state by using work function of gate electrode (p-type Si substrate). The energy difference between the conduction band minimum and Fermi level ( $\Delta E_{CB}$ ) of ZTO and 0.3SZTO are 0.467 eV and 0.835 eV, respectively. It is well known in AOSs, the conduction band is mainly made of spherical s-orbitals of the metal cations. In addition, the wave function of heavy cations are spatially spread and make large overlaps with neighboring cations, which results in the large conduction band dispersion and small electron effective mass and reasonably high electron mobility [24]. Through the our previous work, we confirmed that the conductivity is strongly related with the electron effective mass depending on the Si ratio in the conduction band of SZTO TFTs [17]. Meanwhile, the relative position of the conduction band minimum (E<sub>CM</sub>) shifts far from the Fermi level (E<sub>F</sub>) because the shallow

Fig. 2. (a) Transfer curve of a-SZTO TFTs and (b) calculated field effect mobility ( $\mu_{FE}$ ) of a-SZTO TFTs as function of gate voltage for each Si ratio.

# Download English Version:

# https://daneshyari.com/en/article/5010163

Download Persian Version:

$\underline{https://daneshyari.com/article/5010163}$

Daneshyari.com