### ARTICLE IN PRESS

Solid-State Electronics xxx (2016) xxx-xxx

Contents lists available at ScienceDirect

# Solid-State Electronics

journal homepage: www.elsevier.com/locate/sse

# The defect-centric perspective of device and circuit reliability—From gate oxide defects to circuits

B. Kaczer <sup>a,\*</sup>, J. Franco <sup>a</sup>, P. Weckx <sup>a,1</sup>, Ph.J. Roussel <sup>a</sup>, M. Simicic <sup>a,1</sup>, V. Putcha <sup>a,1</sup>, E. Bury <sup>a,1</sup>, M. Cho <sup>a</sup>, R. Degraeve <sup>a</sup>, D. Linten <sup>a</sup>, G. Groeseneken <sup>a,1</sup>, P. Debacker <sup>a</sup>, B. Parvais <sup>a</sup>, P. Raghavan <sup>a</sup>, F. Catthoor <sup>a,1</sup>, G. Rzepa <sup>b</sup>, M. Waltl <sup>b</sup>, W. Goes <sup>b</sup>, T. Grasser <sup>b</sup>

#### ARTICLE INFO

Article history:

Available online xxxx

The review of this paper was arranged by Jurriaan Schmitz

Keywords: Variability Reliability Defects RTN BTI HCI

#### ABSTRACT

As-fabricated (time-zero) variability and mean device aging are nowadays routinely considered in circuit simulations and design. Time-dependent variability (reliability-related variability) is an emerging concern that needs to be considered in circuit design as well. This phenomenon in deeply scaled devices can be best understood within the so-called defect-centric picture in terms of an ensemble of individual defects. The properties of gate oxide defects are discussed. It is further shown how in particular the electrical properties can be used to construct time-dependent variability distributions and can be propagated up to transistor-level circuits.

© 2016 Elsevier Ltd. All rights reserved.

#### 1. Introduction

Circuit simulations

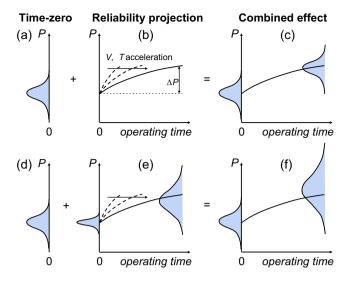

Variability of as-fabricated (i.e., time-zero) parameters of modern VLSI devices has been considered in circuit design tools for some time (Fig. 1a). With the exception of Time-Dependent Dielectric Breakdown (TDDB) [1,2], circuit lifetime estimation due to Field-Effect Transistor (FET) gate-oxide degradation (aging) mechanisms is presently based on projecting only the *mean* parameters shifts (Fig. 1b) [3]. The combination of both hitherto orthogonal efforts used in determining circuit operating margins is illustrated in Fig. 1c.

It has long been accepted that in mechanisms associated with FET gate current, such as Stress-Induced Leakage Current (SILC) and TDDB, only a handful of defects will cause significant current increases and can bridge the gate oxide, presently  $\sim 1$  nm thick. Similarly, as lateral dimensions of VLSI devices are reduced toward the 10 nm range, just a few stochastically-behaving defects present in the FET gate oxide will have a sizable impact on the *drive* current as well. These phenomena result in additional, *time-dependent*

http://dx.doi.org/10.1016/j.sse.2016.07.010

0038-1101/© 2016 Elsevier Ltd. All rights reserved.

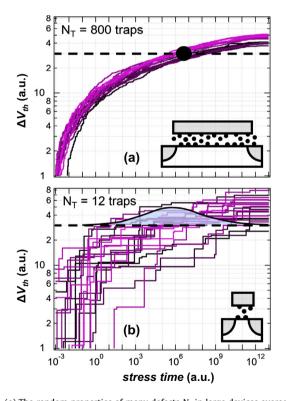

variability in deeply-scaled devices, and their manifestation in the form of Random Telegraph Noise (RTN) has been extensively studied by many groups [4–13]. Here we build upon those observations and show how the same, physics-based considerations give rise to a new, *statistical* perception of other gate-oxide degradation mechanisms, such as Bias Temperature Instability (BTI) and Hot Carrier Injection (HCI) [14–16]. This paradigm shift is illustrated in Fig. 2.

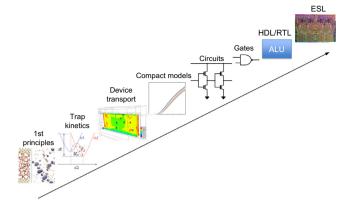

Since only a handful of defects (cf.  $N_T$  = 12 in Fig. 2b) will be responsible for the time-dependent effects in each deeply-scaled device, we maintain that understanding of degradation mechanisms at the level of individual defects is essential for simulations of time-dependent variability in circuits. This notion is indeed the basis of the so-called *defect-centric* picture and is hierarchically illustrated in Fig. 3. After defining basic variability terms, we review the properties of individual defects and show how to propagate these properties to higher hierarchical levels. We formalize the statistical description of time-dependent distributions (Fig. 1e) into simple equations and point out the parallels with time-zero variability. To estimate the full device and circuit parameter distributions at the end of useful lifetime, time-zero and time-dependent statistics have to be combined, as illustrated

a imec, Kapeldreef 75, B-3001 Leuven, Belgium

<sup>&</sup>lt;sup>b</sup> TUWien, Gusshausstrasse 27-29, A-1040 Vienna, Austria

<sup>\*</sup> Corresponding author.

E-mail address: ben.kaczer@imec.be (B. Kaczer).

<sup>&</sup>lt;sup>1</sup> Also at KU Leuven, ESAT Department, Leuven, Belgium.

B. Kaczer et al./Solid-State Electronics xxx (2016) xxx-xxx

**Fig. 1.** A schematic representation of time-zero and time-dependent effects considered in circuit design. (a–c) Presently, time-zero variability of a device parameter P is considered together with the projection of the mean parameter shift  $\Delta P$  (obtained by reliability engineers through bias and temperature accelerated tests) during aging. (d–f) Time-dependent variability is also considered, in contrast to (a–c).

**Fig. 2.** (a) The random properties of many defects  $N_T$  in large devices average out, resulting in a well-defined lifetime while (b) the stochastic nature of a handful of defects in deeply-scaled devices becomes apparent, resulting in large variation in the lifetime. This also illustrates the paradigm shift in projecting reliability in deeply scaled devices (Fig. 1b and e) [17].

in Fig. 1d-f. Finally, we discuss how the combined variability can be propagated to and simulated at the circuit level.

#### 2. Device variability

We refer to as-fabricated, time-independent, or static, device-todevice variability, as time-zero variability. Time-dependent, or

**Fig. 3.** Hierarchical levels of the defect-centric picture: Understanding of defect properties at the atomic level [18] can be propagated up to circuit design.

dynamic, variability then refers to all variability due time-dependent effects. In this work, this is limited to effects due to defects (traps) present in FET gate dielectrics. The main emphasis of this Section is developing the time-dependent variability within the defect-centric picture. This is done Section 2.2. Subsections thereof then discuss the properties of individual traps (Section 2.2.1), both temporal and electric, the statistics of multiple traps (Section 2.2.2), and the experimental methods to characterize time-dependent variability (Section 2.2.3). The complete distribution (Section 2.3) is constructed from time-dependent variability and time-zero variability, discussed next.

#### 2.1. Time-zero variability

As-fabricated, i.e., time-zero variability, both systematic (process-induced) and random, is a well-known phenomenon in deeply-scaled VLSI technologies [19,20]. For example, the time-zero threshold voltages  $V_{th0}$  are assumed to be normally-distributed with mean  $\langle V_{th0} \rangle$  and variance  $\sigma_{Vth0}^{-2}$  [21]. Disregarding edge effects, the random component of  $\sigma_{Vth0}^{-2}$  scales as

$$\sigma_{Vtho}^2 \cong \frac{A_{Vth}^2}{A_C} \tag{1}$$

where  $A_{Vth}$  is a scaling factor and  $A_G$  the total channel area [22,23]. It should be noted that some variation-inducing effects, such as Line-Edge Roughness, will result in a departure from this ideal scaling rule in deeply scaled devices [24].

A large number of nominally identical devices need to be typically measured to establish  $A_{Vth}$ , while organization of devices into matched pairs or local arrays is used to separate the systematic and the random components [25].

#### 2.2. Time-dependent variability

Similarly to time-zero variability, time-dependent variability also has random and systematic components [25–28]. Because of the limited number of gate-oxide defects  $N_T$  present in modern deeply downscaled FETs (e.g.,  $N_T$ =10 with defect density  $10^{12}$  cm<sup>-2</sup> and  $A_G$  =  $W \times L$  =  $100 \times 10$  nm<sup>2</sup>), other degradation mechanisms, such as RTN/BTI and HCI will be distributed as well [14,16,29]. Based on this simple fact we claim that the time-dependent variability in deeply scaled devices can be best understood in terms of an ensemble of individual defects and their time, voltage, and temperature dependent properties. This is indeed the underlying foundation of the defect-centric approach. To develop this approach further, we now discuss some of the relevant properties of individual defects.

## Download English Version:

# https://daneshyari.com/en/article/5010437

Download Persian Version:

https://daneshyari.com/article/5010437

<u>Daneshyari.com</u>