ELSEVIER

Contents lists available at ScienceDirect

### **Applied Surface Science**

journal homepage: www.elsevier.com/locate/apsusc

Full Length Article

# Investigation of 'surface donors' in Al<sub>2</sub>O<sub>3</sub>/AlGaN/GaN metal-oxide-semiconductor heterostructures: Correlation of electrical, structural, and chemical properties

M. Ťapajna<sup>a,\*</sup>, R. Stoklas<sup>a</sup>, D. Gregušová<sup>a</sup>, F. Gucmann<sup>a</sup>, K. Hušeková<sup>a</sup>, Š. Haščík<sup>a</sup>, K. Fröhlich<sup>a</sup>, L. Tóth<sup>b</sup>, B. Pécz<sup>b</sup>, F. Brunner<sup>c</sup>, J. Kuzmík<sup>a</sup>

- <sup>a</sup> Institute of Electrical Engineering, Slovak Academy of Sciences, Dúbravská cesta 9, 841 04 Bratislava, Slovakia

- <sup>b</sup> Institute of Technical Physics and Materials Sciences, MTA EK, Konkoly T. M. út 29-33, H-1121 Budapest, Hungary

- c Ferdinand-Braun-Institut, Leibniz Institut für Höchstfrequenztechnik, Gustav-Kirchhoff-Strasse 4, 12489 Berlin, Germany

#### ARTICLE INFO

#### Article history: Received 3 May 2017 Received in revised form 30 June 2017 Accepted 20 July 2017 Available online 26 July 2017

Keywords: AlGaN/GaN MOS-HEMT Surface donors Interface states

#### ABSTRACT

III-N surface polarization compensating charge referred here to as 'surface donors' (SD) was analyzed in  $Al_2O_3/AlGaN/GaN$  metal-oxide-semiconductor (MOS) heterojunctions using scaled oxide films grown by metal-organic chemical vapor deposition at 600 °C. We systematically investigated impact of HCl pre-treatment prior to oxide deposition and post-deposition annealing (PDA) at 700 °C. SD density was reduced down to  $1.9 \times 10^{13}$  cm<sup>-2</sup> by skipping HCl pre-treatment step as compared to  $3.3 \times 10^{13}$  cm<sup>-2</sup> for structures with HCl pre-treatment followed by PDA. The nature and origin of SD was then analyzed based on the correlation between electrical, micro-structural, and chemical properties of the  $Al_2O_3/GaN$  interfaces with different SD density ( $N_{SD}$ ). From the comparison between distributions of interface traps of MOS heterojunction with different  $N_{SD}$ , it is demonstrated that SD cannot be attributed to interface trapped charge. Instead, variation in the integrity of the  $GaO_x$  interlayer confirmed by X-ray photoelectron spectroscopy is well correlated with  $N_{SD}$ , indicating SD may be formed by border traps at the  $Al_2O_3/GaO_x$  interface.

© 2017 Elsevier B.V. All rights reserved.

#### 1. Introduction

Gallium nitride (GaN) represents one of the most attractive semiconductor materials in the fields of light emitting diodes [1,2], RF devices [3], and power electronics [4]. In particular, GaN based high electron mobility transistors (HEMTs) have been shown to provide low on-state resistance, high off-state breakdown voltage, and fast switching, making them very attractive for high-power switching applications [4–7] and mixed signal integrated circuits [8]. Enhancement-mode or normally-off switching devices are often required in applications [7]. A promising approach to process normally-off GaN HEMTs is to employ metal-oxide-semiconductor (MOS) gate structure with sufficiently high *net* negative charge at the oxide/III-N interface ( $N_{int}$ ) [8]. This has been recently demonstrated by Blaho et al. [9], where normally-off MOS-HEMTs with threshold voltage ( $V_{th}$ ) increasing from 1.2 to 3.5 V with Al<sub>2</sub>O<sub>3</sub> gate oxide thickness increasing and uncompromised output current has

\* Corresponding author. E-mail address: milan.tapajna@savba.sk (M. Ťapajna). been achieved [9]. Although a high density of negative charge is expected to be present at the III-N surface as a result of surface polarization charges ( $P_S$ ),  $N_{int}$  close to zero was reported by many authors [10–14]. Compensation of  $P_S$  at the oxide/III-N interface in GaN-based MOS heterostructures was attributed to formation of a compensating charge located at or close to the oxide/III-N interface [10–13], referred here to as 'surface donors' (SD) [15]. Although some microstructural models for SD have been proposed in the literature [11,12,16], there is yet no agreement on the exact location, microscopic origin, and nature of SD in III-N MOS heterostructures. However, such knowledge is unavoidable in order to utilize technological manipulation of SD density for  $V_{th}$  adjustment in power switching MOS-HEMTs.

In this work, we report on a simple approach for SD density  $(N_{SD})$  reduction in GaN MOS-HEMTs by skipping HCl pre-treatment of the barrier surface prior to deposition of  $Al_2O_3$  using metalorganic chemical vapor deposition (MOCVD) at  $600\,^{\circ}$ C. Further, post-deposition annealing (PDA) of  $Al_2O_3$  films performed at  $700\,^{\circ}$ C was also found to have a strong impact on  $N_{SD}$ , resulting in systematic increase in  $N_{SD}$  for both with and without HCl pre-treatment. This allowed us to correlate variations in  $N_{SD}$  with electrical,

microstructural, and chemical properties of the oxide/III-N interface, analyzed by means of interface state density distribution ( $D_{it}$ ), high-resolution transmission electron microscopy (HR-TEM), and X-ray photoelectron spectroscopy (XPS).

#### 2. Experimental details

MOS-HEMT structures studied here were fabricated on GaN-cap/Al $_{0.24}$ Ga $_{0.76}$ N/GaN heterostructures (from top 3 nm/20 nm/1.9  $\mu$ m) grown on sapphire substrate by MOCVD. After MESA etching and Ti/Al/Ni/Au Ohmic contacts processing, Al $_2$ O $_3$  gate dielectrics with thickness ( $t_{ox}$ ) of 10, 20, and 30 nm (nominal thickness) were deposited by MOCVD. Prior to Al $_2$ O $_3$  growth by MOCVD, part of the sample underwent standard cleaning step including HCl dip and DI water rinse (with HCl), while HCl cleaning step was skipped in other part of the sample (without HCl). Al $_2$ O $_3$  thin films were then grown at 600 °C using Al acetylacetonate precursor diluted in toluene and O $_2$ /Ar carrier gas mixture. Part of samples with and without HCl pre-treatment was then annealed at 700 °C for 1 h in N $_2$  (PDA). Finally, Ni/Au (40/50 nm) gates were deposited via e-beam evaporation and patterned using photolithography and lift-off process.

X-ray reflectivity (XRR) (Bruker AXS-D8 Discover equipment) was used to measure oxide thickness on Al<sub>2</sub>O<sub>3</sub> layers deposited on SiO<sub>2</sub>/Si substrates in the same run as MOS-HEMT devices. HR-TEM and XPS analyses were performed on bare samples with 10- and 2 nm thick Al<sub>2</sub>O<sub>3</sub> films, respectively, grown on nominally identical GaN/AlGaN/GaN wafers as for the respective MOS-HEMT devices. For HR-TEM study, specimens were mechanically ground and polished, followed by 7 kV Ar<sup>+</sup> ion milling until perforation. JEOL 3010 was used operating at 300 kV with point resolution of 0.17 nm. XPS signals were recorded using a Thermo Scientific K-Alpha system equipped with a micro-focused monochromatic Al Ka X-ray source (1486.6 eV) at angle of 45°. Capacitance-voltage (CV) and transient characteristics were measured on MOS-HEMT circular diodes with diameter of 80  $\mu$ m.  $D_{it}$  distribution was determined for structures with  $t_{ox}$  = 10 and 20 nm using three complementary techniques: (i) CV curve frequency dispersion at positive  $V_g$  -s ( $D_{it}$  from  $E_C$ -E = 0.3 to  $0.4\,\mathrm{eV}$ ) [17]; (ii)  $V_{th}$ -transient technique measured at temperatures of 25, 75, 125, 175, 225, and 275 °C ( $D_{it}$  from  $E_C$ -E = 0.5 to 1.3 eV), and (iii) filtered light-assisted  $V_{th}$ -transient ( $D_{it}$  from  $E_C$ -E = 1.7 to 3.0 eV) [18]. In the CV frequency dispersion technique proposed by Hori et al. [17],  $D_{it}$  is determined from the differences in positive  $V_g$ s, at which capacitance (related to interface states) increases above plateau (see Fig. 3(a)) as a function of measurement frequency. In  $V_{th}$ -transient technique exemplified in Fig. 3(b) [18], thermal emission of electrons from interface traps is monitored via device  $V_{th}$ transient shift, deduced from the capacitance transients measured at  $V_g \approx V_{th}$ -0.2 V (exemplified in Fig. 3(b)). Only relative change  $(\Delta V_{th})$  between  $V_{th}$  transients measured after 'filling' pulse  $V_{g,F} = 0$ (no filling of interface traps) and  $V_{g,F} = 4 \text{ V}$  (interface traps filling) is used for  $D_{it}$  determination, to cancel out pronounced trapping of electrons by the bulk oxide traps (i.e. positive  $V_{th}$  drift) previously discussed in Ref. [13].  $D_{it}(E)$  is determined from the time derivative of  $\Delta V_{th}$  transient as  $D_{it} = \left(C_{ox}/qkT\right) \left[\partial \Delta V_{th}(t)/\partial (\log_{10} t)\right]$ , where  $C_{ox}$  is the oxide capacitance, q is an electron charge, kis the Boltzmann constant, and  $E_{it} = E_C - kT \ln (\gamma_n \sigma_n T^2 t)$ , where  $\gamma_n = 3.25 \times 10^{21} (m_n/m_0) \text{ cm}^{-2} \text{s}^{-1} \text{K}^{-2}$ ,  $m_n$  is the electron density-ofstates effective mass, and  $\sigma_n$  is the capture cross-section set to  $10^{-16}$  cm<sup>2</sup>. In filtered light-assisted  $V_{th}$  transient technique (exemplified in Fig. 3(c)) [13], the difference between  $V_{th}$  transient measured in the dark and after light exposure ( $\Delta V_{th}$ , the light was exposed at t=30 s of elapsed time) is used.  $D_{it}(E)$  was calculated as  $D_{it}(hv_i) = C_{ox} \left[ \Delta V_{th,i} / q(hv_i - hv_{i-1}) \right]$ , where  $hv_i$  is the *i*-th light energy successively increased from 1.7 to 3.0 eV, while the light

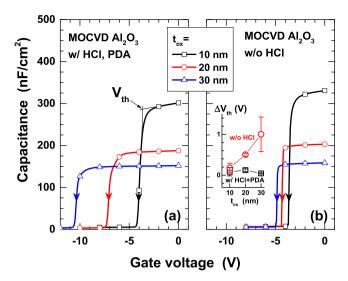

**Fig. 1.** (Color online) CV characteristics of MOS-HEMT structures with different thickness of  $Al_2O_3$  gate dielectrics grown by MOCVD with HCl pre-treatment and PDA (a) and without HCl pre-treatment (b). Also depicted is the graphical extraction of  $V_{th}$  from the CV curves. Inset shows CV hysteresis ( $\Delta V_{th}$ ) of the corresponding MOS-HEMT structures measured using  $V_g$  swept from  $V_{th}$  –3  $V_t$  to positive bias (3/5/6  $V_t$  for 10/20/30 nm-thick  $Al_2O_3$ ) and backwards using sweep rate of 0.2  $V_t$ s.

energy as measured from  $E_C$  was used for  $E_{it}$ . The light from the broad-band Xe-lamp (SP, ASB-XE-175) was filtered using bandpass metal interference filters with FWHM spectral transmittance ranging from 17.5 to 5 nm for light energy of 1.75–3.25 eV, respectively.

#### 3. Results and discussion

#### 3.1. Surface donors manipulation

As discussed in Ref. [18],  $V_{th}$ - $t_{ox}$  dependence can be used to determine charge distribution in the MOS-HEMT structure. While quadratic  $V_{th}$ - $t_{ox}$  dependence indicates charge distributed in the oxide bulk, linear dependence implies a sheet charge distribution [15]. Assuming the sheet charge to be located at the oxide/III-N interface, the slope of  $V_{th}$ - $t_{ox}$  dependence is related to  $N_{int}$  as [18]

$$\varepsilon_{ox} \frac{dV_{th}}{dt_{ox}} - P_{QW} = qN_{int} = P_S + qN_{SD} + qN_{it}$$

,(1)

where  $P_{QW}$  is the polarization charge at AlGaN/GaN interface and  $P_S$  is the surface polarization charge, which includes polarization charge at the GaN-cap surface and GaN-cap/AlGaN interface, as discussed in [13]. The same  $P_S$  was used for all structures, assuming negligible variation of GaN-cap surface and GaN-cap/AlGaN interface polarization charges due to HCl treatment (native oxides removal) and PDA performed at temperature well below that used for the growth of III-N heterostructure.  $N_{SD}$  is the SD density providing compensation of  $P_S$  and  $N_{it}$  is the interface trapped charge, representing the sheet density of ionized interface states. These states often lie deep in the energy gap of the GaN barrier and behave as fixed-like charge, unless elevated temperature or light emission is employed to activate their trapping behavior. We note that in contrast to Ref. [15], the interfacial (sheet) oxide fixed charge,  $N_{OX}$ , is included in  $N_{SD}$  in Eq. (1) for simplicity.

Fig. 1 exemplifies typical CV characteristics of MOS-HEMT structures for different  $t_{ox}$ , used for graphical extraction of the devices' threshold voltage  $(V_{th})$ , as depicted in Fig. 1(a). To minimize parasitic positive drift of the CV curve upon application of negative gate voltage  $(V_g)$  discussed below, measurement was performed from  $V_g = 0$  (i.e. equilibrium) towards depletion region. While structures

#### Download English Version:

## https://daneshyari.com/en/article/5349558

Download Persian Version:

https://daneshyari.com/article/5349558

<u>Daneshyari.com</u>