#### G Model APSUSC-34538; No. of Pages 4

## **ARTICLE IN PRESS**

Applied Surface Science xxx (2016) xxx-xxx

Contents lists available at ScienceDirect

## **Applied Surface Science**

journal homepage: www.elsevier.com/locate/apsusc

Full Length Article

## Effect of annealing ambient on SnO<sub>2</sub> thin film transistors

Priyadarshini D.M. <sup>a,b,\*</sup>, Ramanjaneyulu Mannam <sup>b</sup>, M.S. Ramachandra Rao <sup>b</sup>, Nandita DasGupta <sup>a,\*\*</sup>

- <sup>a</sup> Microelectronics and MEMS Laboratory, Department of Electrical Engineering, IIT Madras, Chennai, 600036, India

- b Department of Physics, Nano Functional Materials Technology Centre and Materials Science Research Centre, IIT Madras, Chennai, 600036, India

#### ARTICLE INFO

Article history: Received 15 October 2016 Accepted 29 November 2016 Available online xxx

Keywords: SnO<sub>2</sub> Annealing Thin film transistor Solution processed

#### ABSTRACT

In this study, the effect of annealing ambient on  $SnO_2$  thin film transistors (TFTs) is presented. Phase pure  $SnO_2$  films have been deposited using solution processed spin coating technique with  $SnCl_2$  as the precursor material. The films are annealed at  $500\,^{\circ}C$  for 1 h in different annealing ambient conditions with varying  $N_2$ : $O_2$  ratio. Top gate, bottom contact TFTs have been fabricated with  $SnO_2$  as the channel layer, silicon as the gate, silicon dioxide as the dielectric and gold as the contact material. XRD patterns reveal the amorphous nature of films. AFM image shows that the spin coated films are pin-hole free with extremely smooth surface morphology. PL and XPS measurements reveal that with increase in  $N_2$ % during annealing, the defects in the films increase. However, with increase in nitrogen concentration, the device performance improves, the threshold voltage shifts towards lower values and mobility increases, but very high  $N_2$ % is not suitable for device operation, a 70%  $N_2 + 30\%$   $O_2$  annealing ambient is found to be suitable with devices showing saturation mobility of  $0.23\,\mathrm{cm}^2\mathrm{V}^{-1}\mathrm{s}^{-1}$  and threshold voltage of  $6.8\,\mathrm{V}$  and on/off ratio of  $10^6$ .

© 2016 Elsevier B.V. All rights reserved.

#### 1. Introduction

Metal oxide semiconductors are gaining popularity over a-Si: H and polycrystalline silicon as channel layer of thin film transistors (TFTs) [1,2]. They have the advantages of high mobility, low processing temperature, large area uniformity and also high transparency, making them suitable candidates for use in display applications [3–5]. Among the different metal oxides, binary oxide semiconductors such as ZnO, SnO<sub>2</sub>, In<sub>2</sub>O<sub>3</sub> have the advantage of simplicity without having to use multiple cations [6]. Tin oxide (SnO<sub>2</sub>) based transistors are a cheaper alternative compared to indium based transistors. Recent reports on TFTs fabricated using SnO<sub>2</sub> by processing it through solution method have shown properties comparable to vacuum deposited methods [7,8].

Solution based processes inherently require annealing to rearrange the structure and adjust the electrical characteristics of the films. It alters the interface quality between the semiconductor and

E-mail addresses: priyadarshini1800@gmail.com (P. D.M.), nand@iitm.ac.in (N. DasGupta).

http://dx.doi.org/10.1016/j.apsusc.2016.11.233 0169-4332/© 2016 Elsevier B.V. All rights reserved. the dielectric layer. Annealing ambient is one of the key factors which influences the defects present in the material. As oxygen vacancies are the main source of free electrons in oxide semiconductors, by carefully controlling the oxygen content during annealing, the film conductivity can be varied, which significantly influences the device performance [9–11]. This study presents the influence of annealing ambient on  $SnO_2$  thin films and thin film transistors. The films have been annealed in different ambient conditions with varying  $N_2\colon O_2$  ratio, namely,  $100\%\ N_2$ ,  $70\%\ N_2+30\%\ O_2$ ,  $35\%\ N_2+65\%\ O_2$  and  $100\%\ O_2$  ambient conditions. PL and XPS studies have been carried out to understand the nature of defects for different annealing ambient conditions and transfer characteristics are examined to understand the device performance.

#### 2. Experimental procedure

Bottom-gate top-contact transistors are fabricated on  $Si/SiO_2$  substrates. A 100 nm thick  $SiO_2$  layer is grown by thermal oxidation on  $n^+$  type Si substrate. Silicon acts as the gate and  $SiO_2$  is the gate insulator of the transistor. The precursor solution for spin coating is prepared by dissolving 2.5 mM of  $SnCl_2$  in 20 mL of methanol. All reagents were purchased from Sigma-Aldrich and used as received. After stirring at  $45\,^{\circ}C$  for 1 h, the prepared  $SnO_2$  precursor solution was spin-coated on  $Si/SiO_2$  substrates at a rate of 3000 rpm for 30 s. Before spin coating, the  $SiO_2$  layer is treated with piranha solution

<sup>\*</sup> Corresponding author at: Microelectronics and MEMS Laboratory, Department of Electrical Engineering, IIT Madras, Chennai, 600036, India/Department of Physics, Nano Functional Materials Technology Centre and Materials Science Research Centre, IIT Madras, Chennai, 600036, India.

<sup>\*\*</sup> Corresponding author.

P. D.M. et al. / Applied Surface Science xxx (2016) xxx-xxx

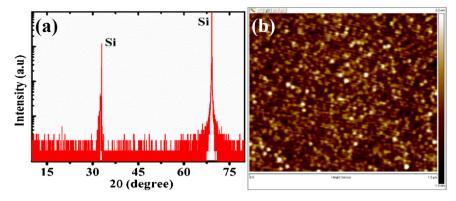

Fig. 1. (a) XRD (b) AFM image of SnO<sub>2</sub> films annealed at 500 oC for 1 h in 70% N<sub>2</sub> + 30% O<sub>2</sub> ambient.

(mixture of sulphuric acid  $(H_2SO_4)$  and hydrogen peroxide  $(H_2O_2)$ in 3:1 ratio) to make the surface more hydrophilic.

The spin coated films are then dried at 120 °C on a hotplate for 30 min. After drying, the films were annealed at 500 °C for 1 h in a tube furnace with controlled flow of mixture of O2 and N2 with varying percentage of nitrogen and oxygen. The films have been annealed in different annealing ambient conditions, namely, 100%  $N_2$ , 70%  $N_2$  + 30%  $O_2$ , 35%  $N_2$  + 65%  $O_2$  and 100%  $O_2$  ambient. The source and drain electrodes (Cr/Au - 5 nm/50 nm) are deposited by an e-beam evaporator after photolithography. Lift off process is done to pattern the source drain contacts and aluminium back metallization is carried out for gate contact.

X-ray diffraction (XRD) measurements were carried out using PANalytical, X'PERT-pro diffractometer with Cu K $\alpha$  ( $\lambda$  = 1.5418 Å) radiation. Surface morphology of the film was characterized using atomic force microscopy (AFM) (Bruker, dimension edge). X-ray photoelectron spectroscopy (XPS) measurements were performed using SPECS, PHIBOS100 energy analyser (SPECS GmbH, Germany) with Al-  $K\alpha$  (1486.61 eV) radiation to excite the electrons. Room temperature photoluminescence (RTPL) measurements were carried out using JY-Horiba, Fluorolog-3 spectra fluorometer with double grating monochromator (1200 grooves/mm, 4 nm slit width) on both excitation and emission sides. All the PL spectra were corrected for instrumental corrections. Oxide thickness was measured using spectroscopic ellipsometer (J.A. Woollam EC 400). Electrical characterization was carried out using Agilent's 1500A semiconductor device analyzer.

#### 3. Results and discussion

Fig. 1 (a) shows the XRD pattern of SnO<sub>2</sub> films on Si/SiO<sub>2</sub> substrate annealed at 500  $^{\circ}$ C in 70% N<sub>2</sub> + 30% O<sub>2</sub> ambient. XRD indicates that the SnO<sub>2</sub> films are amorphous in nature. The two peaks observed correspond to only silicon substrate. Films annealed at different annealing ambient conditions are also seen to be amorphous in nature. Amorphous films have the advantage of large area uniformity and have smoother surfaces due to uniform structures, resulting in smooth channel interfaces to the gate insulator. Also, they do not suffer from grain boundary problems as in case of polycrystalline films [12,13]. Fig. 1 (b) shows the atomic force microscopy (AFM) image of the film over an area of  $1 \mu m \times 1 \mu m$ . From the AFM image, it can be seen that the films do not have any pin holes present. The samples have surface roughness less than 2 nm indicating a very smooth surface.

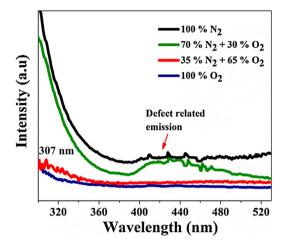

Fig. 2 shows the PL emission spectra for films annealed in different ambient conditions with 280 nm excitation wavelength. It can be seen from Fig. 2 that the emission spectrum consists of a UV emission peak around 307 nm and a broad emission band in the visible region consisting peaks around 410 nm, 437 nm and 467 nm.

Fig. 2. PL spectra of SnO<sub>2</sub> films annealed with different ambient conditions.

The peak at 307 nm ( $\sim$ 4 eV) in the UV region corresponds to the transition of electron from the conduction band to the valence band [14]. The luminescence in the visible region is due to defects and/or traps present in the material. The peaks positioned around 410 nm and 437 nm are assigned to transitions from Sn<sub>i</sub> levels to VBM and from  $Sn_i$  to  $V_{Sn}$  respectively [15]. The peak positions around 467 nm are assigned to the transitions from oxygen vacancies to VBM [16]. As can be seen from Fig. 2, with increase in N<sub>2</sub>% during annealing, the defect luminescence increases. This signifies that more defects such as oxygen vacancies and Sn interstitials are created in the material.

Further, XPS studies have been carried out. Survey scan spectra of XPS shows only expected elements (Sn, O) are present in the films (not shown here). This clearly indicates that all films are free of detectable contaminations. Fig. 3 (a) and 3 (b) show the Sn 3d and O 1 s spectra respectively for different annealing ambient conditions. In the Sn 3d spectra, the peaks at 486.8 eV and 495.3 eV are assigned to Sn  $3d_{5/2}$  and Sn  $3d_{3/2}$  respectively [17]. O 1s peak is asymmetric and it can be fitted into two peaks. The peak at lower binding energy (530.8 eV) is assigned to  $O^{2-}$  state. i.e Sn-O bonding in SnO<sub>2</sub> films. The peak at higher binding energy (532.5 eV) is due to the oxygen deficiency [18]. It is worth mentioning that before collecting the XPS data, film is sputtered using Ar+ ion gun to remove surface contamination. So the possibility of surface adsorbed hydrogen can be ruled out and the peak at 532.5 eV is assigned to O defects in SnO<sub>2</sub> films [18].

As can be seen from Fig. 3 (a) the Sn peak position remains constant with different annealing ambient conditions signifying that Sn remains in its 4+ state for all annealing ambient conditions.

Please cite this article in press as: P. D.M., et al., Effect of annealing ambient on SnO<sub>2</sub> thin film transistors, Appl. Surf. Sci. (2016), http://dx.doi.org/10.1016/j.apsusc.2016.11.233

### Download English Version:

# https://daneshyari.com/en/article/5350169

Download Persian Version:

https://daneshyari.com/article/5350169

<u>Daneshyari.com</u>