Contents lists available at ScienceDirect

journal homepage: www.elsevier.com/locate/mejo

## Analytical models for channel potential, threshold voltage, and subthreshold swing of junctionless triple-gate FinFETs

## Guangxi Hu<sup>\*</sup>, Shuyan Hu, Jianhua Feng, Ran Liu, Lingli Wang, Lirong Zheng

State Key laboratory of ASIC and system, School of Information Science and Technology, Fudan University, 220 Handan Road, Shanghai 200433, China

#### ARTICLE INFO

### ABSTRACT

Article history: Received 7 April 2015 Received in revised form 5 October 2015 Accepted 4 February 2016 Available online 23 February 2016

Keywords: Semiconductor device Analytical MOSFET Modeling and simulation

### 1. Introduction

As the channel length of metal-oxide-semiconductor fieldeffect transistors (MOSFETs) scales down to the deca-nanometer regimes, short channel effects (SCEs), carrier mobility degradation, and currents tunneling through the extremely thin gate oxide become much more serious [1]. To solve these problems, a new type of MOSFET, the triple-gate FinFET, has been proposed, studied and adapted as a technical solution for the 22 nm technology node and beyond [2–9]. However, as MOSFETs continue to scale down to the nanometer regimes, the fabrication processes of the source/ drain (S/D) of the traditional inversion-mode (IM) transistor are rather complicated; the large contact resistances of S/D of the IM transistor degrade the MOSFETs; and the thermal budget of the traditional S/D will be a heavy burden. All these problems will limit the use of the triple-gate FinFETs. To tackle these problems and to improve the device performance, the junctionless (JL) MOSFET was put forward and explored to a great extent [10–17]. Unlike the traditional IM transistor where accepters and donors are doped in the channel and the S/D regions, respectively, a JL transistor is doped with the same type of dopant throughout the channel and S/D regions. Therefore, the fabrication processes are simplified and the S/D contact resistances are decreased.

To facilitate the applications of the device in integrated circuits, analytical models for channel potential, threshold voltage,  $V_{th}$ , and subtreshold swing, *SS*, are inevitably needed in the practical use

\* Corresponding author. E-mail address: gxhu@fudan.edu.cn (G. Hu).

http://dx.doi.org/10.1016/j.mejo.2016.02.003 0026-2692/© 2016 Elsevier Ltd. All rights reserved. Analytical models for channel potential, threshold voltage, and subthreshold swing of the short-channel fin-shaped field-effect transistor (FinFET) are obtained. The analytical model results are verified against simulations and good agreements are observed. Analytical expressions for subthreshold swing, drain induced barrier lowering effect, and threshold voltage roll-off characteristics are presented. The explicit expressions for threshold voltage and subthreshold swing make the model useful in the practical applications of the device.

© 2016 Elsevier Ltd. All rights reserved.

of the device. Lots of theoretical researches have been carried out on the characteristics of drain current,  $I_{DS}$ ,  $V_{th}$ , and SS of the JL double-gate (DG) MOSFETs in the literature [18–21]. Explorations on the analytical models of the JL surrounding-gate (SG) or nanowire MOSFETs have been conducted in [22–26]. In our previous work, we obtained the analytical models of  $V_{th}$  and SS for JL SG transistors [27]. Trevisoli and others investigated the  $I_{DS}$  model for triple-gate JL nanowire transistors [28]. They obtained the  $I_{DS}$ model based on the approach of adding the solution of the 3-D Laplace equation to the solution of the 2-D Poisson equation, instead of solving the 3-D Poisson equation directly. The analytical expressions for  $V_{th}$  and SS of the JL FinFET with a short channel are desired in the applications of the device.

In this work, we focus our research on the  $V_{th}$  and SS of the JL FinFET with a short channel. We solve the 3-D Poisson equation directly and obtain an analytical expression for channel potential. Then, we achieve the analytical expression for  $V_{th}$  based on the new definition we put forward in our previous work [27]. After that, analytical expressions for SS, drain induced barrier lowering effect (DIBL) and  $V_{th}$  roll-off characteristics are obtained.

#### 2. Analytical model

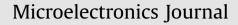

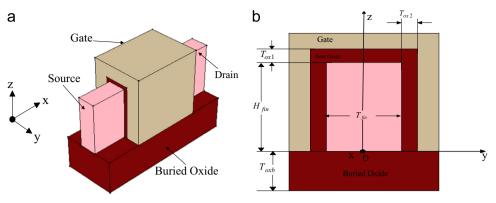

The sketches of the JL FinFET similar to those in [8] are shown in Fig. 1(a) and (b). The Cartesian axes of x, y, and z are along the channel length, width, and height directions, respectively. The channel material of the device is heavily n-doped silicon. The channel is surrounded with a very thin oxide layer and the oxide is

Fig. 1. (a) Bird's eye view of a FinFET. (b) Cross section view of a FinFET.

then enclosed with a fin-shaped gate, which can either be a metal or a heavily doped polysilicon.

The Poisson equation in the channel is

$$\frac{\partial^2 \phi}{\partial x^2} + \frac{\partial^2 \phi}{\partial y^2} + \frac{\partial^2 \phi}{\partial z^2} = -\frac{q N_D}{\varepsilon_{si}} \bigg[ 1 - \exp\bigg(\frac{\phi - V}{V_t}\bigg) \bigg],\tag{1}$$

where  $\phi$  is electric potential,  $N_D$  the doping density, and  $\varepsilon_{si}$  the permittivity of silicon.  $V_t = k_B T/q$  is thermal voltage and V is the quasi-Fermi potential. q,  $k_B$ , and T have their usual meanings.

#### 2.1. Electric potential in the channel

In this work, the voltage at the source end is set to be the reference,  $V_{R}$ . Similar to the treatment used in [2,3,8], the boundary conditions of the device can be simplified as follows:

$$\phi(0, y, z) = V_R \tag{2a}$$

$$\phi(L, y, z) = V_R + V_{DS},\tag{2b}$$

$$\phi(\mathbf{x}, T_{eff}/2, z) = V_{GS} - V_{FB}, \qquad (2c)$$

$$\phi(x, -T_{eff}/2, z) = V_{GS} - V_{FB}, \qquad (2d)$$

$$\phi(x, y, H_{eff}) = V_{GS} - V_{FB}, \qquad (2e)$$

$$\left. \frac{\partial \phi}{\partial z} \right|_{z=0} = 0 \tag{2f}$$

where  $V_{DS}$  is the drain bias,  $V_{GS}$  the gate bias,  $V_{FB}$  the flat-band voltage, and *L* the gate length.  $T_{eff}$  and  $H_{eff}$  are effective thickness and effective height of the channel, defined as [2,3]

$$T_{eff} = \sqrt{T_{fin} (T_{fin} + 4T_{ox2} \varepsilon_{si} / \varepsilon_{ox})},$$

(3a)

$$H_{eff} = \sqrt{H_{fin}(H_{fin} + 2T_{ox1}\varepsilon_{si}/\varepsilon_{ox})},$$

(3b)

where  $T_{ox1}$ , and  $T_{ox2}$  are the oxide thicknesses shown in Fig. 1(b), and we assume  $T_{ox1} = T_{ox2} = T_{OX}$  in this work.  $H_{fin}$ , and  $T_{fin}$  are the channel height and channel thickness, respectively.  $\varepsilon_{ox}$  is the permittivity of the oxide.

From (2f), the bottom boundary condition could be replaced with the following equation [3]

$$\phi(x, y, -H_{eff}) = V_{GS} - V_{FB}.$$

(4)

It is hard to obtain an analytic solution of potential  $\phi$  in (1). Different from the traditional IM FinFET, the JL FinFET will be turned on in the partially depleted region, and turned off in the fully depleted region [21,25,27]. Similar to the treatment used in [25,27], a full depletion approximation is used, the exponential term in (1) can be ignored in the subthreshold region, and (1) is

simplified to:

$$\frac{\partial^2 \phi}{\partial x^2} + \frac{\partial^2 \phi}{\partial y^2} + \frac{\partial^2 \phi}{\partial z^2} = -\frac{q N_D}{\varepsilon_{si}}.$$

(5)

With boundary conditions (2a) and (2b), the electric potential along the channel length direction (x) can be described by a summation of series [8,29,30], then, analytic solution for (5) can be obtained

$$\phi(x, y, z) = V_R + \frac{V_{DS}}{L}x + \sum_{n=1}^{\infty} A_n(y, z) \sin\left(\frac{n\pi}{L}x\right)$$

(6)

As shown in the Appendix A,  $A_n(y,z)$  is given by

$$A_{n}(y,z) = G_{n}(y,z) + \varphi_{n}, \qquad (1)$$

where  $G_{n}(y,z) = \sum_{m} \sum_{l} g_{ml}(n) \cos\left[\frac{(m-0.5)\pi}{t}y\right] \cos\left[\frac{(l-0.5)\pi}{h}z\right]$

$$g_{ml}(n) = \frac{(-1)^{m+l+1}4(d_{n}+k_{n}^{2}\varphi_{n})}{(m-0.5)(l-0.5)\pi^{4}\left[(m-0.5)^{2}/t^{2}+(l-0.5)^{2}/h^{2}+n^{2}/L^{2}\right]}, \qquad \varphi_{n} = \frac{2}{n\pi} \left\{ (V_{GS} - V_{FB} - V_{R}) \left[1 - (-1)^{n}\right] + V_{DS}(-1)^{n} \right\}$$

$$k_{n} = n\pi/L, d_{n} = \frac{2qN_{D}}{n\pi\varepsilon_{si}} \left[ (-1)^{n} - 1 \right]$$

$$t = T_{eff}/2, h = H_{eff} \qquad (8)$$

*m*, *n*, and *l* are all positive integers.

#### 2.2. Threshold voltage

Similar to the definition used in [25,27], the threshold voltage in this paper is defined as the voltage applied to the gate to make the whole channel in full depletion, which means the mobile charges can be neglected. Exactly speaking, however, the mobile charge density varies in the channel as a function of the electric potential. We choose a location where the electric potential of the average value,  $\phi_{ave}$ . Generally, for the JL FinFETs,  $V_{CS} < V_{FB}$ , then along the *y* and *z* directions, the electric potential will be the highest at the location y=0 and z=0. So we choose the average potential place at the location:  $x = x_{min}, y = 0, z = 0$ , which means

$$\varphi_{ave} = \varphi(x_{\min}, 0, 0), \tag{9}$$

where  $x = x_{min}$  is the location the electric potential reaches the minimum along the *x* direction, it can be approximated as [2,4]:

$$x_{min} = \frac{L}{2} - \frac{1}{2\pi} \left( \frac{1}{T_{eff}^2} + \frac{0.5}{H_{eff}^2} \right)^{-1/2} \ln(1 + V_{DS}/V_R).$$

(10)

If the following equation holds true,

$$\varphi(x_{\min}, 0, 0) - V = -2V_t, \tag{11}$$

the exponential term in (1) is then negligibly small and the channel can be considered as in full depletion condition, and,

Download English Version:

# https://daneshyari.com/en/article/541215

Download Persian Version:

## https://daneshyari.com/article/541215

Daneshyari.com