Microelectronics Journal 38 (2007) 164-170

### Microelectronics Journal

www.elsevier.com/locate/mejo

# Reliability study of power RF LDMOS device under thermal stress

M.A. Belaïd\*, K. Ketata, K. Mourgues, M. Gares, M. Masmoudi, J. Marcon

LEMI, University of Rouen, IUT Rouen, 76821, Mont Saint Aignan, France

Received 6 January 2006; received in revised form 27 July 2006; accepted 17 August 2006 Available online 10 October 2006

#### **Abstract**

This paper presents the results of comparative reliability study of two accelerated ageing tests for thermal stress applied to power RF LDMOS: Thermal Shock Tests (TST, air-air test) and Thermal Cycling Tests (TCT, air-air test) under various conditions (with and without DC bias, TST cold and hot, different extremes temperatures  $\Delta T$ ). The investigation findings of electrical parameter degradations after various ageing tests are discussed. On-state resistance ( $R_{\rm ds~on}$ ) is reduced by 12% and feedback capacitance ( $C_{\rm rss}$ ) by 24%. This means that the tracking of these parameters enables to consider the hot carrier injection as dominant degradation phenomenon. To reach a better understanding of the physical mechanisms of parameter's shift after thermal stress, a numerical device model (2D, Silvaco-Atlas) was used to confirm degradation phenomena.

© 2006 Elsevier Ltd. All rights reserved.

Keywords: Simulation; Hot carrier effects; LDMOS; Thermal stress

#### 1. Introduction

RF LDMOS is becoming increasingly important in communication sector, such as mobiles, portable computers and eventually base stations, thus generating ongoing effort demand to improve performances. The device's lifetime is one of the criteria used to qualify a technology. Temperature is a critical parameter, particularly in RF power electronic devices. This element has a considerable influence on reliability and performances [1,2], can limit the lifetime of semiconductors and consequently plays an essential part in failure mechanisms [1,3]. For these reasons thermal shocks and cycling conditions are becoming important for RF LDMOS in many applications. It is well-known that if devices are repeatedly subjected to electrical and thermal overload over extended periods of time, shock and cycling phenomena may lead to device failure, leaving the load current unlimited and therefore leading to serious risk of damage [4]. The objective of the presented work is a comparative reliability study of various thermal stress conditions, respecting to other studies in the

extraction

modelling the device before and after ageing.

literature. The methodology consists in characterizing and

It is essential to characterize power RF LDMOS in order to extract parameters before and after device stress. This step would enable us to correlate thermal stress to any parameter drift, or even to help identify a degradation phenomenon. A commercial Motorola RF LDMOS has been used for this study. The main characteristics of this device can be listed as follows: frequencies up to 2 GHz, output power of 10 W, breakdown voltage of 65 V. I-V and C-V measurements were performed using the commercial software package IC-CAP.

The static mode I-V gives us an insight into the device behaviour in its various operating modes (linear, saturated, etc.), and allows to quantify some important electrical parameters before and after device stress. These measurements were performed by an Agilent E5270 DC analyser with 20 W power supply. The device was mounted on a Peltier module in order to stabilize the self-heating during DC measurements. The use of data management under IC-CAP allows checking the consistency of measurements [5].

<sup>2.</sup> Device experimental characterization and parameters

<sup>\*</sup>Corresponding author. Tel.: +33 2351 47179; fax: +33 2351 46254. E-mail address: Mohamed-ali.belaid@univ-rouen.fr (M.A. Belaïd).

From these measurements, on-state resistance ( $R_{ds\_on}$ ) was deduced as a critical electrical parameter.

C-V profiles were performed using an HP 4194A impedance analyser, with a 2-pin method (which yields the total capacitance between the measurement pins:  $C_{\rm rss}$ ), the third transistor pin being unconnected [5]. These electrical parameters ( $R_{\rm ds\_on}$ ,  $C_{\rm rss}$ ) will be helpful in our reliability study to keep track of electric device degradation state. In this study, for each test conditions, five samples have been tested to ensure the reproducibility of the results.

To quantify the parameter shift that appears after ageing, a new electro-thermal model was used for power RF LDMOS devices as a reliability tool [6]. It has been implemented in Agilent's ADS software using Symbolic Defined Device (SDD), by providing a more accurate and flexible model. For simplicity, the new IC-CAP plot optimizer feature was applied instead of direct model parameter extraction.

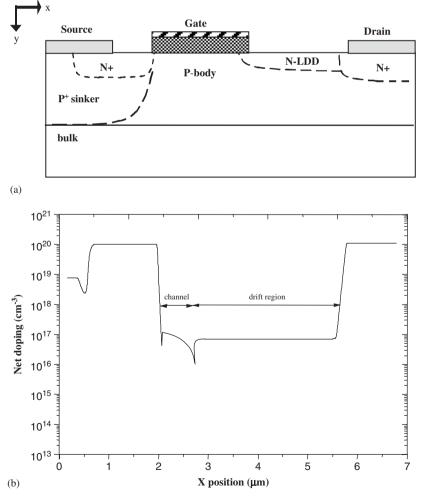

The qualitative understanding of physical phenomenon is also presented. A modified 2D RF power N<sup>-</sup> channel LDMOS structure previously developed by Raman et al. [7] was implemented and simulated using the physical

simulator Atlas of Silvaco [8]. Fig. 1 shows the device's structure with approximate doping wells. The main geometrical and technological parameters are given in Table 1. The implemented structure is typically similar to our tested device. The suggested structure has a Gaussian doping profile along LDD and channel surface. The doping profile was optimized using a 2D technological process simulation carried out by SSUPREM3 [8], see Fig. 1.

#### 3. Thermal stress bench

In our experiments, the devices are stressed with an applied drain–source voltage ( $V_{\rm ds}$ ) of 40 V and a gate–source voltage ( $V_{\rm gs}$ ) of a value to obtain a permanent drain–source current ( $I_{\rm ds}$ ) less than 10 mA (without a self-heating effect), that corresponds to the quiescent current at ambient temperature. The thermal stresses were performed with a THERMONICS T-2820 Precision Temperature Forcing System (PTFS). The system is most commonly used for direct testing of semiconductor components at temperature extremes while they are on an auto-tester performance board. This enables measurement of all

Fig. 1. (a) Cross-section view of RF LDMOS device implemented in Silvaco-Atlas, with its intrinsic capacitances and (b) Net doping profile along silicon surface.

## Download English Version:

# https://daneshyari.com/en/article/542630

Download Persian Version:

https://daneshyari.com/article/542630

Daneshyari.com