Contents lists available at ScienceDirect

**Optics Communications**

journal homepage: www.elsevier.com/locate/optcom

## Control mechanism of double-rotator-structure ternary optical computer

<sup>a</sup> School of Information Engineering, East China Jiao tong University, Shuanggang Road, Nanchang 330013, China

<sup>b</sup> Software School, East China Jiao tong University, Shuanggang Road, Nanchang 330013, China

<sup>c</sup> School of Computer, Wuhan University, Bayi Road, Wuhan 430072, China

## ARTICLE INFO

Keywords: Double rotator structure Ternary optical processor Reconfiguration Control mechanism

### ABSTRACT

Double-rotator-structure ternary optical processor (DRSTOP) has two characteristics, namely, giant data-bits parallel computing and reconfigurable processor, which can handle thousands of data bits in parallel, and can run much faster than computers and other optical computer systems so far. In order to put DRSTOP into practical application, this paper established a series of methods, namely, task classification method, data-bits allocation method, control information generation method, control information formatting and sending method, and decoded results obtaining method and so on. These methods form the control mechanism of DRSTOP. This control mechanism makes DRSTOP become an automated computing platform. Compared with the traditional calculation tools, DRSTOP computing platform can ease the contradiction between high energy consumption and big data computing due to greatly reducing the cost of communications and I/O. Finally, the paper designed a set of experiments for DRSTOP control mechanism to verify its feasibility and correctness. Experimental results showed that the control mechanism is correct, feasible and efficient.

#### 1. Introduction

With the continuous progress of science and technology, people's requirements for computing speed are also increasing. The main means of increasing computing speed for computers is to increase the processing power of the CPU, and to enhance the CPU's processing power mainly depends on the increase of chip integration [1-3]. Since the first tube computer was invented in 1946, the Moore's Law is always verified by the CPU's development. However, due to the limit of RC time-constant, CPU's integration will reach its upper limit sooner or later [4-7]. Ternary optical computer (TOC) is a photovoltaic hybrid computer, which uses mature liquid crystal technology to realize optical computing. It uses the common, cheap, stable electronic chip as control components, and uses opt-electronic hybrid manner to store data. TOC's architecture includes three key elements, which are using optical signal to computing, using electrical signal to control and using optelectronic hybrid manner to storage data, respectively [8-11]. The second-generation experimental system of TOC has thousands of databits that can be reconstructed easily, and these data-bits can easily be extended. Based on the second-generation experimental system, a series of experiments have been carried out, which confirmed that the main advantages of TOC are giant data-bits parallel computing and reconfigurable processor [12-16]. In addition, TOC uses liquid crystal devices (LCDs) and embedded systems as the main components [1721]. The energy consumption of these components is very small, so TOC's energy consumption is accordingly small even if it has a large number of data bits [22–27]. In current experiments, the energy consumption of a TOC, whose computing power is equivalent to dozens of CPU, is not more than a PC. In the current study phase about TOC, double-rotator-structure ternary optical processor (DRSTOP) proposed by the author is better than the others in reconfiguration speed and efficiency. DRSTOP's computing capacity can reach 2000 bit×1 GHz. When facing large-scale data processing problem, the computing capacity of DRSTOP is equivalent to hundreds of CPU. Besides, it does not require special cooling equipment, which means that it can save considerable energy [28–33]. It can be seen, DRSTOP has a wide range of applications and high application value. The work and control mechanisms of DRSTOP discussed in this paper will play a key role in specific applications.

CrossMark

#### 2. DRSTOP and its work process

#### 2.1. Double rotator typical structure

Due to the limitations of the typical structure of decrease-radix design principle (DRDP), the correspondence between the pixel bits and data bits is uncertain, which means that sometimes one data bit need two pixel bits to complete the operation. This uncertainty reduces

E-mail address: skpark@163.com (S. Kai).

http://dx.doi.org/10.1016/j.optcom.2016.12.004

<sup>\*</sup> Corresponding author.

Received 7 November 2016; Received in revised form 30 November 2016; Accepted 1 December 2016 Available online 08 December 2016 0030-4018/ © 2016 Elsevier B.V. All rights reserved.

Fig. 1. Double rotator typical structure.

the efficiency of pixel bits, and brings some difficulties for the management of data bits. Therefore, Ref. [34] proposes a new typical optical structure, as shown in Fig. 1. Since a double-layered rotator is used in this typical structure, this structure is named as double rotator structure by Ref. [35].

In Fig. 1, the polarizer Y1 and Y2 may be a vertical polarizer or a horizontal polarizer; Optical-controlled Liquid Crystal Unit (Lca and Lcb) may be in one of two states: original-rotating liquid crystal unit (ORLCU) and original-non-rotating liquid crystal unit (ONRLCU). Optical controller's function may be one of four kinds, which are open circuit, short circuit, vertical polarizer or horizontal polarizer, respectively [34,35].

#### 2.2. Reconfiguration circuit

In Fig. 1, the optical path constituted by Y1, Lca, Y2 and Lcb is called as main optical path (MOP). According to the polarization properties of the two polarizers in the MOP, the MOP can be divided into two partitions, which are HH and VV partitions. When the input of the MOP is V state, VV partitions can be used to realize the basic operation units (BOUs); when the input of the MOP is H state, HH partitions can be used to realize the BOUs. When the input of the MOP is W state, the W state can be translated to V or H state, and then VV or HH partitions can be used to realize the BOUs. In this paper, W state is always translated to V state, so the MOP of DRSTOP can be constituted by three partitions: one HH partition and two VV partitions. Similarly, with the different polarization properties of the polarizers in the controlling optical path (COP), the COP is divided into two partitions, i.e. V and H partitions. Optical controller has four values, which are penetrated optical valve, closed optical valve, vertical polarizer and horizontal polarizer, respectively. The function of reconfiguration circuit is to realize the correct selection from the three partitions of the MOP and the four values of the COP. In Ref. [35], the design process of the reconfiguration circuit is described in detail. Through designing the reconfiguration circuit and setting up the reconfiguration register's instructions [35], all 78 BOUs can be realized, and all of 19683 two-inputs, three-value logic operations can be made.

## 2.3. Realization of reconfigurable ternary optical processor (RTOP) based on double rotator structure

The reconfiguration circuit is significant in that it can connect the optical part and the circuit part in a suitable manner to form a complete RTOP. RTOP can realize the hardware reconfiguration of all 19683 two-inputs, three-value logic operations. Compared with the classical

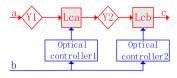

structure, DRSTOP's typical structure is changed, so the related structure in reconfiguration circuit must be changed to fit the new typical structure (as shown in module 2 of Fig. 2). In the new typical structure, the LCD units of operator was changed from one layer to two layers, which will lead to the change of the part of reconfiguration circuit associated with the LCD control signal generation circuit. According to Ref. [36], the schematic of DRSTOP is shown in Fig. 2.

In Fig. 2, S is a surface light source; ST are phototubes; XOR are XOR gates; R is pull-down resistor; DFS is a double four selector (S1<sub>in</sub> corresponds with S1<sub>out</sub>, and S1<sub>con</sub> decides which line is output; S2<sub>in</sub> corresponds with S2<sub>out</sub>, and S2<sub>con</sub> decides which line is output); RS is a reconstructing register, which has eight bits; other devices are the same as described in Fig. 1. A<sub>1</sub>A<sub>2</sub> represents the binary encoding of the main optical path input a, and B<sub>1</sub>B<sub>2</sub> represents the binary encoding of the controlling optical path input b.

The main optical path is composed of light source, four-layers polarize and two-layers LCD units. Among them the two polarizes and two LCD units close to the light source are main optical path encoder, which can transform the two-value electric signal to the three-value optical signal. The two polarizes and two LCD units in the middle are operators, which correspond to the typical optical structure in Fig. 1. The main function of reconfiguration circuit is to provide control signal for the four layers LCD. The control side of each LCD layer connects a XOR gate, whose function is to achieve the logic control of rotation property of LCD (in the actual structure, the LCD units are used that rotates the polarized light usually, but some BOUs need the LCD units that don't rotate the polarized light usually, when the XOR gate is needed to reverse control signal to realize the change of LCD rotation property). In the typical structure of Fig. 1, the optical controller has four values: floating, short, vertical polarizer and horizontal polarizer. This paper uses electricity-controlled liquid crystals in the RTOP. The control sides of these liquid crystals also have four values the same as those in the optical controller, only if the photoelectric conversion is completed. Which value will be selected is realized by the double four selector DFS. The complete RTOP includes three partitions, two of which are the same and both are called VV partitions as shown in Fig. 2. The third partition is called HH partition, similar to the VV partition, which can be realized only by changing the two V polarizes of the operator to H polarizes. The outputs of these three partitions can be superimposed to one output, which is the final output of DRSTOP [35,36].

#### 2.4. DRSTOP work process

The work process of DRSTOP is controlled by a PC (named DCP). DCP generates and formats the reconfiguration commands, MOP coding information and COP coding information, and sends these control information to the DRSTOP operation unit through the handshake signal. Then, the DRSTOP decoder sends the decoding results back to the PC. The DRSTOP operation unit includes an encoder (see module 1 in Fig. 2) and a computing unit (see module 2 in Fig. 2). According to Ref. [36], the relationship between DCP and DRSTOP is

Fig. 2. Reconfigurable ternary optical processor diagram of double rotator structure.

Download English Version:

# https://daneshyari.com/en/article/5449689

Download Persian Version:

https://daneshyari.com/article/5449689

Daneshyari.com