FISEVIER

Contents lists available at ScienceDirect

# Microelectronics Reliability

journal homepage: www.elsevier.com/locate/microrel

# Statistical variability in FinFET devices with intrinsic parameter fluctuations

Chih-Hong Hwang a, Yiming Li a,b,\*, Ming-Hung Han a

#### ARTICLE INFO

Article history:

Received 30 November 2009

Received in revised form 21 January 2010

Available online 25 March 2010

#### ABSTRACT

High- $\kappa$ /metal-gate and vertical channel transistors are well-known solutions to continue the device scaling. This work extensively estimates the influences of the intrinsic parameter fluctuations on nanoscale fin-type field-effect-transistors and circuits by using an experimentally validated three-dimensional device and coupled device-circuit simulations. The dominance fluctuation source in threshold voltage, gate capacitance, cut-off frequency, delay time, and power has been found. The emerging fluctuation source, workfunction fluctuation, shows significant impacts on DC characteristics; however, can be ignored in AC characteristics due to the screening effect of the inversion layer.

© 2010 Elsevier Ltd. All rights reserved.

## 1. Introduction

In nano-device-circuits and systems, the device variability is pronounced and becomes crucial for circuit design [1–9]. The most well-known fluctuation sources on transistors are the randomdopant-fluctuation (RDF) and process-variation-effect (PVE) [4,6,7]. The RDF comes from the manufacturing process, such as ion implantation, thermal annealing and so on. Fluctuations of device characteristics including are caused both by a fluctuation in the number of dopants and the particular random distribution of dopants in the channel region [7]. The inevitable variations of processing conditions, such as the resolution limit of lithography and the grainy nature of photo resist and gate, also impact the device dimensions. The gate length deviation and the line edge roughness are the dominating factors in PVE [4,6,7]. To suppress the impact of these variations, fin-type field-effect-transistors (FinFETs) [10–12] and high- $\kappa$ /metal-gate technology [13] are promising. However, the use of metal as gate material may introduce another source of fluctuation, workfunction fluctuation (WKF). The grain orientation of metal is uncontrollable during growth period [14]; therefore, the device threshold voltage  $(V_{\rm th})$  will become a probabilistic distribution rather than a deterministic value. Approach has been noticed the workfunction fluctuation (WKF); unfortunately, only the device  $V_{\rm th}$  fluctuation was concerned and the scope is limited to the planar transistors [14,15].

In studying the fluctuation of FinFETs, diverse approaches have recently been presented [10–12]; however, the attention is most drawn to the existence of RDF and PVE on transistors. A compre-

E-mail address: ymli@faculty.nctu.edu.tw (Y. Li).

hensive understanding of these fluctuations including WKF on Fin-FETs and circuits is lacked. Therefore, this study explores the intrinsic device parameter fluctuations (WKF, PVE, and RDF) on 16-nm-gate silicon-on-insulator (SOI) FinFETs and digital circuits by an experimentally validated three-dimensional coupled device-circuit simulation technique [8,9]. The major variability sources in device's DC/AC and circuit's timing/power characteristics are explored for the first time. The vast study assesses the fluctuation on digital circuit performance and reliability, which can be in turn used to optimize nanoscale devices and circuits.

### 2. Simulation technique

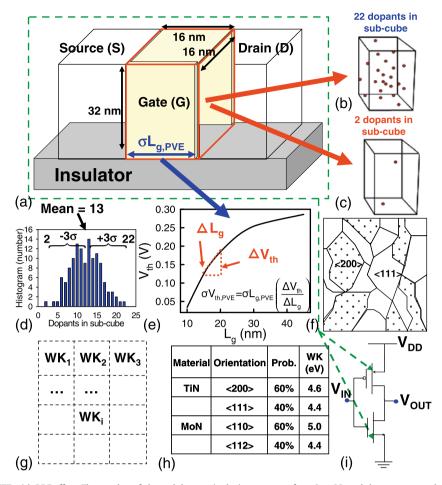

Fig. 1a illustrates the explored 16-nm-gate SOI FinFETs with amorphous-based TiN/HfSiON gate stacks with an EOT of 1.2 nm [14]. The equivalent channel doping concentration is  $1.48 \times 10^{18} \, \text{cm}^{-3}$ . Fig. 1b-d illustrates the RDF-induced fluctuation, the simulation mainly follows our recent work [7-9]. The PVE-induced fluctuation is examined by  $V_{\rm th}$  roll-off characteristics, as shown in Fig. 1e [7]. The physical models and accuracy of such large-scale simulation approach have been quantitatively calibrated by experimentally measured results [7,10]. For WKF in Fig. 1f, a Monte-Carlo approach is proposed for examining such effect, as shown in Fig. 1g. Based on the average grain size, 4 nm [14,15], the gate area is first partitioned into several parts. Then, the workfunction of each partitioned area (WK<sub>i</sub>) is randomized following the properties of metal in Fig. 1h [14,15]. The effective device workfunction is then obtained and used for estimation of WKF-induced fluctuations. Fig. 1i is the explored inverter circuit, in which a coupled device-circuit simulation approach [8,9] is employed to ensure the best accuracy. Notably, the device dimension and  $V_{\rm th}$  of both n-type and p-type transistors are the same to compare them on the same basis.

<sup>&</sup>lt;sup>a</sup> Department of Electrical Engineering and Institute of Communications Engineering, National Chiao Tung University, 1001 Ta-Hsueh Road, Hsinchu 300, Taiwan

<sup>&</sup>lt;sup>b</sup> National Nano Device Laboratories, Hsinchu 300, Taiwan

<sup>\*</sup> Corresponding author. Address: Department of Electrical Engineering, National Chiao Tung University, 1001 Ta-Hsueh Road, Hsinchu 300, Taiwan. Tel.: +886 35712121x52974.

**Fig. 1.** (a) The explore SOI FinFET with RDF effect. The number of channel dopants in device may vary from 2 to 22, and the average number is 13(b-d). (e) The  $V_{th}$  roll-off characteristics for estimating PVE. (f) Metal-gate surface morphology. (g) In estimation of WKF, the gate area is partitioned into several pieces according to the average grain size. The workfunction of each partitioned area (WK<sub>i</sub>) is a random value, whose probability follows (h). (i) The tested inverter circuit.

#### 3. Results and discussion

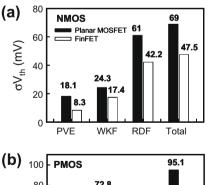

Fig. 2a and b displays the components of  $\sigma V_{\rm th}$  for *n*-type and *p*-type planar MOSFETs and FinFETs, respectively. The total  $\sigma V_{\rm th}$ ,  $\sigma V_{\rm th,total}$ , are obtained from the statistical addition as shown in below:

$$(\sigma V_{\text{th,total}})^2 - (\sigma V_{\text{th,PVE}})^2 + (\sigma V_{\text{th,WKF}})^2 + (\sigma V_{\text{th,RDF}})^2 \tag{1}$$

The oVth,PVE, oVth,WKF, and oVth,RDF are the PVE-, WKF-, and RDF-induced  $\sigma$ Vth, respectively. The FinFET shows a significantly smaller  $\sigma Vth$  than the planar MOSFET due to its better channel controllability [10]. The RDF and WKF dominate the  $\sigma$ Vth in both n-type and p-type transistors. The σVth,WKF in p-type Fin-FETs becomes comparable to σVth,RDF due to the large deviation of workfunction. In Fig. 1h, the probability for the used material TiN (for NMOS) and MoN (for PMOS) are the same; however, the differences of workfunction in different grain orientation are quite different. The large deviation of workfunction in MoN enlarges the σVth,WKF of p-type FinFETs and makes the σVth,total of p-type FinFETs larger than the n-type FinFETs. Notably, the simulation result is still valid for lightly-doped transistors, in which the lightlydoped channel is employed for the suppression of RDF. With similar simulation methodology, the WKF possesses over 95% Vth fluctuation of  $\sigma$ Vth,total, which shows the significance of controlling WKF. Fig. 3 summarizes the gate capacitance fluctuations ( $\sigma$ Cg) with 0 V, 0.5 V and 1.0 V gate bias. Different to the results of Vth fluctuation, the WKF brought less impact on gate capacitance fluc-

Fig. 2. The components of  $\sigma V_{\rm th}$  for (a) n-type and (b) p-type planar MSOFETs and SOI FIRETS

tuation. At low gate bias or negative gate bias, the accumulation layer screens the impact of WKF. Additionally, at low gate bias, the total capacitance decreases because of an increased depletion

## Download English Version:

# https://daneshyari.com/en/article/545351

Download Persian Version:

https://daneshyari.com/article/545351

<u>Daneshyari.com</u>