ELSEVIER

Contents lists available at SciVerse ScienceDirect

## Microelectronics Journal

journal homepage: www.elsevier.com/locate/mejo

# Analytical optimization of high-performance and high-yield spiral inductor in integrated passive device technology

Cong Wang, Nam-Young Kim\*

RFIC Laboratory, Kwangwoon University, 447-1 Wolgye-dong, Nowon-ku, Seoul 139-701, Republic of Korea

#### ARTICLE INFO

Article history:

Received 7 June 2011

Received in revised form

25 December 2011

Accepted 27 December 2011

Available online 9 January 2012

Reywords:

Spiral inductor

Inductance

Q-factor

Yield

Integrated passive device (IPD)

#### ABSTRACT

The analytical optimization of several spiral inductors with different inner diameters, line widths, coil spacing, turn numbers, ring shapes, metal thicknesses, and substrates was performed by the measurement-derived inductance and Q-factor. Through the analytical optimization, a thick electroplated Cu/Au metal process and an additional sputter-etching strategy on a 200  $\mu$ m finished SI-GaAs substrate with the suitable layout parameters have been proposed in order to obtain the higher performance and yield for the spiral inductors. The proposed physical layouts and fabrication parameters are an optimal solution for manufacturing spiral inductors in the integrated passive device (IPD) process that require high performance, stringent size, and volumetric efficiency.

© 2012 Elsevier Ltd. All rights reserved.

#### 1. Introduction

IPD technology has attracted significant attention in recent years, primarily due to the needs of handheld wireless devices to further decrease in cost and size and increase in performance and functionality [1–4]. Many functional blocks, such as harmonic filters, couplers, baluns, and power combiners/dividers, in the microwave modules can be realized using IPD technology [5–9]. Inductors are used extensively in RF and microwave applications for resonance circuits, phase shifters, and filters [10–13], which can dominate the performance of module circuit. Fundamentally, three basic inductor structures are feasible in IPD technology, such as the planar spiral coil structure [14,15], the multi-level-spiral inductor [16], and the solenoidal inductor [17]. Among these configurations, planar spiral inductors are generally chosen for their large inductance value, small size, and excellent Q-factor value.

The spiral inductor consists of a pair of inter-wound spirals placed on separate metal layers and the air-bridge, which offers an improved current capacity and a reduced series resistance. Since it is separated vertically to some extent, there is less capacitance between the adjacent turns. The air-bridge is required to connect the center trap of the spiral inductor to the rest of the circuit, which is often used in the first iteration in order

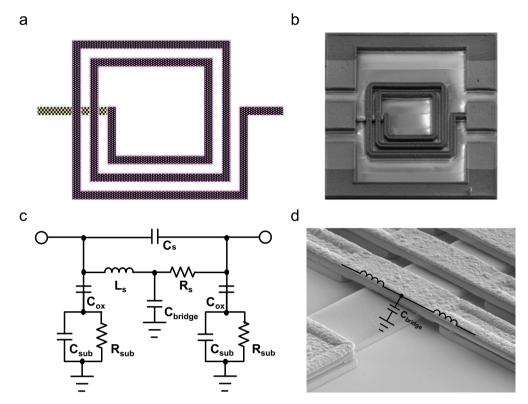

to characterize the inductor using a different numbers of turns. The Q-factor is a very important parameter in the design of the spiral inductor, which is a function of both the frequency and the geometrical parameters. The number of turns in a spiral inductor, the width of the rings, the spacing between spiral turns, and its inner diameter determine the value of the inductance and the O-factor. Although a spiral inductor is easy to fabricate, it is one of the most difficult components to model theoretically due to the electromagnetic coupling between the metal lines. Therefore, a physical experiment is usually required to analytically optimize and characterize it. By changing the geometry, the Q-factor of the spiral inductor can be optimized to the highest value in the frequency range at which the inductor will operate. It should be noted that if one takes into account the size issue in an integrated passive environment, a more inductor-rich design approach may be adopted with useful performance gains. The layout of a rectangle-type spiral inductor, the scanning electron microscope (SEM) photograph, and the equivalent circuits of the spiral inductor and the air-bridge model are illustrated in Fig. 1, where the inductance and resistance of the spiral and underpass is represented by the series inductance  $L_s$  and the series resistance  $R_{\rm s}$ , respectively. The overlap between the spiral and the underpass allows direct capacitive coupling between the two terminals of the inductor. This feed-through path is modeled by the series capacitance  $C_s$ . The capacitance of the air-bridge is modeled by C<sub>bridge</sub>. The oxide capacitance between the spiral and the substrate is modeled by  $C_{ox}$ . The capacitance and resistance of the substrate are modeled by  $C_{\text{sub}}$  and  $R_{\text{sub}}$ , respectively. The layout

<sup>\*</sup> Corresponding author. Tel.: +82 10 8721 5188; fax: +82 31 888 5254. E-mail addresses: kevinhunter0414@hotmail.com, nykim@kw.ac.kr (N.-Y. Kim).

**Fig. 1.** (a) The basic layout of a rectangle-type spiral inductor; (b) SEM photograph of the same fabricated spiral inductor; (c) the equivalent circuit of the spiral inductor; (b) the equivalent model of the air-bridge.

objective is to obtain the desired value of inductance in the smallest area possible, all the while keeping the parasitic capacitance low in order to ensure that the self-resonance frequency (SRF) of the element is outside of the designed frequency band.

Over the last few years, several techniques have been presented to optimize the physical layout of silicon-based spiral inductors [18,19]. A major shortcoming of these optimizations is that they cannot thoroughly and comparatively analyze the characteristics of spiral inductors very well due to the fact that they did not take the fabrication variables into account. These works were also grounded on a multi-variable analysis method, which cannot make us clearly understand the detailed effects of the performances of the spiral inductors on each different variable. In this study, a passive component characterization mask set was built and analyzed on the basis of univariate method with different inner diameters, line widths, coil spacing, turns, and ring shapes with various fabrication parameters in order to optimize the spiral inductor values and the Q-factors. For highly increasing spiral inductor yield, a sputter-etching surface pre-treatment process during the air-bridge formation process is proposed. Very compact spiral inductors with excellent performances and up to 100% yield can be realized in the IPD applications.

#### 2. Experimental procedure

In this section, we briefly introduce the spiral inductor fabrication process. The process features two levels of plated Cu/Au metal and all plated metals use Ti/Au 200 Å/800 Å seed sputtering prior to plating process in order to increase the plated metal adhesion to the substrate or the other metal layer. The fabrication process starts with a first passivation layer composed of  $SiN_x$  and deposited by plasma-enhanced chemical vapor deposition (PECVD) up to a thickness of 2000 Å. Next, the 1st Ti/Au seed metal layer is deposited by sputtering. Then, the wafer is masked

using photo resist in order to define the bottom metal layer structures and conventionally electroplated Cu/Au bottom metal is used as the metal beeline and rings for spiral inductor. The dielectric layer is then created by a 2000 Å SiN<sub>x</sub> thin film layer. Next, the 2nd Ti/Au seed metal layer followed by an air-bridge post-photo process is deposited. Then, an air-bridge photo process is performed prior to a Cu/Au top metal definition and electroplating process, by which the air-bridge interconnections are formed at the broken coil paths around the metal beelines for the spiral inductors. After the plating process, the air-bridge mask is stripped by a lift-off machine, and then the inductively coupled plasma reactive-ion etching (ICP-RIE) of the Ti/Au seed metal is done. Finally, all of the components are passivated with a 3000 Å SiN<sub>x</sub> in order to protect the components from oxidation and moisture. The top view of the fabricated spiral inductor and the enlarged focused ion beam (FIB) photograph of the air-bridge are shown in Fig. 2(a) and (b), respectively.

#### 3. Analytical optimization of spiral inductor

The analytical optimizations can be performed by manufacturing a matrix of spiral inductors with different physical layouts, which is shown with the fabricated wafer in Fig. 3. In order to calibrate the material properties and the simulation parameters, DC and RF measurements of simple transmission lines are used to determine the metal conductivity and the substrate loss tangent. De-embedded structures and the ground–signal–ground (GSG) test structure are used due to the calibration of the material property and the simulation methodology. These measurement-derived values were then used for the analysis of several spiral inductors with different inner diameters, line widths, coil spacing, turn numbers, and ring shapes. The basic spiral inductor structure requires two levels of plated metal and one air-bridge connection between them, which is demonstrated in Fig. 4(a). The spiral inductor is defined by the inner

### Download English Version:

# https://daneshyari.com/en/article/547613

Download Persian Version:

https://daneshyari.com/article/547613

<u>Daneshyari.com</u>