Available online at www.sciencedirect.com

MICROELECTRONICS RELIABILITY

Microelectronics Reliability 44 (2004) 2011-2017

www.elsevier.com/locate/microrel

# Prediction of thermo-mechanical integrity of wafer backend processes

V. Gonda <sup>a</sup>, J.M.J. Den Toonder <sup>c</sup>, J. Beijer <sup>b</sup>, G.Q. Zhang <sup>b</sup>, W.D. van Driel <sup>c</sup>, R.J.O.M. Hoofman <sup>d</sup>, L.J. Ernst <sup>a,\*</sup>

<sup>a</sup> Delft University of Technology, P.O. Box 5033, Mekelweg 2, 2628 CD Delft, The Netherlands

<sup>b</sup> Philips Centre for Industrial Technology, P.O. Box 218, 5600 MD Eindhoven, The Netherlands

<sup>c</sup> Philips Research Laboratories, Prof. Holstlaan 4, 5656 AA Eindhoven, The Netherlands

<sup>d</sup> Philips Research Leuven, Kapeldreef 75, B-3001 Leuven, Belgium

Received 7 October 2003; received in revised form 4 February 2004 Available online 8 July 2004

# Abstract

More than 65% of IC failures are related to thermal and mechanical problems. For wafer backend processes, thermo-mechanical failure is one of the major bottlenecks. The ongoing technological trends like miniaturization, introduction of new materials, and function/product integration will increase the importance of thermomechanical reliability, as confirmed by the ITRS (International technology roadmap for semiconductors; [1]). Since most of the thermomechanical problems initiate in the design phase, failure prevention-designing for reliability, is strongly desired. To support wafer backend process development, it is necessary to develop reliable and efficient methodologies (both testing and modeling) to predict the thermal and mechanical behavior of backend processes.

This paper presents our research results covering the backend process reliability modeling considering both thermal and mechanical (CMP) loading. The emphasis is particularly on the effect of using Cu/SiLK low-dielectric-constant (low-*k*) structure instead of the traditional Al/SiO<sub>2</sub>. SiLK is a particular polymeric low-*k* material developed by the Dow Chemical Company [2] [Adv. Mater. 12 (2002) 1767].

Our results shows that Cu/SiLK structures exhibit significantly different reliability characteristics than their aluminum predecessors, and that they are more critical from several design aspects. This not only makes the stress management in the stacks more difficult, but also strongly impacts packaging. © 2004 Elsevier Ltd. All rights reserved.

© 2004 Elsevier Etd. All fights reserve

### 1. Introduction

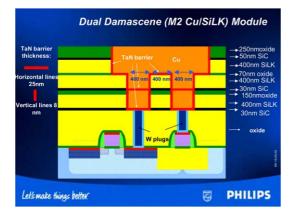

The implementation of new low-*k* dielectric materials has serious consequences for the structural integrity of Cu/low-*k* interconnects. The new materials have substantially different thermo-mechanical properties than silicon oxide (TEOS), which is being used up to now as the dielectric material. Particularly, the elastic modulus of the new materials is two orders of magnitude smaller, whereas the coefficient of thermal expansion (CTE) is 20–60 times larger. Moreover, the use of copper requires a dedicated processing technique which is called damascene process. Fig. 1 shows a cross section of a simple damascene test module. The main process steps involved in making this structure are the following:

- 1. deposition of dielectric layers

- 2. patterning the dielectric (etching)

- 3. deposition of a diffusion barrier layer (e.g. tantalum nitride (TaN)

- 4. copper electroplating

- 5. annealing

- 6. planarization (chemical-mechanical polishing, CMP)

<sup>&</sup>lt;sup>\*</sup>Corresponding author. Tel.: +31-15-278-6519; fax: +31-15-278-2150.

E-mail address: 1.j.ernst@wbmt.tudelft.nl (L.J. Ernst).

<sup>0026-2714/\$ -</sup> see front matter @ 2004 Elsevier Ltd. All rights reserved. doi:10.1016/j.microrel.2004.05.021

Fig. 1. Cu/low-k damascene test module.

The different process steps are performed at different temperatures, and therefore the stack experiences many temperature cycles during the processing. This leads to high thermal stresses/strains, which can lead to delamination or fracture of the layers.

In this paper, we study the mechanical stresses that are introduced during the main process steps in the module sketched in Fig. 1, including the situation when a precrack is present in the stack. The finite element package Marc was used to simulate the various process steps.

#### 2. Finite element analysis

The module, sketched in Fig. 1, consists of a two-level interconnect stack on a silicon wafer. To make use of the symmetry and the periodic layout, we meshed the half pitch of the module. It was assumed that the global deformations of this small part were determined by the much thicker silicon underneath.

# 2.1. Mesh

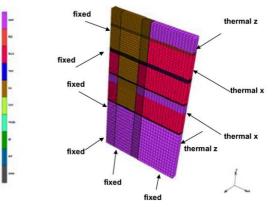

Initially a 2-D model (model 1) was made with 4-node generalized plane strain elements. Various material configurations were studied with this simple model, considering that stresses are overestimated by using plane strain conditions. Subsequently the model was expanded into the third dimension (model 2, see Fig. 2) to have a one-element thick model. Here 3-D 8-node bricks were used. The size of the meshed part is approximately  $1.5 \times 3$  µm.

Modeling the process steps, mentioned earlier, required elimination (etching) and inserting (electroplating) of material. This is implemented by activating and deactivating elements. Extra elements for the barrier layer and for the copper are located 'parallel' (on the top

Fig. 2. Boundary conditions.

of each other) to the elements of the dielectric layers, but they employed the same nodes, which prevented the misalignment of the mesh.

# 2.2. Boundary conditions

The boundary conditions (see Fig. 2) were set up to fulfill the symmetry and silicon driven global deformation conditions. Here the bending of the substrate and the internal force acting on the substrate can be ignored [3]. Fig. 2 illustrates the simplified model. Symmetry conditions are applied at the left-hand side of the model, as the vertical degree of freedom (DOF) was constrained. The bottom nodes are supported vertically, but can move horizontally. Coupled boundary conditions are applied at the right side of the module, where the applied deformations are calculated from the thermal expansion/ shrinkage of the silicon. In case of the 3-D model, the front plane was constrained against out-of-plane deformations, and the back plane was loaded with thermal deformation.

# 2.3. Loads

The applied load for model 1 was a thermal loading, consisting of slow (isothermal) cooling down from 400 °C to room temperature (25 °C), followed by CMP loading (see later). The setup was assumed to be stress free at high temperature. In model 2, the thermal loading of the main process step was simulated. This involved various temperature cycles, as shown in Fig. 3, and the (de)activating of elements corresponding to material removal and deposition. The following sequence is repeated twice, corresponding to the processing of the two levels of the dual damascene module:

- 1. Deposition of carbide, SiLK, oxide layers at 400 °C

- 2. Cool down to RT (25 °C)

- 3. Etch the layers

Download English Version:

# https://daneshyari.com/en/article/547785

Download Persian Version:

https://daneshyari.com/article/547785

Daneshyari.com