Contents lists available at ScienceDirect

### Physics Letters A

www.elsevier.com/locate/pla

# Remarkable charge-trapping performance based in $Zr_{0.5}Hf_{0.5}O_2$ with nanocrystal $Ba_{0.6}Sr_{0.4}TiO_3$ blocking layer for nonvolatile memory device

X.B. Yan<sup>a,b,\*</sup>, X.L. Jia<sup>a</sup>, T. Yang<sup>a</sup>, J.H. Zhao<sup>a</sup>, Y.C. Li<sup>a</sup>, Z.Y. Zhou<sup>a</sup>, Y.Y. Zhang<sup>a</sup>

<sup>a</sup> Key Laboratory of Digital Medical Engineering of Hebei Province, Key Laboratory of Optoelectronic Information Materials of Hebei Province, College of Electron and Information Engineering, Hebei University, Baoding 071002, PR China <sup>b</sup> Department of Materials, Science and Engineering, National University of Science Science Science and Engineering

<sup>b</sup> Department of Materials Science and Engineering, National University of Singapore, Singapore 117576, Singapore

#### ARTICLE INFO

Article history: Received 15 May 2016 Received in revised form 10 August 2016 Accepted 12 August 2016 Available online 18 August 2016 Communicated by R. Wu

Keywords: Charge trapping Nanocrystal Ba<sub>0.6</sub>Sr<sub>0.4</sub>TiO<sub>3</sub> blocking layer Zr<sub>0.5</sub>Hf<sub>0.5</sub>O<sub>2</sub> Nonvolatile memory

#### Introduction

The charge trapping memory (CTM) devices have been studied for many years, such as silicon-oxide–nitride-oxide–silicon (SONOS) type memory device. CTM as an important component of the nonvolatile flash memories has found many wide applications due to its good endurance and retention, fast program/erase speed and low operating voltage characteristics over the floating-gate devices [1,2]. However, with the further scaling down, few electrons for information storage and low charge trapping efficiency are the crucial problems for nanoscale SONOS devices [3]. To confront the challenge, bandgap-engineered charge trapping layer and high-*k* materials in which oxygen vacancy is thought to be the main defect have been proposed to be used in the CTM devices to obtain a better charge trapping capability and retention characteristics [4, 5].

$HfO_2$  is considered as the most promising dielectric among the high-*k* dielectrics. It has large band-gap, relatively high dielectric

E-mail address: xiaobing\_yan@126.com (X.B. Yan).

http://dx.doi.org/10.1016/j.physleta.2016.08.022 0375-9601/© 2016 Elsevier B.V. All rights reserved.

#### ABSTRACT

Two kinds of charge trapping memory device with Au/Zr<sub>0.5</sub>Hf<sub>0.5</sub>O<sub>2</sub>(ZHO)/SiO<sub>2</sub>/p-Si and Au/Ba<sub>0.6</sub>Sr<sub>0.4</sub>TiO<sub>3</sub> (BST)/Zr<sub>0.5</sub>Hf<sub>0.5</sub>O<sub>2</sub>/SiO<sub>2</sub>/p-Si structure were fabricated and investigated. The double BST/ZHO films exhibit a larger memory window of 7.36 V under  $\pm 14$  V sweeping voltages in its C–V curve and the device has good charge retention properties with only small charge loss of ~5% after more than 10<sup>4</sup> s. The good characteristics are attributed to the inter-diffusion between BST and ZHO where more deep defect sites were created after RTA treatment, which provides high potential barriers for the trapped charges to tunnel back to the silicon substrate. Furthermore, the nanocrystal in the BST layer increases the tunneling barrier of tunneling current into the gate and effectively restrains the leakage of storage charge from blocking layer, which improves the charge retention characteristic.

© 2016 Elsevier B.V. All rights reserved.

constant  $(22\sim25)$  and high thermal stability [6,7]. In addition, the electrical properties of HfO<sub>2</sub> can be improved by doping different elements such as Al, Zr and Ta [8,9]. On the other hand, it is well known that ZrO<sub>2</sub> is isomorphous to HfO<sub>2</sub> with a similar structure. And oxygen vacancy is verified as main defect in ZrO<sub>2</sub> and HfO<sub>2</sub> which has been investigated theoretically and experimentally [10, 11]. Furthermore, Zr-doping in HfO<sub>2</sub> can stabilize the tetragonal phase of HfO<sub>2</sub> [12,13], and enhance the *k*-value of HfO<sub>2</sub> [14]. In addition, barium strontium titanate (BST) is a kind of high dielectric coefficient of ferroelectric material, which is widely used in the dynamic random access memory (DRAM) due to its strong nonlinear, small leakage flow, large capacitance rate and anti-fatigue. The dielectric properties of BST film are related to the composition and significantly influenced by the forming process and the annealing process. Therefore, in our case, we investigated the ZHO films with and without nanocrystal BST films as blocking layer to construct CTM devices. We focus on two CTM devices with the structures of Au/ZHO/SiO<sub>2</sub>/p-Si and Au/BST/ZHO/SiO<sub>2</sub>/p-Si, and the latter shows a distinguished charge-trapping efficiency and a good retention characteristic. And we investigated the microstructure information through high resolved transmission electron microscopy (HRTEM) to make a further study about its charge trapping mechanism.

<sup>\*</sup> Corresponding author at: Key Laboratory of Digital Medical Engineering of Hebei Province, Key Laboratory of Optoelectronic Information Materials of Hebei Province, College of Electron and Information Engineering, Hebei University, Baoding 071002, PR China.

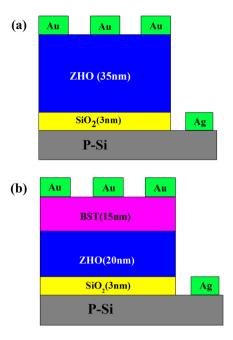

**Fig. 1.** The schematic structures of memory devices (a) with single ZHO layer and (b) with BST/ZHO double layers.

#### **Experimental details**

We fabricated two kinds of CTM structures with Au/ZHO/SiO<sub>2</sub>/ p-Si and Au/BST/ZHO/SiO<sub>2</sub>/p-Si, respectively. P-type (001) silicon wafer with a resistivity of  $< 0.005 \Omega/cm$  was ultrasonically cleaned in the acetone for 10 min, and then in the alcohol for 10 min, and then in the deionized water for 3 min. After ultrasonic cleaning, the wafer was immersed in HF diluted solution (HF:H<sub>2</sub>O = 1:3) for 90 seconds to remove the native oxides. At last, the wafer was cleaned by the deionized water to remove HF, and dried by nitrogen gas gun. The ZHO high-k film and BST film were deposited by using RF-magnetron sputtering. The chamber for RF-sputtering was under a mixed ambience of argon and oxygen with the ratio 2:1 at 3 Pa, and the RF power was 80 W. After deposition, the ZHO/SiO<sub>2</sub>/p-Si and BST/ZHO/SiO<sub>2</sub>/p-Si films were annealed at high temperatures of 600 °C in O<sub>2</sub> atmosphere for 5 min by rapid thermal annealing (RTA). For measuring the electrical properties, dot-shaped Au top electrodes with an area of  ${\sim}7.47 \times 10^{-4} \ \text{cm}^2$ were deposited on the surface of the samples using a shadow mask by vacuum evaporation. The electrical properties of the memory structure Au/ZHO/SiO<sub>2</sub>/p-Si and Au/BST/ZHO/SiO<sub>2</sub>/p-Si were characterized at a high frequency (4 MHz) by using Keithely 4200 semiconductor characterization system.

#### **Results and discussion**

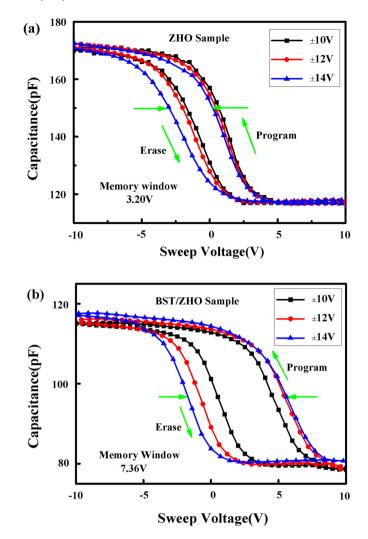

The memory device possess a single layer ZHO with a thickness of 35 nm and the double layers 15-nm BST/20-nm ZHO as the blocking layer and the charge trapping layer as schematic diagram in Fig. 1(a) and (b), respectively. The total thicknesses of two kinds of films keep the same. Fig. 2 demonstrates capacitance–voltage (C–V) curves of the samples annealed at 600 °C with different sweeping voltages at a high frequency (4 MHz). It is obvious that the memory windows increase with the increase of the sweeping voltage. ZHO sample shows a largest memory window of 3.2 V when the sweeping gate voltage is  $\pm 14$  V. However, the memory window of BST/ZHO sample reaches a largest value of 7.36 V at the same voltage, indicating a better charge storage capability. Here, the memory window in C–V curve is defined as the difference of the flat band voltages ( $V_{fb}$ ) between the program and erase states,

Fig. 2. The typical capacitance–voltage (C–V) curves of memory devices under different sweeping voltages (a) with single ZHO layer and (b) with BST/ZHO layers at 4 MHz.

which was measured by sweeping the voltage  $V_G$  from +14 V to -14 V and then back to +14 V.

To get the microstructure information in BST/ZHO memory device, HRTEM images were shown in Fig. 3. The thicknesses of three functional layers, SiO<sub>2</sub>, ZHO and BST, are about 3.50 nm, 21.3 nm and 15.5 nm which well correspond with our designing scheme. respectively. The inter-diffusion at the interface between the blocking layer BST and the trapping layer ZHO could be observed and the thickness of the interface layer is about 6.21 nm as shown Fig. 3(a). The effective inter-diffusion region where additional defect centers could be created during the inter-diffusion process is considered to be the main reason that improves the charge storage capability. So the inter-diffusion phenomenon at the interface BST/ZHO plays a significant role in modifying the charge trapping density in the memory devices. It is also observed that the tunneling layer SiO<sub>2</sub> shows amorphous structure and there is a narrow inter-diffusion region whose thickness is about 1.38 nm at the interface between the tunneling layer and the trapping layer as shown in Fig. 3(b). Just like the SiO<sub>2</sub> tunneling layer, this interdiffusion region also has a very important role in the charge retention characteristic of the memory devices.

Fig. 3(c) depicts that the blocking layer BST film is well crystallized with random orientations after RTA treatment. It is well seen that there are different nano-grains formations and the crys-

Download English Version:

## https://daneshyari.com/en/article/5497018

Download Persian Version:

https://daneshyari.com/article/5497018

Daneshyari.com