## ARTICLE IN PRESS

INTEGRATION the VLSI journal xxx (xxxx) xxx-xxx

ELSEVIER

Contents lists available at ScienceDirect

## INTEGRATION, the VLSI journal

journal homepage: www.elsevier.com/locate/vlsi

## An improved communication scheme for non-HOL-blocking wireless NoC

Yiming Ouyang<sup>a</sup>, Jianfeng Yang<sup>a,\*</sup>, Kun Xing<sup>b</sup>, Zhengfeng Huang<sup>b</sup>, Huaguo Liang<sup>b</sup>

- <sup>a</sup> School of Computer and Information, Hefei University of Technology, 193 Tunxi Road, Hefei 230009, China

- <sup>b</sup> School of Electronic Science & Applied Physics, Hefei University of Technology, 193 Tunxi Road, Hefei 230009, China

#### ARTICLE INFO

Keywords:

Wireless network-on-chip

WI congestion

VOQ scheme

Communication scheme

#### ABSTRACT

As the wireless interface often requires handling numbers of data simultaneously in wireless network-on-chip, it potentially causes data congestions. The degradation of wireless data transfer can tremendously reduce the efficiency of the network communication. In this paper, virtual output queuing (VOQ) technique has been used to eliminate the head-of-line blocking issue. Moreover, a novel and effective communication scheme has also been introduced to alleviate the traffic load in wireless nodes and hence improving the efficiency of wireless communication. Simulation results indicate that our proposed architecture is advantageous in various aspects including the transfer latency, network throughput and energy consumption.

#### 1. Introduction

Network-on-chip (NoC) has attracted significant attention and gradually become a promising paradigm for the on-chip interconnection of multi-core processors [1]. However, with the increase in the number of cores integrated in the chip, the growing communication delay and power consumption has caused severe problems for the on-chip interconnection. By inserting long-distance links in network, the average number of communication hops between cores and the communication delay of the entire network can be effectively reduced [2]. Nonetheless, according to the International Technology Roadmap for Semiconductors (ITRS) [3], as those links are still metal links, in the long run, the network performance has to be improved by applying new interconnection technologies in the future.

3D structure of the NoC has been proposed to improve the on-chip integration. Chips which are vertically stacked together greatly reduce the communication distance between cores [4]. For the optical interconnect, optical channel can provide the data communication with ultra-high bandwidth and low electromagnetic interference [5]. RF interconnection required an additional transmission medium, in which the data can be transferred to the destination approaching the speed of light [6]. However, these three technologies all have some technical or practical challenges which should be addressed [7].

Wireless Network-on-Chip (WiNoC) has been proposed in recent years, and by integrating wireless interface (WI) on chip, cores are able to achieve wireless interconnections [8]. WiNoC with millimeter (mm) -wave wireless links working at  $10-100\,\mathrm{GHz}$  with a transmission distance of 20 mm is a feasible choice to design architectures with

long-range, single-hop, energy efficient wireless interconnects [9]. Acting as the communication shortcuts, the wireless links added in the network can reduce the communication latency and transmission power consumption of the network. With the increase of the network traffic load, the number of data sent to WIs also rises. Once the amount of data exceeds the processing capacity of WI, it could possibly lead to hotspot situation in the WI [10]. Data congestion at the WI not only reduces the long-distance communication efficiency of the network, but also impedes the transmission of other data [11]. In this study, a novel WiNoC is designed using virtual output queuing (VOQ) routers, where an improved communication scheme is designed to alleviate the data congestion in the network and enhance the wireless resources utilization efficiency. Section 2 reviews the related works. In Section 3, the proposed communication scheme, router architectures and routing scheme are presented. Section 4 demonstrates the experimental results from cycle accurate simulation based on average hop count, normalized latency and normalized power consumption parameters. In the last section, a conclusion of this paper is made.

#### 2. Related work

#### 2.1. VOQ scheme

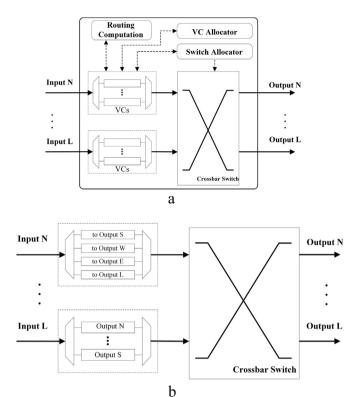

The conventional virtual-channel (VC) router is illustrated in Fig. 1a. The major components of the router include the input buffers, the routing computation logic, the VC allocator, the switch allocator and the crossbar switch. Buffer in each input port is divided into several VCs. In the VC router, the head-of-line (HOL) blocking may occur

E-mail address: jfyang0222@163.com (J. Yang).

http://dx.doi.org/10.1016/j.vlsi.2017.10.005

Received 17 February 2017; Received in revised form 4 July 2017; Accepted 10 October 2017 0167-9260/ © 2017 Published by Elsevier B.V.

<sup>\*</sup> Corresponding author.

Fig. 1. VC router architecture (a) and virtual output queuing scheme (b).

when the network latency increases, which seriously hinders the network performance. For the first in first out (FIFO) buffer queue in input port, if the first packet in the queue is blocked, all the other packets queuing behind it will also be blocked. VOQ scheme is proposed in Ref. [11] which can eliminate the HOL blocking phenomenon in network. Each input port in routers maintains a dedicated virtual-channel for each output shown in Fig. 1b. VOQ routers with a single queue for each output channel work well in low network load, but the performance will decline when the traffic load becomes heavy. To alleviate this problem, an efficient VOQ scheme named Multiple VOQ was proposed in Ref. [12], each input port can maintain more than one queue for each output channel.

#### 2.2. Wireless interconnection

In recent years, WiNoC is considered as a reasonable method to replace the traditional wire-based NoC, and the emergence of a variety of on-chip antennas makes it possible to achieve on-chip wireless communications. A WiNoC based on CMOS ultra wideband (UWB) technology was proposed [13], where 1 mm data transmission range can be achieved with the antenna length at 2.98 mm. In the WiNoC with the UWB technology, multiple-hops are required when the longdistance communication occurs. The feasibility of designing wireless interconnection with miniature antennas and simple transceivers has been proposed in Ref. [14], which can operate under the sub-THz frequency range of 100-500 GHz. With the increase of the frequencies the corresponding antenna sizes decrease correspondingly. The antenna based on carbon nanotubes (CNTs) has been demonstrated in Ref. [15], and its transmission frequencies can realize THz/optical range with the bandwidth of 10 Gb/s. However, due to the technical bottleneck of CNT integration, its implementation in WiNoC design was severely limited. Silicon integrated antenna working in the mm-wave range of 10–100 GHz is now a feasible technology for on-chip wireless communication [7].

Due to the long wireless transmission distance of the mm-wave based WiNoC (up to 8 mm), wireless channels formed by a few nodes can provide wireless communication within the whole network zone [16]. Considering the power consumption of the wireless component and the area overhead, such WiNoC structure seems to be more rational. As the wireless resource in WiNoC can greatly improve the performance of the network, increasing the utilization efficiency becomes a key issue of the WiNoC [17]. It is known that WI acts as the wireless resource portal for data access. With the increase of the network data load, it is possible that a number of data are accessing wireless resources via a single WI, resulting in data congestion at WI. Moreover, when the network load stays high, since there are more input and output port within the wireless routing nodes, the wireless port data are facing more pressure when they are competing for the output port. If the downstream wireless data receiver remains in the buffer area and cannot provide enough space for the upcoming wireless data, the upstream wireless routing nodes WI are likely to be congested. The existence of congestion situations will greatly impair the performance of network. Adaptive routing strategies can perceive the congestion information and balance the network load in WiNoC [18-20]. However, those strategies are excessive regard the load balance of the entire network and disregard the work efficiency of wireless resources, when treat wireless nodes in the same way as other nodes. Besides, the commonly used solution for WI congestion is known as the method of flow control. A credit-based flow control which was proposed in Ref. [21]. By judging whether the downstream nodes input buffer area is full, the wired signal flowing to congested nodes can be effectively avoided. A Feedback-based end-to-end congestion control scheme is proposed in Ref. [22], in order to alleviate the congestion issue by using information feedback and adjusting the size of the data and transmission rate using originating node. A token flow control is adopted in Ref. [10] to alleviate overloading at the WIs as many messages try to access the wireless shortcuts simultaneously. The above solutions can effectively avoid intensifying the congestion at the wireless nodes, but by controlling the visit from normal routing nodes to wireless routing nodes will to some extent restrict the utilization efficiency of the wireless resource. Therefore, we attach importance to decrease the influence caused by WI congestion, as well as improving buffer utilization efficiency of wireless routing node at wireless data receiving terminal in order to minimize possibility of the data congestion at upstream WI and hence improving the WiNoC performance.

In this paper, we establish a novel WiNoC architecture based on VOQ technology. The VOQ scheme is used to eliminate HOL blocking phenomenon caused by WI congestion. To mitigate the traffic load at the wireless nodes, we propose an improved communication scheme. Moreover, our routing strategy and the simplified pipeline stages are demonstrated.

#### 3. WiNoC architecture

#### 3.1. Topology

The WiNoC in this paper has a hierarchical structure, and the bottom mesh layer is homogeneously divided into subnets. In each subnet, a baseline router (BR) is replaced by a wireless router (WR) which implements with wireless interface (WI). Apart from sending and receiving data on wired links, WRs also acts as the upper wireless network layer. Fig. 2 shows a  $10 \times 10$  hierarchical hybrid wireless network architecture. The whole network is divided into four  $5 \times 5$  subnets, each of which has a WR responsible for long-distance data communication. Although increasing the number of WRs can reduce the latency of the network communication, excessive WRs can also result in extra hardware overhead and power consumption [23]. Therefore, WRs' number and layout is crucial for balancing network

### Download English Version:

# https://daneshyari.com/en/article/6942236

Download Persian Version:

https://daneshyari.com/article/6942236

**Daneshyari.com**