ELSEVIER

Contents lists available at ScienceDirect

## Microelectronic Engineering

journal homepage: www.elsevier.com/locate/mee

Research paper

## Metal work function engineering on epitaxial (100)Ge and (110)Ge metaloxide-semiconductor devices

Peter D. Nguyen, Michael B. Clavel, Aheli Ghosh, Mantu K. Hudait\*

Advanced Devices & Sustainable Energy Laboratory (ADSEL), Bradley Department of Electrical and Computer Engineering, Virginia Tech, Blacksburg, VA 24061, United States

ARTICLE INFO

Keywords: Germanium Metal-oxide-semiconductor Epitaxial Crystallographic orientation

#### ABSTRACT

Capacitance-voltage characterization of epitaxial n-type (100)Ge and (110)Ge metal-oxide-semiconductor capacitors (MOS-Cs) was performed using two work function Al and Pt gate metals to evaluate the orientation effect on flat-band voltage ( $V_{FB}$ ) shift, Fermi level pinning factor (S), and interface induced defects ( $D_{it}$ ). These epitaxial (100)Ge/AlAs/GaAs and (110)Ge/AlAs/GaAs heterostructures were grown in-situ using two separate molecular beam epitaxy (MBE) chambers. A  $V_{FB}$  shift of > 700 mV, S > 0.5, and  $D_{it}$  value of  $\sim$  6 × 10<sup>11</sup> cm<sup>-2</sup> eV<sup>-1</sup> in the energy range of 0.05 eV to 0.3 eV below the conduction band, have been demonstrated from epitaxial n-type (100)Ge and (110)Ge surfaces, which are comparable to the reported bulk Ge MOS-C values, suggesting a robust MOS-C developed process as well as device quality epitaxial (100)Ge and (110)Ge layers on GaAs substrates using an AlAs intermediate buffer. Thus, the metal work function engineering on device-quality MBE grown crystallographically oriented Ge materials, can offer a promising path for extending the performance and application of Ge-based field-effect transistors for low-power devices.

#### 1. Introduction

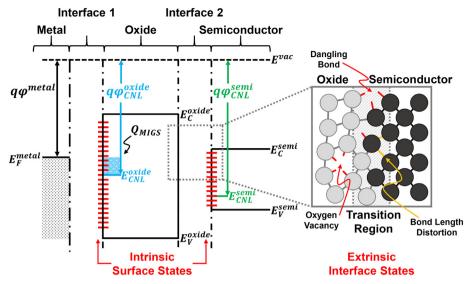

The replacement of polysilicon gates with metal gates in silicon (Si) metal-oxide-semiconductor field-effect transistors (MOSFETs) at the 45 nm transistor node has engendered a lot of interest in the metal work function engineering of MOSFETs [1] for continued transistor miniaturization. For *n*-channel and *p*-channel MOSFETs, two distinct gate metals are generally used to accommodate for the difference between the metal work function,  $\varphi_m$ , and the semiconductor work function,  $\varphi_s$ (which differs for n- and p-type channels),  $\varphi_{ms}$ .  $\varphi_{ms}$  has a direct impact on the flat-band voltage (VFB), which in turn affects the transistor threshold voltage ( $V_{TH}$ ). However, the ability to tune  $V_{FB}$  using two different work function metals in a metal-oxide-semiconductor capacitor (MOS-C) configuration, and consequently  $V_{TH}$ , is limited by Fermi-level pinning (FLP) at the semiconductor's surface. This FLP stems from the formation of a dipole layer, shown in Fig. 1, originating from intrinsic surface states that have been filled due to the presence of charged interfacial defects [2] at the oxide/semiconductor heterointerface. The formation of an additional dipole layer at the metal/ oxide heterointerface is also possible, corresponding to the well-described metal-induced gap states, i.e., the filled intrinsic oxide surface states resulting from the evanescent coupling of the metal electron wave function and available oxide surface states. [3, 4] The influence of these dipole layers depends on the cumulative difference between  $\varphi_m$  and the charge neutrality level  $\varphi_{CNL}$  at the semiconductor surface, as shown in Fig. 1, where  $E_{F,m}$  is the Fermi-level energy of the metal and  $E_{CNL}$  is the charge neutrality level (CNL) energy level, *i.e.*, the *effective* Fermi-level energy at the semiconductor surface. The interface dipole(s) that forms alters the interfacial band alignment, generating significant band bending at the semiconductor surface in order to equilibrate  $E_{CNL}$  and  $E_{F,m}$ , thereby altering  $\varphi_m$  and producing  $\varphi_{m,eff}$ , the effective metal work function.  $\varphi_{m,eff}$  can be expressed by the following: [5]

$$\varphi_{m,eff} = \varphi_{CNL} + S(\varphi_m - \varphi_{CNL}) \tag{1}$$

where S is known as the Schottky pinning parameter, which ranges from 0 (full pinning) to 1 (no pinning). If MOS-C's implementing different gate metals [5–7] are fabricated from the same oxide/semiconductor structure, the difference in flat-band voltage,  $\Delta V_{FB}$ , is now equivalent to the difference in  $\phi_{m,eff}$ , i.e.,  $\Delta \phi_{m,eff}$ . Correspondingly, Eq. (1) can be re-written in terms of  $\Delta V_{FB}$ , S, and the difference in effective metal work functions:

$$\Delta V_{FB} = \Delta \varphi_{m,eff} = S\Delta \varphi_m \tag{2}$$

In this work, the integration of two different gate metals, platinum (Pt) and aluminum (Al), to form MOS-Cs on (100) and (110) crystal-lographically oriented epitaxial Ge heterostructures grown by solid

E-mail address: mantu.hudait@vt.edu (M.K. Hudait).

<sup>\*</sup> Corresponding author.

Fig. 1. Schematic energy band diagram of a metal-oxide heterointerface and the intrinsic interface states that form due to differing charge neutrality levels (CNLs) between the dissimilar materials (adapted from Ref. [5]). It also illustrates the intrinsic and extrinsic surface states at each heterointerface.

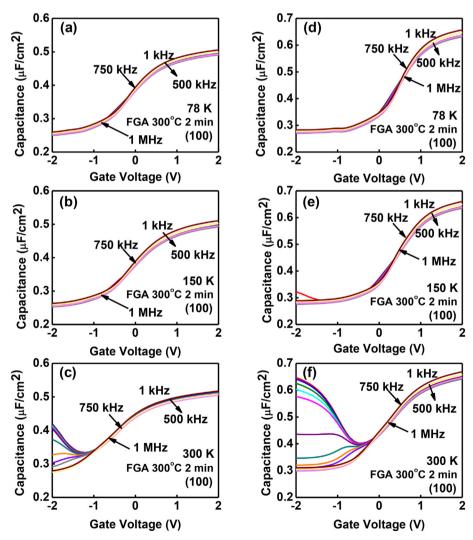

Fig. 2. C-V characteristics of the (100) Ge MOS-C on GaAs via an AlAs buffer architecture using two different gate metals. Devices with 100 nm Al/0.4 nm TiN measured at (a) 78 K (Ref. [10]), (b) 150 K and (c) 300 K. Devices with 60 nm Au/40 nm Pt/0.4 nm TiN measured at (d) 78 K, (e) 150 K and (f) 300 K.

### Download English Version:

# https://daneshyari.com/en/article/6942355

Download Persian Version:

https://daneshyari.com/article/6942355

<u>Daneshyari.com</u>