Contents lists available at ScienceDirect

## Microelectronic Engineering

journal homepage: www.elsevier.com/locate/mee

# Electrical characteristics of ALD $La_2O_3$ capping layers using different lanthanum precursors in MOS devices with ALD $HfO_2$ , $HfSiO_x$ , and HfSiON gate dielectrics

Donghwan Lim, Woo Suk Jung, Young Jin Kim, Changhwan Choi\*

Division of Materials Science and Engineering, Hanyang University, Seoul 133-791, Republic of Korea

#### ARTICLE INFO

Article history: Received 21 February 2015 Received in revised form 30 March 2015 Accepted 10 April 2015 Available online 16 April 2015

Keywords: High-k $V_{\rm FB}$  shift  ${\rm La_2O_3}$ Atomic layer deposition EOT

#### ABSTRACT

We have investigated the electrical characteristics – flat band voltage ( $V_{FB}$ ) shift, equivalent oxide thickness (EOT) scaling and charge trapping – of atomic layer deposition (ALD) La<sub>2</sub>O<sub>3</sub> capped high-k gate dielectrics (HfO<sub>2</sub>, HfSiO<sub>x</sub>, and HfSiON) in the metal-oxide-semiconductor (MOS) device structure, where two different lanthanum precursors – ① lanthanum formamidinate, La(fAMD)<sub>3</sub>, and ② lanthanum beta-diketonate, La(thd)<sub>3</sub>, – were used for ALD capping layer. Regardless of precursors, La<sub>2</sub>O<sub>3</sub> capping layer on the ALD high-k films leads to negative  $V_{FB}$  shift and thinner EOT as increasing capping thickness. However, more shift and further EOT scaling are observed with La<sub>2</sub>O<sub>3</sub> thin film using La(fAMD)<sub>3</sub>. In addition, La<sub>2</sub>O<sub>3</sub> capping layer using La(fAMD)<sub>3</sub> precursor shows lower interface state density ( $D_{it}$ ) and stronger immunity against charge trapping than La<sub>2</sub>O<sub>3</sub> capping layer with La(thd)<sub>3</sub> precursor. Similar trends are attained with Si containing HfO<sub>2</sub> – HfSiO<sub>x</sub> and HfSiON, but amount of  $V_{FB}$  shift and EOT reduction is smaller than that of HfO<sub>2</sub>-based device, resulting from suppressed La-diffusion due to stronger Si–O bonds as well as nitrogen blocking in the dielectrics.

Published by Elsevier B.V.

#### 1. Introduction

A successful adoption of high-k/metal gate (HKMG) technology into manufacturing logic devices with gate last process has driven further implementation into other applications such as dynamic random access memory (DRAM) [1]. Even though device requirement of peripheral transistors in DRAM is not as tight as in the logic transistor case, alternative material and process integration should be still considered to achieve low and symmetric threshold voltage  $(V_{TH})$  for advanced DRAMs because the peripheral transistor process is completed in advance, and subsequent capacitor fabrication steps including high thermal process could significantly degrade the properties of HKMG in peripheral transistors. Therefore, gate-first (GF) process is still cost-effective for DRAMs if solutions to suppress  $V_{\rm TH}$  roll-off, reduce leakage current and scale EOT are provided. Material-oriented solution using group IIA elements in the periodic table such as La can induce negative  $V_{\rm FB}$  shift (i.e., lower  $V_{\rm TH}$ ) for GF-nMOS device because diffused La elements through high-k gate dielectric cause dipole formation at the Si substrate and interfacial layer [2-5].

Several ALD precursors such as La(N(SiMe<sub>3</sub>)<sub>2</sub>)<sub>3</sub>, La(iPRADL)<sub>3</sub>, and La(iPrCp)<sub>3</sub> to deposit La<sub>2</sub>O<sub>3</sub> capping layer on the high-k gate dielectrics have been demonstrated with negative  $V_{\rm FB}$  shift and scaled EOT [6–9]. Electrical properties of n-channel MOS devices are substantially affected by ALD La precursor, gate dielectrics and process integration. Even though several studies on ALD La<sub>2</sub>O<sub>3</sub> capping layer have been reported, there are few reports on the systematic investigation on the effects of dielectrics, process temperature, and precursor on EOT and  $V_{\rm FB}$  in MOS devices.

We investigated the impact of ALD precursors on  $V_{\rm FB}$  shift, EOT scaling and charge trapping in the ALD La<sub>2</sub>O<sub>3</sub>-capped HKMG device structures. Our result suggests that besides process optimization, the precursor is also important to attain improved electrical properties of GF-based nMOS device applications.

#### 2. Experiment

After device isolation, interfacial layer (IL) was grown during the pre-gate clean step.  $HfO_2$ ,  $HfSiO_x$ , and HfSiON gate dielectrics were deposited by ALD using precursors (TEMAHf for Hf, TEMASi for Si), oxidant ( $H_2O$ ,  $O_3$ ), purging gas (Ar) and nitrogen source (NH<sub>3</sub>) for nitridation at a temperature in the range about 300 °C to 350 °C. ALD La<sub>2</sub>O<sub>3</sub> capping layer was prepared by La(fAMD)<sub>3</sub> and La(thd)<sub>3</sub> precursors. Some samples received sputtered La<sub>2</sub>O<sub>3</sub>

<sup>\*</sup> Corresponding author. Tel.: +82 2 2220 0383; fax: +82 2 2220 0389. E-mail address: cchoi@hanyang.ac.kr (C. Choi).

layer for comparison, where La was deposited first, followed by air exposure. Next, TiN gate electrode was DC-sputtered, followed by gate patterning and post metal annealing at various conditions. Final forming gas anneal (FGA) was carried out at  $400^{\circ}$ C for 15 min [10]. The electrical properties were characterized by capacitance voltage (C-V) measurement at a frequency of 100 kHz before and after FGA using an Agilent E4980A CV-meter and a HP 4145B parameter analyzer.  $D_{it}$  values were attained using the conductance method.

#### 3. Result and discussion

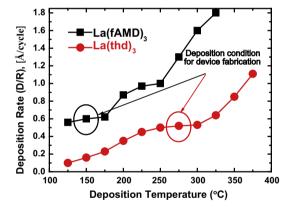

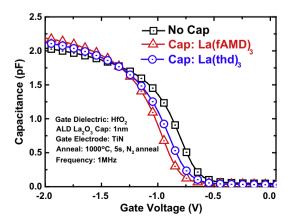

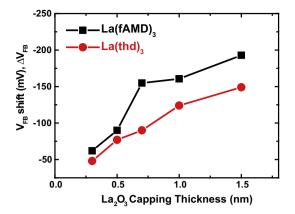

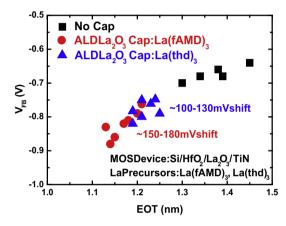

Considering growth rate behaviors as a function of various deposition temperatures, ALD La<sub>2</sub>O<sub>3</sub> deposition temperatures using La(fAMD)<sub>3</sub> and La(thd)<sub>3</sub> were chosen at 150 °C and 275 °C, respectively, as shown in Fig. 1. The C-V characteristics of MOS devices with 1 nm thick-ALD La<sub>2</sub>O<sub>3</sub>-capped HfO<sub>2</sub> gate dielectrics are shown in Fig. 2. Compared to non-capping device, negative  $V_{FB}$  shift and higher gate capacitance are observed at the devices with La<sub>2</sub>O<sub>3</sub>capping. Between two precursors, La(fAMD)<sub>3</sub>-based device shows more negative  $V_{\rm FB}$  shift as well as higher capacitance. Fig. 3 compares V<sub>FB</sub> shifts on HfO<sub>2</sub> as a function of ALD La<sub>2</sub>O<sub>3</sub> thickness. Regardless of precursors, increasing La<sub>2</sub>O<sub>3</sub> thickness induces more negative  $V_{FR}$  shift, but the shift using La<sub>2</sub>O<sub>3</sub> prepared by La(fAMD)<sub>3</sub> is more substantial. The correlation between EOT and V<sub>FB</sub> shift is presented in Fig. 4. Compared with non-La<sub>2</sub>O<sub>3</sub> capping, ALD La<sub>2</sub>O<sub>3</sub> capping induces negative V<sub>FB</sub> shift as well as EOT scaling. However, compared to  $La(thd)_3$  precursor, further  $V_{FB}$  shift (>50 mV) and EOT scaling (~0.1 nm) are attained with La(fAMD)<sub>3</sub>

Fig. 1. ALD deposition rate of  ${\rm La_2O_3}$  films using different precursors as a function of process temperature.

Fig. 2. C-V characteristics of MOS devices with La<sub>2</sub>O<sub>3</sub>-capped HfO<sub>2</sub>.

Fig. 3. V<sub>FB</sub> shift with increasing La<sub>2</sub>O<sub>3</sub> capping layer on the HfO<sub>2</sub> gate dielectric.

Fig. 4. The effects of La<sub>2</sub>O<sub>3</sub> capping and ALD La precursors on EOT vs V<sub>FB</sub> behaviors.

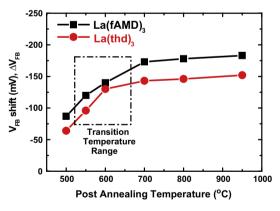

Fig. 5.  $V_{FB}$  shift as a function of post annealing temperatures on MOS capacitor with  $La_2O_3$ -capped HfO<sub>2</sub> gate dielectric.

precursor. These results are attributed to lower deposition temperature and different optimal oxidant pulse time. Fig. 5 shows  $V_{\rm FB}$  shifts as a function of various post annealing temperatures. It indicates that La diffusion becomes saturated over 700 °C irrespective of precursors, guiding a maximum process temperature through the whole process integration. La needs to be diffused into IL for the dipole formation, leading to  $V_{\rm FB}$  shift. This saturation of the  $V_{\rm FB}$  shifts with respect to process temperature suggests that the process temperature of the device integration containing La<sub>2</sub>O<sub>3</sub> capping layer can be lowered down to 700 °C. Regardless of precursors, increasing La<sub>2</sub>O<sub>3</sub> capping layer causes slight increase

### Download English Version:

# https://daneshyari.com/en/article/6943208

Download Persian Version:

https://daneshyari.com/article/6943208

<u>Daneshyari.com</u>