Contents lists available at SciVerse ScienceDirect

### Microelectronic Engineering

journal homepage: www.elsevier.com/locate/mee

# Stress in electroplated gold on silicon substrates and its dependence on cathode agitation $^{\,\,\!\!\!/}$

Suan Hui Pu\*, Andrew S. Holmes, Eric M. Yeatman

Department of Electrical and Electronic Engineering, Imperial College London, South Kensington Campus, London SW7 2AZ, UK

#### ARTICLE INFO

Article history: Received 12 December 2012 Received in revised form 21 April 2013 Accepted 28 May 2013 Available online 5 June 2013

Keywords: Gold electroplating Cathode agitation Residual stress

#### ABSTRACT

The influence of cathode agitation on the residual stress of electroplated gold has been investigated. Using a custom-built plating cell, a periodic, reciprocating motion was applied to silicon substrates that were electroplated with soft gold. A commercially available gold sulfite solution was used to deposit the  $0.6~\mu m$  thick gold films using a current density of  $3.0~m A/cm^2$  and a bath temperature of  $50~^{\circ}C$ . By increasing the speed of cathode agitation from 0 to 5 cm/s, the magnitude of the compressive stress decreased from -64~to -9~MPa. The results suggest that cathode agitation significantly alters the mass transport within the electrolytic cell and can be used as a method of stress control in gold electroplating. This finding is potentially significant for plating applications in microelectronics and microsystems that require precise stress control.

© 2013 The Authors. Published by Elsevier B.V. All rights reserved.

#### 1. Introduction

Electroplated gold is a widely used material in the microelectronic and microsystems industries [1,2]. For many applications, the properties of gold such as its high electrical conductivity, low hardness and resistance to oxidation are often advantageous. For example, transmission lines in microwave integrated circuits are typically fabricated using gold to reduce signal attenuation [3]. In electronic assembly, soft gold is important for wire bonding and innovative flip-chip assembly [4,5]. Conversely, for applications such as electrical connectors or switch contacts, gold deposits with high hardness are important for achieving good wear resistance [2]. Relative to other deposition methods such as evaporation or sputtering, electroplating gives higher deposition rates and is particularly well suited to depositing thick films that are up to a hundred microns thick. In addition, a patterned photoresist mold is typically used in gold electroplating for microelectronic applications. This reduces material wastage since only the exposed device areas are deposited with gold whereas physical vapour deposition methods involve blanket deposition, followed by patterning using lift-off or etching using a photoresist mask. Another advantage of gold electroplating is that a wide range of gold electrolytes are available commercially, allowing the physical

E-mail address: suanhui.pu@soton.ac.uk (S.H. Pu).

properties of the gold deposit such as hardness, roughness and stress to be tailored.

For most gold plating processes, the deposits contain residual stresses that can be either compressive or tensile, depending on the plating parameters. Stress control in gold plating is particularly critical in applications such as mask fabrication in X-ray lithography [6-10]. X-ray lithographic masks consist of gold absorber patterns deposited on thin membranes only a few microns thick [6,9]. As the gold layer can be up to one micron thick, residual stresses can result in significant bending moments, causing mask distortion and poor pattern transfer. For radio frequency MEMS (micro-electromechanical systems) applications, fixed-fixed beam structures are often employed as switches [11]. An increase in the switching voltages can occur when a severe state of residual tension is built into the beams. This causes a stiffening effect and results in a deviation from designed switching voltages. Residual stress control in gold films can also be used to fabricate curved, electrostaticallyactuated electrodes [12,13]. For example, a curved cantilever electrode can be achieved using a bilayered gold-copper structure [13]. The gold bottom layer is electroplated using a relatively stress-free process while the top copper layer is deposited with residual tension.

In previous work, the stress of electroplated gold has been reported as a function of plating current density [6–8,10,14], bath temperature [8,10], film thickness [6,8], pulsed-current plating [6,9,14], and the addition of brighteners such as arsenic [14] or thallium [10]. In this work, the influence of direct cathode (substrate) agitation on stress in soft, pure gold is studied experimentally. In all forms of electroplating, mass transport plays a key role in the properties of the electroplated film [15]. To obtain electrolyte mixing and ion replenishment in the vicinity of the

<sup>\*</sup> This is an open-access article distributed under the terms of the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original author and source are credited.

\* Corresponding author. Present address: University of Southampton (USMC), No.

<sup>3,</sup> Persiaran Canselor 1, Kota Ilmu Educity @ Iskandar, 79200 Nusajaya, Johor, Malaysia. Tel.: +60 7 560 2 461.

wafer, commercial plating baths employ continuously pumped electrolytic cells that are filtered using submicron filters. In laboratory plating equipment, electrolyte agitation is often induced using magnetic stirrers in small scale plating cells. The use of periodic, reciprocating cathode agitation as a means of enhancing mass transport in gold electroplating has not been explored systematically. Our results suggest that the residual stress in electroplated gold can be controlled by adjusting the speed of cathode agitation.

#### 2. Experimental details

A commercially available gold sulfite solution (Metalor ECF 60) was used for the electroplating experiments. For microelectronic applications, sulfite-based gold plating solutions offer better compatibility with positive photoresists relative to cyanide-based solutions [14,16,17]. Gold cyanide solutions tend to attack positive photoresists, causing underplating at the interface between the resist and the seed layer. Due to the limitations in pattern transfer quality, cyanide-based solutions are seldom employed in microelectronics fabrication. In the experiments, the pH of the gold sulfite solution was maintained at 9.5 and no brightener or grain refiner was added to the solution. Soft gold was deposited on silicon substrates that were pre-coated with a gold seed layer. The stress of the electroplated gold was then measured for a range of cathode agitation speeds, plating temperatures and current densities.

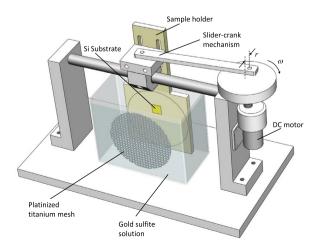

#### 2.1. Cathode agitation

Previously, the effect of cathode vibration (in a direction parallel to the anode) on mass transport has been studied in copper electrolytic cells [18,19]. For vibration amplitudes up to 8 mm and frequencies up to around 50 Hz, the results showed a significant increase in the mass transfer coefficient. In order to enhance mass transport in gold electroplating, a custom-built electroplating cell that allows periodic cathode agitation was used in the current work [20]. As shown in Fig. 1, the samples were mounted on a polypropylene sample holder that was attached to a reciprocating slider–crank mechanism. A platinised titanium anode was mounted parallel to the cathode and a separation of 40 mm was maintained between the electrodes.

Cathode agitation was achieved using a DC motor to actuate the slider-crank mechanism. The instantaneous linear velocity of the sample is sinusoidal and given by

$$v \approx r\omega \sin(\omega t)$$

(1)

Fig. 1. Electroplating cell with reciprocating cathode agitation.

where  $\it r$  and  $\it \omega$  are the radius and angular velocity of the crank, respectively. The corresponding root mean square speed of the sample is

$$v_{\rm rms} \approx \frac{r\omega}{\sqrt{2}}$$

(2)

#### 2.2. Stress measurement

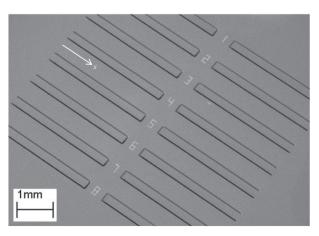

The stress in the electroplated gold was measured using silicon cantilevers fabricated on 4-inch silicon-on-insulator (SOI) wafers. For the experiments, the silicon wafers were diced into smaller chips with 16 cantilevers per chip. Each cantilever is 3000  $\mu m$  long, 200  $\mu m$  wide and 20  $\mu m$  deep. The edges of the cantilevers are aligned with the Si <100> lattice directions. A thin, 150 nm gold seed layer is sputtered onto the top surface of the cantilever prior to gold electroplating. Fig. 2 shows a typical chip with the silicon cantilevers for stress measurement.

The height of each cantilever tip was measured relative to the chip surface before and after gold electroplating. Cantilever height measurements were made using a Veeco Wyko NT9100 white light interferometer. A typical Wyko scan is shown in Fig. 3, where the positions A and B indicate the cantilever tip and the rigid chip surface, respectively. The difference in the initial and final cantilever heights gives the vertical displacement,  $\delta$  due to the stress in the gold film.

For a given film stress, the curvature induced in the cantilever beam can be expressed using Stoney's equation [21], since the thickness of the gold deposit is much smaller than the thickness of the cantilever. Hence, the curvature is given by

$$\kappa \approx \frac{6h_f \sigma_f (1 - \nu_s)}{E_s h_s^2} \tag{3}$$

where  $h_f$  and  $\sigma_f$  are the thickness and stress of the plated gold, respectively.  $E_s$ ,  $h_s$  and  $v_s$  are the Young's modulus, thickness and Poisson's ratio of the cantilever, respectively. The factor  $(1-v_s)$  in Eq. (3), which is not present in Stoney's original formula, is due to the fact that the stress in the gold film is biaxial in nature [22]. Stoney's original formula assumed that the film stress is uniaxial. For displacements that are small relative to the cantilever length L,

$$\frac{\partial^2 \delta}{\partial x^2} \approx \kappa \tag{4}$$

and the boundary conditions for the built-in end are

Fig. 2. Silicon cantilevers fabricated using an SOI process.

#### Download English Version:

## https://daneshyari.com/en/article/6943771

Download Persian Version:

https://daneshyari.com/article/6943771

<u>Daneshyari.com</u>