FISEVIER

Contents lists available at ScienceDirect

## **Electric Power Systems Research**

journal homepage: www.elsevier.com/locate/epsr

# A method for the assessment of the optimal parameter of discrete-time switch model

R. Razzaghi\*, C. Foti, M. Paolone, F. Rachidi

École Polytechnique Fédérale de Lausanne, 1015 Lausanne, Switzerland

#### ARTICLE INFO

#### Article history: Received 15 November 2013 Received in revised form 13 January 2014 Accepted 10 February 2014 Available online 16 March 2014

Keywords: Discrete-time switch model Modified nodal analysis Fixed admittance matrix nodal method Real-time simulations

#### ABSTRACT

This paper proposes a novel method for the optimal parameter selection of the discrete-time switch model used in circuit solvers that adopt the fixed admittance matrix nodal method (FAMNM) approach. As known, FAMNM-based circuit solvers allow to reach efficient computation times, in particular for real-time simulation applications, since they do not need the inversion of the circuit nodal admittance matrix. However, these solvers need to optimally tune the so-called discrete switch conductance, since this parameter might largely affect the simulations accuracy. Within this context, we propose a method for the determination of the discrete-time switch conductance which is obtained by minimizing the distance between the eigenvalues of the original circuit's nodal admittance matrix with those associated with the circuit including the discrete-time switches. The method is proven to provide values of the discrete-time switch conductance that maximize the simulation accuracy and minimize the losses on this artificially introduced parameter. Additionally, the proposed method avoids the use of trial-and-error process typically required when discrete-time switch conductances need to be addressed in FAMNM approach. The performances of the proposed method are demonstrated for circuits with single and multiple switches in which passive RLC elements and transmission lines are both considered.

© 2014 Elsevier B.V. All rights reserved.

#### 1. Introduction

Accurate and computationally efficient time-domain simulation of power systems including switches (such as traditional circuit breakers or power electronic devices), is a challenging subject since the tradeoff between accuracy and computation time depends on the adopted models of the switching devices, especially when real-time constraints need to be achieved.

Detailed switch models reproducing their physical properties are used when studying phenomena such as switching losses, arcing times and electromagnetic transients associated with switching-arc extinction. However, in many power systems applications, these sophisticated models cannot be used because of their required computational efforts and complexity of implementation. As a result, simplified switch models have been proposed in the literature (e.g. [1,2]).

One of the most popular methods consists in representing switches as lumped electrical components. The simplest approach is the so-called two-valued resistor model where two resistors, characterized by large differences of their resistance values, are associated with each state of the switch. The typical representation consists in replacing the switch by a resistor characterized by a "small" value of resistance for the "closed-state" and a "large" value for the "open-state". However, in this case the system's admittance matrix needs to be updated and re-factorized after each switching state change (e.g. [3,4]).

Within the context of real-time simulations, updating the admittance matrix imposes additional computational burden to the solution algorithms that need to be executed within a determined time window. As a consequence, the admittance matrix re-factorization represents a major obstacle to satisfy the computational constraints.

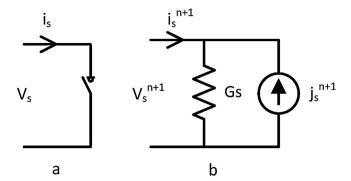

A possible approach to circumvent this problem is the use of modeling techniques that keep the system admittance matrix constant (e.g., [5,6]). To this end, discrete circuit models for switching devices were proposed in [1,7,8]. The basic idea is that the switch could be represented by a relatively small inductance when its state is 'closed' and by a relatively small capacitance when its state is 'open'. As a consequence, the discrete-time switch model is represented by an equivalent conductance  $(G_s)$  in parallel with a current source controlled by the so-called history term (e.g., [4]). The consequence of such a representation is an approach called fixed admittance matrix nodal method (FAMNM) [9]. In the FAMNM, the discrete-time switch conductance  $G_s$  is kept constant during

<sup>\*</sup> Corresponding author. Tel.: +41 216934815; fax: +41 216934662. E-mail address: reza.razzaghi@epfl.ch (R. Razzaghi).

switches state-transitions, the change of the switches state affects only the value of the current source which does not appear in the circuit admittance matrix. On the other hand, such a switch representation introduces artificial transients [2,5].

Solutions to solve this problem have been proposed in the literature. In particular, a damping resistance can be added in series to the discrete-time switch model [10]. However, this approach poses the problem of the optimal choice for the value of such a damping resistance as well as the inclusion of artificial losses into the system.

A different approach to solve this problem is the optimal selection of the  $G_s$  parameter. One possibility is to consider an a priori value for  $G_s$  and, then, find the corresponding optimal value by comparing the simulation results with benchmark ones in order to minimize the relevant errors [2] (i.e., obtained by off-line simulations where the switches are represented by ideal devices). However, such a trial-and-error approach provides solutions that require specific and time consuming assessments in which the uniqueness of the solution is not guaranteed.

The authors of this paper have presented a preliminary analysis in [11] on the possibility of finding the optimal discrete-time switch  $G_s$  conductance by solving a suitable optimization problem. The current paper aims at discussing more in detail the method presented in [11], and providing its extension to the case of systems with multiple switches. Specifically, the proposed method is based on the minimization of the Euclidian distance between the eigenvalues of the FAMNM-based network admittance matrix and those associated with the admittance matrices of the reference networks corresponding to all possible switches permutations where the switches are represented by ideal ones. It is worth noting that, compared to the existing methods that rely on the extensive and numerous trial-and-error simulation studies, the proposed method allows to reduce the computations required to find the optimal discrete-time switch  $G_s$  conductance.

The structure of the paper is as follows: Section 2 summarizes the formulation of the FAMNM. Section 3 describes the problem definition. Section 4 presents the proposed method to find the optimum values for the conductance of the discrete-time switches generalized to the case of systems with multiple switches. Section 5 presents the validation of the proposed method by making reference to three examples. Finally, Section 6 concludes the paper with the final remarks and potential implementation of what discussed in the paper.

#### 2. FAMNM representation of the switch

The idea of FAMNM is the discrete-time representation of the switch with a constant impedance model [1,7–9]. Such an approach assumes that the equivalent model of the ideal switch is piecewise linear and could be represented by a capacitance when it is open and an inductance when it is closed. The inductance and capacitance are represented, in a discrete form, by a conductance in parallel with a current source. In order to set the value of the conductance for both switch states, in case the backward Euler numerical integration method is used, the following constraint should be satisfied:

$$G_{\rm S} = \frac{C_{\rm S}}{\Delta t} = \frac{\Delta t}{L_{\rm S}} \tag{1}$$

where  $C_s$  and  $L_s$  are the discrete-time switch capacitance and inductance respectively, and  $\Delta t$  is the simulation time-step. For other numerical integration methods, a similar approach could be applied to relate  $G_s$  to the switch capacitance and inductance. It is worth observing that Eq. (1), with different analytical forms, holds also in case other numerical integration techniques are used [1].

As a consequence of this representation, the relevant model is composed of a constant conductance in parallel with a current

**Fig. 1.** Ideal switch (a) and corresponding discrete-time model (b). *Source*: Adapted from [1].

source (see Fig. 1). As a function of the switch on/off state, the value of the current source  $(j_s^{n+1}$  in Fig. 1) is updated at each time-step based on the switch current/voltage. The advantage of this method is that the value for the switch conductance  $G_s$  is fixed irrespective of the switch on/off state. As a result, the nodal admittance matrix will remain unchanged during switching operations as the switch state only affects the value of the shunt current source. The current source associated with the switch at the simulation step n+1 is defined as [1]:

$$J_{S}^{n+1} \begin{cases} -i_{S}^{n} & \text{for the 'on' state} \\ G_{S}v_{S}^{n} & \text{for the 'off' state} \end{cases}$$

(2)

According to [1], one approach for determining the value of  $G_S$  is to select  $C_S$  and  $L_S$  equal to the corresponding real switch parameters. Then, the values of  $G_S$  and  $\Delta t$  could be determined using (1). However, the main drawback of this approach is that the required simulation time step might become extremely small resulting in prohibitive computational times.

As already stated in the introduction, a different procedure refers to the assessment of an optimal  $G_S$  value by means of a trial-and-error process where benchmark results are obtained by means of off-line simulations carried out by adopting ideal switches. However, such an approach requires non-negligible pre-computational efforts.

#### 3. Discrete-time representation of electrical systems

Generally, there are two main types of solution methods currently used in the field of power system, power electronics and electronic circuit simulations [12]: (i) modified nodal analysis (MNA) and (ii) state-space (SS) approach. In this study, in order to formulate the network equations, MNA has been selected similarly to [1]. This choice is supported by the fact that the MNA provides a straightforward way of directly integrating the above illustrated discrete-time switch model.

As known, the MNA formulation is expressed as follows:

$$[A_n][x_n] = [b_n] \tag{3}$$

where matrix  $[A_n]$ , in the discrete-time domain, is formed by the discrete representation of the network elements;  $[x_n]$  is the vector of unknown network's node voltages and branch currents; and  $[b_n]$  is a vector composed of the independent sources and current history terms related to the network components. At each iteration, the unknown vector  $[x_n]$  is calculated and, then, the vector  $[b_n]$  is updated. As already mentioned, representing switches with FAMNM allows to keep  $[A_n]$  fixed during switching transitions.

In order to solve Eq. (3) in discrete-time, a suitable numerical integration method should be used. Among the several methods available, backward Euler and the trapezoidal methods are the

### Download English Version:

# https://daneshyari.com/en/article/705040

Download Persian Version:

https://daneshyari.com/article/705040

<u>Daneshyari.com</u>