FISEVIER

Contents lists available at ScienceDirect

#### Materials Science in Semiconductor Processing

journal homepage: www.elsevier.com/locate/mssp

## A bilayer graphene nanoribbon field-effect transistor with a dual-material gate

Hadi Owlia\*. Parviz Keshavarzi

Electrical and Computer Engineering Department, Semnan University, Semnan, Iran

#### ARTICLE INFO

# Keywords: Bilayer graphene nanoribbon field-effect transistor (BLGNRFET) Dual-material gate (DMG) Short-channel effects (SCEs) Nonequilibrium Green's function (NEGF)

#### ABSTRACT

This paper introduces dual-material gate (DMG) configuration on a bilayer graphene nanoribbon field-effect transistor (BLGNRFET). Its device characteristics based on none-quilibrium Green's function (NEGF) are explored and compared with a conventional single-material gate BLGNRFET. Results reveal that an on-off ratio of up to 10 is achievable as a consequence of both higher saturation and lower leakage currents. The advantages of our proposed DMG structure mainly lie in higher carrier transport efficiency by means of enhancing initial acceleration of incoming carriers in the channel region and the suppression of short channel effects. Drain-induced barrier lowering, subthreshold swing and hot electron effect as the key short channel parameters have been improved in the DMG-based BLGNRFET.

© 2015 Elsevier Ltd. All rights reserved.

#### 1. Introduction

Nowadays, there is much excitement in the low-energy electronic properties of sp<sup>2</sup> carbon allotropes including graphene monolayers and bilayers [1–7]. Coupling of the two monolayer graphene sheets in accordance with AB (or Bernal) stacking is the most energetically favorable relative arrangement and has also been observed in crystalline graphite [8]. The bandstructure in the bilayer garphene represents hyperbolic dispersion at the six corners of Brillouin zone, so-called a Mexican hat structure [9,10]. It turns out that charge carriers in transport near Fermi level behave like massive quasiparticles with a finite density of state at zero energy.

The lack of a natural bandgap in pristine graphene reveals some challenges for using in electronic devices

E-mail addresses: hadi.owlia@gmail.com, hadi.owlia@semnan.ac.ir (H. Owlia), pkeshavarzi@semnan.ac.ir (P. Keshavarzi).

nanoribbons (GNRs) show a reciprocal relationship between the energy bandgap and ribbon width [13]. Typically, gaps larger than 1 eV can be achieved by the widths below 2 nm [14]. In existing device technologies, preparing GNRs associated with well-defined edges faces considerable fabrication challenges when the ribbon width approaches 1-2 nm [15]. It is shown that a gate-induced electric field, which is applied perpendicularly to a bilayer graphene (BLG) surface, opens a bandgap at the charge neutrality point [16]. First principle calculations confirm that both the strength of the electric field and the BLG width are efficiently able to modulate the observed energy gap [16,17]. Hence, using bilayers instead of monolayers can obtain larger gaps at the same width. It is worth mentioning that bandgap in such BLGs still is not comparable to its silicon counterparts leading to a meaningful distance between the on-off ratio of the both technologies. However, the usage of a new computational paradigm

based on intrinsic negative differential resistance rather

[11]. A simple way of opening an energy gap is by lateral quantum confinement which can be induced by patterning a few nm width graphene ribbons [11,12]. The graphene

<sup>\*</sup> Corespondence to: Electrical and Computer Engineering Department, Semnan University, Semnan, 3513119111, Iran. Tel.: +98 2333383994.

than classical approach can circumvent the raised problem in graphene FETs [18,19].

As device pitch shrinks and is particularly downscaled below 100 nm, short channel effects (SCEs) becomes considerably crucial in device characteristics [20]. To suppress these undesirable effects, some techniques such as different gate insulators, electrically-activated source extension and utilizing high- $\kappa$  dielectrics have been presented [21–23]. Another interesting approach which is commonly used in well-known device designs is called "gate material engineering". Dual-material gate (DMG) structure of a conventional silicon MOSFET, silicon-on-insulator MOSFET (SOI-MOSFET), carbon nanotube field-effect transistor (CNTFET) and junctionless nanowire transistor (INT) are some early examples of such work [24-27]. Appling the DMG configuration is an efficient approach to enhance immunity against SCEs. In this approach, two gate metals with different work functions, which are laterally merged together, are employed to minimize the sensitivity of source-side barrier from drain potential variation. It is found that this configuration not only reduces short channel effects but also improve gate transport efficiency. In general, carrier transport in MOSFETs starts with a low initial velocity and is gradually accelerated towards the drain end. Relatively slow carrier drift velocity in the channel near the source region can be increased by the DMG configuration resulting in higher average velocity. This is caused by adjusting the electric field distribution and potential profile along the channel. Although this configuration has recently been applied to a monolayer graphene FET [28], exploiting its advantages in bilayer garphene would make the device more reliable as mentioned before. In this paper, we present a dual-material gate bilayer graphene nanoribbon field-effect transistor which combines the advantages of a BLGNRFET with DMG configuration.

The paper is organized as follows: Section 2 introduces the device structure and geometry. In this section, the performed simulation approach incorporating Schrodinger and Poisson equations is described as well. Section 3 deals with a discussion on results and illustrations. Finally, concluding remarks are outlined in the last section.

#### 2. Approach

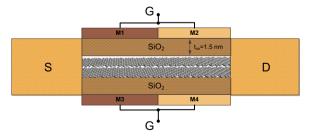

The sketch of a double-gate BLGNRFET wherein each gate consisted of dual materials with different work

Fig. 1. Dual-material gate bilayer graphene nanoribbon field-effect transistor.

functions is demonstrated in Fig. 1. The work function is defined as the separation between vacuum level and Fermi level. Here, the metals near source side have a higher work function over those near drain side, i.e.,  $\Phi_1 = \Phi_3 = 4.7$  eV and  $\Phi_2 = \Phi_4 = 4.4$  eV. A 10-nm-long N = 12 armchair-edge BLG surrounded by 1.5-nm top and bottom  $SiO_2$  dielectric layers ( $\kappa = 3.9$ ) forms the channel region. Source and drain contacts are made from the extensions of the BLG channel. Albeit the channel material is dopant-free, the source and drain regions are uniformly doped with an n-type doping concentration of 0.01 dopant per carbon atom.

Tight-binding approximation is used to describe atomic details of the BLG channel [29,30]. This approach is a well-known model to obtain an effective Hamiltonian of the channel through fitting the band structure derived from ab initio calculations. The elements of the Hamiltonian matrix are composed of on-site potentials at the carbon atoms of a BLG unit cell and hopping parameters including nearest neighbor interactions.

In simulation procedure, there is a suitable coupling between bandstructure/density of state with the NEGF formulation for quantum transport and full 3D Poisson's equation for electrostatics [31]. Once the Hamiltonian and self-energy matrices incorporating boundary conditions from source/drain contacts are known, carrier concentration of the BLG channel is determined through computing the NEGF formalism and arranged in a density matrix. The concentration is entered into the Poisson's equation so as to calculate potential profile along the channel. The resultant representing the applied gate voltage and any change in the density matrix from a reference condition is thought of as a new input in the NEGF formalism. A self-consistent iterative scheme is performed until the results yield reasonably good convergence. In the whole simulation procedure, thermal conditions are assumed to be fixed at room temperature.

#### 3. Results and discussion

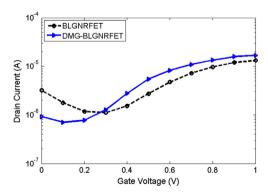

This section evaluates the performance of the DMG configuration on the MOSFET-like BLGNRFET. In the following discussion, dual-material gate and conventional MOSFET-like BLGNRFETs are respectively abbreviated as DMG-BLGNRFET and BLGNRFET. Fig. 2 illustrates the

Fig. 2. Transfer characteristics of the simulated device structures at  $V_{\rm DS}{=}0.5\,{\rm V}.$

#### Download English Version:

### https://daneshyari.com/en/article/7119156

Download Persian Version:

https://daneshyari.com/article/7119156

<u>Daneshyari.com</u>