Solid-State Electronics 116 (2016) 22-29

Contents lists available at ScienceDirect

Solid-State Electronics

journal homepage: www.elsevier.com/locate/sse

### SOLID-STATE ELECTRONICS Ar international Journal

# DC sputtered amorphous In–Sn–Zn–O thin-film transistors: Electrical properties and stability

Mitsuru Nakata<sup>a,b,1</sup>, Chumin Zhao<sup>a,1</sup>, Jerzy Kanicki<sup>a,\*</sup>

<sup>a</sup> Solid-State Electronics Laboratory, Department of Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, MI 48109, USA <sup>b</sup> NHK Science and Technology Research Laboratory, Setagaya, Tokyo 157-8510, Japan

#### ARTICLE INFO

Article history: Received 19 June 2015 Received in revised form 6 November 2015 Accepted 10 November 2015

Keywords: Thin-film transistors Amorphous In–Sn–Zn–O Field-effect mobility Electrical stability

#### 1. Introduction

In the past decade, thin-film transistors (TFTs) based on amorphous oxide semiconductors, especially amorphous In–Ga–Zn–O (a-IGZO), have been intensively studied [1–4]. The relatively high field-effect mobility ( $\mu_{eff} \sim 10 \text{ cm}^2/\text{V}$  s) of a-IGZO TFTs, in compassion to that of hydrogenated amorphous silicon (a-Si:H) TFTs, is a desirable property for next generation high-resolution, or high frame rate active-matrix flat-panel displays (AM-FPDs) [5,6]. However, the mobility of a-IGZO TFTs is still not sufficient to drive ultra-high resolution (UHR) (e.g. 8 k × 4 k) AM-FPDs at a high frame rate (>240 fps). At the same time, the electrical stability of a-IGZO TFTs needs to be further improved for mass production of UHR displays [7].

Recently, amorphous In–Sn–Zn–O (a–ITZO) TFTs with a boosted  $\mu_{\rm eff}$  of ~30 cm<sup>2</sup>/V s, threshold voltage ( $V_{\rm T}$ ) of ~1 V, and subthreshold swing (*SS*) of <0.3 V/dec have attracted much attention as an alternative to a-IGZO TFTs [7–10]. Ryu et al. reported that the device properties such as  $V_{\rm T}$  and *SS* are highly related to the Sn/(In + Sn + Zn) ratio, while improved device stability was achieved by increasing the Sn/Zn ratio [11,12]. It was also reported that the electron effective mass ( $m_{\rm e}^*$ ) in a-ITZO varies from 0.23 to 0.28  $m_{\rm e}$  by changing the ratio of (In + Sn + Zn) [13]. The obtained a-ITZO  $m_{\rm e}^*$  is smaller than that of a-IGZO (0.34  $m_{\rm e}$ ) [14], indicating

#### ABSTRACT

In this study, we investigated the electrical properties of DC sputtered amorphous In–Sn–Zn–O (a-ITZO) thin-film transistors (TFTs) fabricated under various process conditions. Fabricated a-ITZO TFTs achieved a threshold voltage ( $V_T$ ) of 1.0 V, subthreshold swing (SS) of 0.38 V/dec and field-effect mobility ( $\mu_{eff}$ ) of around 30 cm<sup>2</sup>/V s. An analytical field-effect mobility model is proposed for a-ITZO TFTs with key parameters extracted using different methods. The impacts of a-ITZO thin-film transition of device performance were evaluated. Finally, the a-ITZO TFT bias-temperature stress (BTS) induced electrical instability was studied. In comparison to amorphous In–Ga–Zn–O (a-IGZO) TFTs, improved electrical stability was observed for a-ITZO TFTs using exactly the same BTS conditions.

increased field-effect mobility. In addition, the average interatomic distance between the In/Sn atoms in a-ITZO was found to be around 3.59 Å at (In + Sn)/(In + Sn + Zn) = 67%, which is smaller than the In atom interatomic distance in a-IGZO (4.35 Å, In/(In + Ga + Zn) = 33%) [13]. The closer In/Sn interatomic distance is expected to enhance the overlaps between In-5s and Sn-5s atomic orbitals resulting in increased conduction band mobility. The a-ITZO TFT electrical properties such as field-effect mobility need to be carefully studied. The impacts of process conditions on device parameters and electrical instability should be characterized.

In this work, we fabricated DC sputtered a-ITZO TFTs and optimized the process conditions. The normalized weight ratio of our a-ITZO target is  $In_2O_3$ :ZnO:SnO<sub>2</sub> = 1:2.67:1.24. The voltagedependent field-effect mobility of a-ITZO TFTs were investigated with parameters extracted using two different analytical methods. We also studied the impacts of channel thickness and oxygen gas flow ratio on device performance. Finally, the electrical stability of a-ITZO TFTs under positive and negative BTS was evaluated and compared with that of a-IGZO TFTs.

#### 2. Experimental

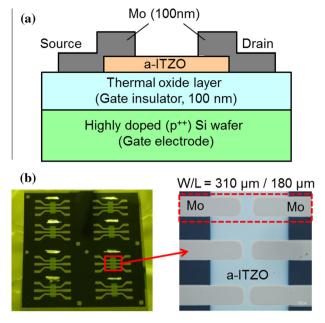

Fig. 1 shows the cross-sectional and top views of the fabricated a-ITZO TFT by shadow masks to avoid influence of the photolithography steps on a-ITZO channel optimization. We used highly doped  $(p^{++})$  silicon wafers with a 100 nm thermal oxide  $(SiO_2)$  layer as the substrate. The highly doped silicon and thermal oxide acted as the gate electrode and gate insulator, respectively. The a-ITZO film was

<sup>\*</sup> Corresponding author. Tel.: +1 (734) 936 0964; fax: +1 (734) 615 2843. *E-mail address:* kanicki@eecs.umich.edu (J. Kanicki).

Fig. 1. (a) Cross-sectional and (b) top views a-ITZO TFTs fabricated using mechanical mask.

deposited on the substrate by DC sputtering in a mixture of Ar/O<sub>2</sub> gases at a pressure of 0.53 Pa and a DC power density of 3.1 W/cm<sup>2</sup>. The O<sub>2</sub> gas flow ratio (O<sub>2</sub> gas flow rate/(Ar gas flow rate +O<sub>2</sub> gas flow rate) × 100%) was varied from 0% to 50%, while the pressure was kept constant. After the a-ITZO deposition, the a-ITZO film was annealed at 350 °C for 30 min. Then molybdenum (Mo) was DC sputtered as the source/drain (S/D) electrodes. Shadow masks were used to pattern the a-ITZO channel and S/D electrodes. Finally, fabricated TFTs were annealed again at 300 °C for 30 min. The channel width (*W*) and length (*L*) of the shadow mask TFTs were measured to be 310 and 180 µm, respectively. No passivation layer was used to the device structure.

#### 3. Results and discussion

#### 3.1. Electrical properties of shadow mask a-ITZO TFTs

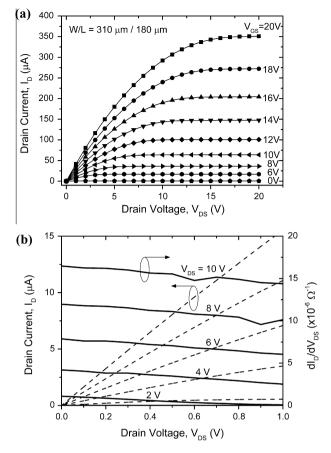

Fig. 2(a) shows the output characteristics of a-ITZO TFT under various gate-to-source voltages ( $V_{GS}$ ) ranging from 0 to 20 V. The O<sub>2</sub> gas flow ratio and a-ITZO thickness were 5% and 50 nm, respectively. A clear distinction between linear and saturation regions was observed. Fig. 2(b) represents the detail of the output characteristics for small drain-to-source voltage ( $V_{DS}$ ) ranging from 0 to 1.0 V. To evaluate the a-ITZO/Mo S/D contact properties, the derivative of the output characteristics ( $\partial I_D/\partial V_{DS}$ ) is also shown. The result represents linear output characteristics at small  $V_{DS}$ , which indicates that ohmic contacts are formed between a-ITZO and Mo S/D electrodes.

Fig. 3(a) shows the transfer characteristics of a-ITZO TFTs at  $V_{\text{DS}} = 0.1$  and 10 V. The gate current is sufficiently low demonstrating proper device operation. Lower off-current ( $I_{\text{off}} < 10^{-14}$  A) is expected for TFTs patterned by photolithography. We initially extracted the device parameters such as the threshold voltage ( $V_{\text{T}}$ ) and  $\mu_{\text{eff}}$  using standard MOSFET equations in the linear (Eq. (1),  $V_{\text{DS}} = 0.1$  V) and saturation regions (Eq. (2),  $V_{\text{DS}} = 10$  V):

$$I_{\rm D,lin} = \frac{W}{L} \mu_{\rm eff} C_{\rm ox} (V_{\rm CS} - V_{\rm T}) V_{\rm DS}, \qquad (1)$$

$$I_{\rm D,sat} = \frac{W}{2L} \mu_{\rm eff} C_{\rm ox} (V_{\rm GS} - V_{\rm T})^2, \qquad (2)$$

where *W* and *L* are channel width and length, and  $C_{ox}$  is the gate capacitance per unit area (~35.4 nF/cm<sup>2</sup>).

**Fig. 2.** (a) An example of output characteristics of a-ITZO TFT fabricated using mechanical mask. (b) Zoom-in output characteristics in the region of  $V_{DS}$  up to 1.0 V is also shown. The a-ITZO film thickness and  $O_2$  gas flow ratio are 50 nm and 5%, respectively.

Fig. 3(b) shows the  $I_D-V_{GS}$  and  $I_D^{1/2}-V_{GS}$  relationships in the linear and saturation regions, respectively. The linear fitting method based on 10–90% of maximum  $I_D$  was used for initial extraction of  $V_T$  and  $\mu_{eff}$ . More accurate models for field-effect mobility extraction will be discussed in Section 3.2. The subthreshold swing (*SS*) was extracted at the maximum slope point from the sub-threshold region from Fig. 3(a) using  $SS = \{Max[dlog(I_D)/dV_{GS}]\}^{-1}$ . The electrical parameters for the a-ITZO TFTs extracted by this approach are summarized in Table 1. The extracted field-effect mobilities in the linear and saturation regions are 30.6 and 25.6 cm<sup>2</sup>/V s, respectively. These values are about three times higher than that of typical a-IGZO TFTs ( $\sim 10 \text{ cm}^2/\text{V s}$ ).

#### 3.2. Field-effect mobility of a-ITZO TFTs

The  $\mu_{eff}$  extracted using the 10–90% linear fitting method (Table 1) neglected the gate voltage dependence. Thus these values are considered as average values over the TFT operation region. However, it can be seen in Fig. 3(b) that the  $I_D-V_{GS}$  ( $V_{DS} = 0.1$  V) and  $I_D^{1/2}-V_{CS}$  ( $V_{DS} = 10$  V) curves are not perfectly linear, indicating that the slope of this curve or field-effect mobility is gate voltage dependent; i.e.  $\mu_{eff}(V_{GS})$ . The  $\mu_{eff}(V_{GS})$  is associated with the conduction band tail states trapping a portion of electrons in the channel [14]. As  $V_{GS}$  increases (Fermi level increases), more of these states are filled. Thereby, an increased number of free electrons can contribute into drain current leading to an increased  $\mu_{eff}$ . For a-ITZO TFTs, a more accurate field-effect mobility model taking the gate voltage dependence into consideration needs to be developed.

Download English Version:

## https://daneshyari.com/en/article/7150877

Download Persian Version:

https://daneshyari.com/article/7150877

Daneshyari.com