Contents lists available at SciVerse ScienceDirect

## Materials Science in Semiconductor Processing

journal homepage: www.elsevier.com/locate/mssp

# Full quantum simulation study of a nano tri-material double gate silicon-on-insulator MOSFET

Zahra Arefinia a,b,\*

- a Department of Physics, Semnan University, Semnan, Iran

- <sup>b</sup> Research Institute for Applied Physics and Astronomy, Tabriz University, Tabriz, Iran

#### ARTICLE INFO

Available online 16 January 2013

Keywords: Tri-material gate Quantum effects Silicon-on-insulator MOSFET Short-channel effects

#### ABSTRACT

We present 2D full quantum simulation based on the self-consistent solution of 2D Poisson–Schrödinger equations, within the nonequilibrium Green's function formalism, for a novel multiple region silicon-on-insulator (SOI) MOSFET device architecture – trimaterial double gate (TMDG) SOI MOSFET. This new structure has three materials with different work functions in the front gate, which show reduced short-channel effects such as the drain-induced barrier lowering and subthreshold swing, because of a step function of the potential in the channel region that ensures the screening of the drain potential variation by the gate near the drain. Also, the quantum simulations show the new structure significantly decreases leakage current and drain conductance and increases on–off current ratio and voltage gain as compared to conventional and dual material DG SOI MOSFET.

© 2012 Elsevier Ltd. All rights reserved.

#### 1. Introduction

As MOSFET scaling aggressively continues down to the sub-50 nm scale, single and double-gate (DG) devices on silicon-on-insulator (SOI) substrates are likely to replace conventional bulk devices. DG MOSFETs have an ultrathin and fully depleted SOI device geometry. In the DG MOSFETs, the inversion layer can be formed throughout the entire silicon film thickness. Therefore, due to dominance of the CMOS logic, to date, the design efforts involving such novel devices have concentrated on the DG characteristics optimized for maximum saturation current and minimum leakage performance.

By constantly reducing the gate length of the MOSFET devices for improving device performance, designers are gradually facing the constraints of the physical limitation of the device, such as short channel effects (SCEs). Therefore, reduction of the SCEs is assumed to play a major role in pushing the CMOS technology into the nanoscale regime.

E-mail address: arefinia@tabrizu.ac.ir

Hence, due to advances in gate material engineering, dual material double gate (DMDG) MOSFETs have been investigated and are expected to suppress the SCEs [1]. The DMDG MOSFET has two laterally contacting gate materials with different work functions to achieve threshold voltage modulation and improved carrier transport efficiency [2]. Furthermore, it induces a step potential at the interface between the different gate materials and creates a peak electric field in the channel region, which improves the carrier transit speed and increases the device driving capability [1].

To enhance immunity against the SCEs, which results in device reliability in high performance circuit applications, a new nanoscale device structure, tri-material double-gate (TMDG) MOSFET, is proposed. The TMDG MOSFET is similar to a conventional single material DG SOI MOSFET [1] with the exception that the front gate of the TMDG structure involves three materials [3,4]. In addition, the material with the lowest work function as the gate material 1, M<sub>1</sub>, is selected close to the drain as the screen gate and the material with the highest work function as the gate material 3, M<sub>3</sub>, is selected close to the source as the control gate. The main advantage of the TMDG SOI structure is to minimize the adverse SCEs.

<sup>\*</sup> Correspondence address: Research Institute for Applied Physics and Astronomy, Tabriz University, Tabriz, Iran.

Owing to the screen effects from the device, having gate materials with low work function, the high electric field near the drain side can be reduced, which suppresses the hot carrier effects and reduces current leakage [5].

By contrast, as these semiconductor devices are further scaled into the nanoscale regime, it becomes necessary to consider quantum mechanical effects when performing device simulation [6-9]. In order to address the quantum mechanical effects, the nonequilibrium Green function (NEGF) method has been used [10-13]. Thus, in this paper, for the simulation of the TMDG SOI MOSFET, a selfconsistent solution of 2D Poisson-Schrödinger equations, within the NEGF formalism has been achieved [14]. The Poisson equation simulates gate control of the channel and the transport equation simulates charge transport between the source and the drain. Then, fundamental electrical properties of the TMDG SOI such as transconductance characteristics, electrostatic potential and transmission coefficient are obtained and compared with the conventional single material double gate (SMDG) and double material double gate (DMDG) SOI MOSFETs. Also, the performance of the use of three materials in both gates is investigated and compared with the TMDG SOI MOSFET.

#### 2. Device structure

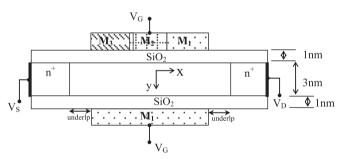

The cross section of the TMDG SOI MOSFET architecture simulated in this work is shown in Fig. 1. The front

gate consisted of three laterally contacting materials with different work functions. To make the threshold voltage near the source more positive than that near the drain, the work function of the materials was selected in such a way that it was highest near the source and lowest near the drain. The length of each gate material,  $M_1$ ,  $M_2$ , and  $M_3$ , was 7 nm, with work functions of 4.0, 4.6, and 5.2 eV, respectively, whereas the back gate was  $M_1$  with a length of 21 nm.

The doping concentrations were assumed to be kept constant in the source and drain regions with a length of 7 nm at  $2 \times 10^{20}$  cm<sup>-3</sup>. It was assumed that the device had an undoped ultra-thin silicon film with a thickness of 3 nm, 1 nm oxide thickness, and 3 nm underlap width.

All the device parameters of the DMDG and SMDG were equal to the TMDG structure, with the exception that the front gate of the DMDG involved two materials,  $M_1$  and  $M_2$ , with a length of 7 and 14 nm, and work function of 4.0 and 4.6, respectively. Also, the front gate of the SMDG consisted of only  $M_1$  material, with a length equal to that of its back gate, 21 nm.

#### 3. Simulation approach

It was assumed that the width of the device was large and the potential was invariant along the width (z direction).

Fig. 1. Cross-sectional view of TMDG SOI MOSFET.

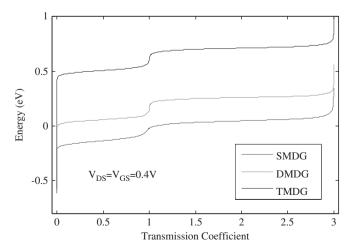

Fig. 2. Ballistic source to drain transmission coefficient versus longitudinal energy of the SMDG, DMDG and TMDG SOI at  $V_{DS} = V_{CS} = 0.4 \text{ V}$ .

### Download English Version:

# https://daneshyari.com/en/article/728789

Download Persian Version:

https://daneshyari.com/article/728789

<u>Daneshyari.com</u>