FISFVIER

Contents lists available at ScienceDirect

## Materials Science in Semiconductor Processing

journal homepage: www.elsevier.com/locate/mssp

## Stability of Cu/Ir/Si trilayer structure to moderate annealing

L.C. Leu<sup>a</sup>, D.P. Norton<sup>a,\*</sup>, T.J. Anderson<sup>b</sup>, L. McElwee-White<sup>c</sup>

- <sup>a</sup> Department of Materials Science and Engineering, University of Florida, Gainesville, Florida 32611, USA

- <sup>b</sup> Department of Chemical Engineering, University of Florida, Gainesville, Florida 32611, USA

- <sup>c</sup> Department of Chemistry, University of Florida, Gainesville, Florida 32611, USA

#### ARTICLE INFO

Available online 17 October 2009

Keywords: Iridium Diffusion barrier Cu-interconnects

#### ABSTRACT

The properties and behavior of trilayer structures consisting of ultrathin iridium thin films sandwiched between Cu and Si have been examined. Iridium thin films (5 nm thick) were deposited on Si substrates using magnetron sputtering, followed by in situ deposition of Cu. The film stacks were examined both as-deposited and after annealing in vacuum over a temperature range of 300–600 °C for 1 h. X-ray diffraction indicates that there is no copper silicide formation upon annealing up to 400 °C. Cross-section HRTEM and EDS line-scans on the sample annealed at 400 °C show the out-diffusion of iridium and the onset of copper diffusion across the interface. The results indicate that iridium is moderately effective as a copper diffusion barrier so long as the processing temperatures remain relatively low.

© 2009 Elsevier Ltd. All rights reserved.

#### 1. Introduction

Diffusion barriers and buffer layers play a pivotal role in many technologies [1-16]. In electronics, one of the most important issues involves the compatibility of metals used for providing contacts and device interconnects. The ever-increasing suite of active materials together with increased demands on circuit performance creates a significant need to understand the limitations of specific metal interface systems in terms of the materials and processing conditions. As an example, the continuous reduction in Si device feature size will soon out-strip the utility of metallization schemes that employ a tantalum/ tantalum nitride (Ta/TaN) diffusion barrier with a Cu seed layer on top for copper metallization. The development of new barrier material structures will be needed as the device dimensions continue to scale down [17-21]. In addition, the conventional Cu electroplating approach for Cu-interconnects requires a Cu seed layer due to the poor nucleation of electrodeposited Cu on Ta [22]. The decreasing feature sizes and increasing high aspect ratios are creating new difficulties in achieving the required uniformity of the Cu seed. As such, the direct copper electroplating on the diffusion barrier without the use of a seed layer has become increasingly attractive. Noble metals, including Ru, Pd, Pt, Rh, Ir, Ag, and Os, have been suggested as replacement materials for the barrier [23], and direct copper electroplating with excellent conformity has been successfully demonstrated for Ru [24], Os [25], and Ir [26]. However, each has its limitations. Recent studies on Ru/Si thin films suggest that Ru itself is not a good barrier against copper diffusion [27-29]. Arunagiri et al. [29] reported that a 5 nm Ru thin film is effective as a copper diffusion barrier only for temperatures up to 300 °C. When one extends the discussion to metallization challenges in even more complex material systems, the need to consider the behavior of specific metal/metal or metal/non-metal interfaces becomes even more apparent.

As one of the platinum group metals, iridium is potentially useful in metallization for a number of electronic applications. It has a high melting point of 2446  $^{\circ}$ C and low resistivity of 4.71  $\mu\Omega$  cm. Iridium has an

<sup>\*</sup> Corresponding author. Fax: +13528461182. E-mail address: dnort@mse.ufl.edu (D.P. Norton).

attractive property of forming a metal oxide (IrO<sub>2</sub>) when oxidized. For the metallization of functional oxides, this property is particularly advantageous. As such, understanding the interfacial stability limitations is important. Previous efforts have included the use of Ir as a single component metal, as a single component barrier, and as a barrier in conjunction with other materials. For Cu-SiO<sub>2</sub>-based electrochemical metallization of memory cells, Ir has been employed as an electrode material [30]. Iridium has been examined as a barrier material for the integration of ferroelectric Pb(Zr,Ti)O3 films on silicon [31]. Iridium has been used in the formation of stacked SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub> ferroelectric capacitors [32]. Iridium has also been examined as an oxygen barrier for the growth of epitaxial superconducting oxides on metals [33]. Iridium is relatively stable when in contact with Cu with no intermediate compound formation and negligible solubility at high temperatures as shown in the Cu-Ir binary phase diagram [34]. Although these physical properties suggest that iridium could provide utility in metallization for various semiconductors, few investigations have been reported on the properties of iridium as a barrier against copper diffusion. In this paper, the properties and stability of Cu/Ir/Si trilayers is examined.

#### 2. Experimental description

Iridium thin films were deposited on Si(100) wafers by magnetron sputtering at room temperature. Film thickness was 5 nm. Prior to deposition, the substrate was etched in 7:1 buffered oxide etch to remove the native oxide, followed by a deionized water rinse. The base pressure of the chamber was of the order of  $5\times10^{-7}$  Torr and the working pressure was kept at 5 mTorr throughout the deposition. The DC sputtering power for the 3 in Ir target was 100 W. Under such conditions, the measured deposition rate was 0.95 Å/s. During the deposition process, the substrates were rotated at 20 rpm to ensure film uniformity.

A 200-nm-thick Cu layer was deposited on top of the iridium barrier in situ at room temperature without breaking the vacuum. The forward sputtering power for Cu deposition was 200 W. The chamber pressure was kept at 5 mTorr Ar throughout the process. The stability of the structure was examined by annealing in vacuum  $(10^{-5} \, \text{Torr})$  over a temperature range of 300–600 °C for 1 h. The film crystallinity and intermetallic phase formation were determined using a Philips APD 3720 X-ray diffractometer (XRD). The interfacial stability of the film stack and copper depth profile were examined using a JEOL 2010F high-resolution transmission microscope (HRTEM) along with a JEOL Superprobe 733 energy-dispersive spectrometer (EDS). For the characterization of electrical properties, a four-point probe was used to measure the sheet resistance of the film stacks.

#### 3. Results and discussion

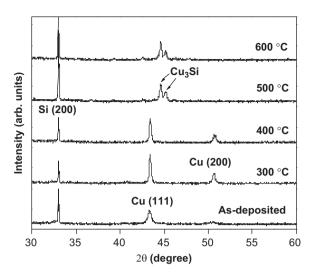

Fig. 1 shows the X-ray diffraction patterns for the Cu/Ir(5 nm)/Si structures both as-deposited and annealed

Fig. 1. X-ray diffraction patterns of as-deposited and annealed Cu/  $Ir(5\,nm)/Si~(0\,0\,1)$ .

in the temperature range of 300–600 °C for 1 h in vacuum. As evident from Fig. 1, upon annealing at 400 °C, no copper silicide diffraction peaks are present, implying no significant copper diffusion through the iridium barrier. This reveals that the diffusivity of copper in iridium is relatively low at 400 °C. Due to grain growth upon heat treatment, copper film crystallinity improves as evidenced by the narrowing of the Cu (111) and (200) peaks. Further annealing yields copper diffusion through the barrier and the formation of copper silicide as indicated by the presence of copper silicide diffraction peaks in the 500 °C annealed samples.

Fig. 2 shows the HRTEM images of the Cu/Ir (5 nm)/Si film stacks before and after annealing at 400 °C for 1 h. As shown in the as-deposited sample, the thickness of Ir barrier is approximately 5 nm. Note that a 2 nm amorphous interlayer lies between the Ir and Si. This amorphous layer is iridium silicide formed at room temperature [35,36] by the diffusion of silicon into iridium [37]. High temperature annealing causes iridium to diffuse further into the adjacent silicon and copper layers as evidenced by the expansion of the dark iridium region shown in Fig. 2b. In agreement with the XRD data, no copper silicide formation is seen in the HRTEM image at the interface upon annealing at 400 °C.

The EDS atomic depth profiles of the as-deposited film stack are shown in Fig. 3. As clearly seen in the depth profiles, a narrow and sharp iridium peak lies between copper and silicon. The EDS Cu signal declines sharply at the position of iridium peak, indicating no copper diffusion into silicon at room temperature. However, a noticeable overlap of silicon and iridium signals exists in the profile as a result of the diffusion of silicon into iridium. The formation of iridium silicide occurs at room temperature. For the annealed stack shown in Fig. 4, the iridium signal spreads towards both silicon and copper. High-temperature annealing leads to perturbation of the iridium bonding, which results in

### Download English Version:

# https://daneshyari.com/en/article/728917

Download Persian Version:

https://daneshyari.com/article/728917

<u>Daneshyari.com</u>