ELSEVIER

Contents lists available at ScienceDirect

### Sensors and Actuators A: Physical

journal homepage: www.elsevier.com/locate/sna

# Application of piezoresistive stress sensors in ultra thin device handling and characterization

Xiaowu Zhang<sup>a,\*</sup>, Aditya Kumar<sup>a</sup>, Q.X. Zhang<sup>a</sup>, Y.Y. Ong<sup>a</sup>, S.W. Ho<sup>a</sup>, C.H. Khong<sup>a</sup>, V. Kripesh<sup>a</sup>, John H. Lau<sup>a</sup>, D.-L. Kwong<sup>a</sup>, V. Sundaram<sup>b</sup>, Rao R. Tummula<sup>b</sup>, Georg Meyer-Berg<sup>c</sup>

- a Institute of Microelectronics, A\*STAR (Agency for Science, Technology and Research), 11 Science Park Road, Singapore Science Park II, Singapore 117685, Singapore

- <sup>b</sup> Packaging Research Center, Georgia Institute of Technology, Atlanta, GA 30332-0560, USA

- <sup>c</sup> Infineon Technologies AG, Am Campeon 3, 85579 Neubiberg, 81726 Munich, Germany

#### ARTICLE INFO

Article history:

Received 8 August 2008

Received in revised form

22 November 2008

Accepted 25 January 2009

Available online 28 February 2009

Keywords:

Piezoresistive stress sensors

Stress measurement

Wafer thinning and handling

Ultra thin device packaging & assembly

#### ABSTRACT

Because of 3D integration, thickness of Silicon wafer is thinner and thinner. For thin silicon ICs, challenges in wafer thinning, handling and assembly process increase. The piezoresistive stress sensors studied in this paper are for experimental purpose, with which detailed stress can be measured during semiconductor process, e.g. wafer thinning. Almost seven times increase in stress have been observed when wafer thickness decreases from 400  $\mu m$  to 100  $\mu m$ . The advantages of these stress data are: (1) serve as a basis for process selection to meet the trends and needs of a reliable package, and for the development and improvement of existing processes; and (2) are important to enhance survivability during wafer thinning, handling and further processing. An ultra thin wafer handling method using support wafer has been investigated to handle 50  $\mu m$  thick wafers. The process for the support wafer method has been well established, which is highly recommended to be used for all processes.

© 2009 Elsevier B.V. All rights reserved.

#### 1. Introduction

The demands to miniaturize products especially for mobile applications and desktop systems are continuing to drive the needs for new and unique solutions in system integration. The requirements of future microelectronic systems include faster, smaller, lighter, and thinner products [1–2]. Advanced microelectronic packaging caters to these ultra-miniaturization and performance needs. One of the innovative approaches adopted to achieve the miniaturization and system integration is embedding active and passive components [3]. Embedded actives require ultra thin silicon die. For thinner silicon die, challenges in wafer thinning, handling and assembly process increase. Silicon piezoresistive stress sensors can be used for in situ stress measurement [4]. In this paper, the piezoresistive stress sensors have been designed, fabricated and calibrated for experimental purpose, with which detailed stress can be measured during wafer thinning process. So far, no such stress data are available

Regarding ultra thin wafer handling methods, DISCO [5] developed the so called DISCO-TAIKO method with thick edge rim. The basic concept is when the wafer is ground, edge rim is left and remains unground. Edge rim provides handling strength and low-

ering handling risk of thin wafers. However, this method is not suitable for some wafer processes which vacuum suck tables are used. IZM-Fraunhofer and ProTec [6] presented the mobile electrostatic chuck (ESC) method, which handles thin wafers through electronic force. Electrical contacts are realized at the backside of the ESC chuck. However, this method has a problem in wet processes (e.g., plating process). In this paper, a support wafer method for ultra thin wafer handling has been developed.

### 2. Design, fabrication and calibration of piezoresistive stress sensors

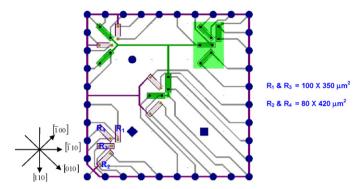

Silicon piezoresistive stress sensors can be used for in situ stress measurement [4]. The layout of the stress sensor design is shown in Fig. 1. Two stress sensors were placed orthogonally for the measurement of the parallel and perpendicular components of the applied stress. The crystal orientations of these two resistors are [1 1 0] and  $[\bar{1}10]$  respectively. Another pair of the stress sensor is rotated 135° with respect to the axis of the applied stress. The crystal orientations of these two resistors are  $[0\,1\,0]$  and  $[1\,0\,0]$ . The resistance of  $R_1$  and  $R_3$  sensors was around 0.625 k $\Omega$  and the resistance of  $R_2$  and  $R_3$  was around 0.932 k $\Omega$ . In this work,  $R_1$  has the same size as  $R_3$  with a width of 100  $\mu$ m and a length of 350  $\mu$ m while  $R_2$  has the same size as  $R_4$  with a width of 80  $\mu$ m and a length of 420  $\mu$ m.

These sensors are fabricated in the silicon die using the conventional silicon processing steps. Thermal oxide of thickness  $5000\,\text{\AA}$

<sup>\*</sup> Corresponding author. Tel.: +65 67705423; fax: +65 67745747. E-mail address: xiaowu@ime.a-star.edu.sg (X. Zhang).

Fig. 1. Stress sensors design.

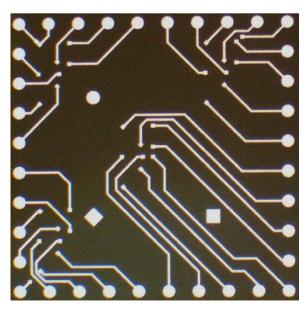

were grown on the both n-type and p-type silicon wafers. Next, the locations of resistors were etched. The resistors were implanted using boron on n-type wafers while using phosphorous on p-type wafers. Afterwards, the wafers were subjected to annealing and drive-in diffusion. Next, aluminum was sputtered to form the metal layers. Finally, a passivation layer (low temperature oxide and silicon nitride) was deposited. Piezoresistive stress sensors have been fabricated as shown in Fig. 2.

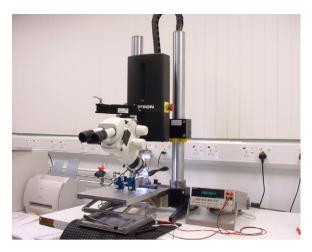

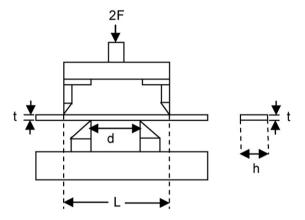

The calibration setup is shown in Fig. 3, which includes a mechanical tester to apply a known stress, two microprobes with a multi-meter for measuring the change in resistance and an optical microscope to ensure the contact between sensor's pad and microprobe. The schematic of four-point bend loading fixture is shown in Fig. 4. The relationship between the applied load (F) and stress  $(\sigma)$  was reported in [7],

$$\sigma = \frac{3F[L-d]}{t^2h} \tag{1}$$

This equation was derived using classical strength of material beam theory assuming a uniform stress  $(\sigma)$  state for points on the top of the specimen. In Eq. (1), L is the loading span, d is the supporting span, h is the width of the sensor strip, and t is the thickness of the sensor strip. This formula works well if the deflection due to the load (F) is not significant and the t and h are small as compared to the d and L [7]. Thus in the present work, L, d, h, and t were chosen to be of 50 mm, 20 mm, 10 mm, and 0.73 mm, respectively.

Fig. 2. The fabricated stress sensor.

Fig. 3. The actual setup for calibration of stress sensors.

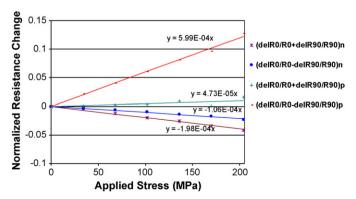

The piezoresistive coefficients are determined by the following equations,

$$(\pi_{11}^{n,p} + \pi_{12}^{n,p}) = \frac{1}{\sigma} \left( \frac{\Delta R_1}{R_1} + \frac{\Delta R_2}{R_2} \right)$$

(2)

$$\pi^{\mathrm{n,p}}_{44} = \frac{1}{\sigma} \left( \frac{\Delta R_1}{R_1} - \frac{\Delta R_2}{R_2} \right) \tag{3}$$

where  $\pi$  is the element of sixth order tensor,  $R_1$  is the resistance of the stress sensor parallel to the uni-axial applied stress.  $R_2$  is the resistance of the stress sensor perpendicular to the uni-axial applied stress. Fig. 5 shows resistance change of parallel and perpendicular p-type and n-type stress sensors versus

Fig. 4. The schematic of four-point bend loading fixture.

**Fig. 5.** Resistance change of parallel and perpendicular stress sensors versus applied stress.

#### Download English Version:

## https://daneshyari.com/en/article/736782

Download Persian Version:

https://daneshyari.com/article/736782

Daneshyari.com