Solid-State Electronics 80 (2013) 135-141

Contents lists available at SciVerse ScienceDirect

# Solid-State Electronics

journal homepage: www.elsevier.com/locate/sse

# Low-temperature electrical characterization of junctionless transistors

Dae-Young Jeon<sup>a,c,\*</sup>, So Jeong Park<sup>a,c</sup>, Mireille Mouis<sup>a</sup>, Sylvain Barraud<sup>b</sup>, Gyu-Tae Kim<sup>c</sup>, Gérard Ghibaudo<sup>a</sup>

<sup>a</sup> IMEP-LAHC, Grenoble INP, Minatec, BP 257, 38016 Grenoble, France <sup>b</sup> CEA-LETI Minatec, 17 rue des Martyrs, 38054 Grenoble, France

<sup>c</sup> School of Electrical Engineering, Korea University, 136-701 Seoul, South Korea

## ARTICLE INFO

Article history: Received 4 June 2012 Received in revised form 23 September 2012 Accepted 14 October 2012 Available online 23 December 2012

The review of this paper was arranged by Prof. S. Cristoloveanu

Keywords: Junctionless transistors (JLTs) Scattering mechanisms Implantation induced defects Flat-band voltage (V<sub>th</sub>) Threshold voltage (V<sub>th</sub>)

## 1. Introduction

Junctionless transistors (JLTs) are currently in the spotlight, owing to the advantages which are expected from their simple structure, without PN junctions, and from their operation principle, based on bulk conduction instead of surface conduction for the standard inversion-mode (IM) MOSFET [1]. For example, ILT devices are known as more robust than IM transistors in terms of effective gate length variability and mobility degradation by transverse electric field. However, JLT devices are facing some issues such as mobility degradation by their high channel doping, reduced gate controllability due to partial depletion regions, and threshold voltage variability induced by fluctuation of silicon thickness and doping atoms spatial distribution. Many specific electrical properties of JLT devices have been investigated, so far mainly at room temperature [1–4]. In particular, JLT devices with planar structures recently revealed very interesting features, including two peaks in the plots of transconductance derivative, which distinguish the (bulk) neutral and (surface) accumulation channels [5]. Only few papers have dealt with low temperature

#### ABSTRACT

The electrical performance of junctionless transistors (JLTs) with planar structures was investigated under low-temperature and compared to that of the traditional inversion-mode (IM) transistors. The low-field mobility ( $\mu_0$ ) of JLT devices was found to be limited by phonon and neutral defects scattering mechanisms for long gate lengths, whereas scattering by charged and neutral defects mostly dominated for short gate lengths, likely due to the defects induced by the source/drain (S/D) implantation added in the process. Moreover, the temperature dependence of flat-band voltage ( $V_{\rm fb}$ ), threshold voltage ( $V_{\rm th}$ ) and subthreshold swing (S) of JLT devices was also discussed.

© 2012 Elsevier Ltd. All rights reserved.

operation, concentrating mainly on the identification of conductance oscillations in nanowire JLTs [6], and on temperature dependence of the threshold voltage of such narrow structures [7]. More generally, low-temperature characterization allows for a better understanding of physical operation and electrical performance of electronic devices [8,9]. Extraction of the electrical parameters of JLT devices in the low-temperature range is a powerful tool to get deeper insight into their operation mechanism and more quantitative information about their performance.

This paper deals with JLT devices with a planar structure ( $W = 10 \ \mu m$ ) fabricated from silicon on insulator (SOI) wafers with a silicon thickness  $t_{\rm si}$  of 9.4 nm. The electrical parameters of JLT devices were extracted at low-temperature and compared to those of IM transistors fabricated by the same process including an additional implantation on source and drain (S/D) regions, except for channel doping concentration. The electrical performances of JLT devices, including scattering mechanisms and short channel effects, are discussed based on an analysis of temperature dependence of low-field mobility, threshold voltage, flat-band voltage and subthreshold swing.

### 2. Device fabrication and experiment

This study was based on N-type JLT devices with high- $\kappa$ /metal gate stack, fabricated at CEA-LETI on (100) SOI wafers with

$<sup>\</sup>ast$  Corresponding author at: IMEP-LAHC, Grenoble INP, Minatec, BP 257, 38016 Grenoble, France.

*E-mail addresses:* jeond@minatec.inpg.fr (D.-Y. Jeon), ghibaudo@minatec.inpg.fr (G. Ghibaudo).

<sup>0038-1101/\$ -</sup> see front matter  $\circledast$  2012 Elsevier Ltd. All rights reserved. http://dx.doi.org/10.1016/j.sse.2012.10.018

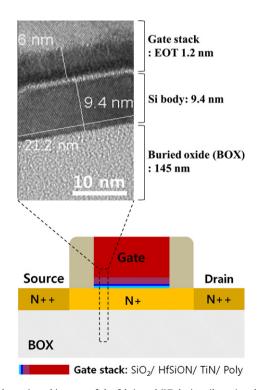

145 nm thick buried oxide (BOX) and a Si body thinned down to 9.4 nm. A full-sheet implantation was performed before active patterning with a phosphorus doping targeted at  $1 \times 10^{19}$  cm<sup>-3</sup> or  $2 \times 10^{19}$  cm<sup>-3</sup>. The gate is composed of HfSiON/TiN/Polysilicon, with an equivalent oxide thickness of 1.2 nm. An additional implantation was performed to S/D regions with the aim of improving electrical performance by reducing access resistance. The S/D implantation process (doping level  $\approx 10^{20}$  cm<sup>-3</sup>) is exactly same with that of IM transistors. Fig. 1 displays the schematic architecture of the fabricated JLT devices, as well as a transmission electron microscopy (TEM) cross-section showing well defined gate stack on the thinned Si channel. On-mask gate length  $L_{\rm M}$  ranged from 1 µm down to 30 nm and on-mask gate width  $W_{\rm M}$  was 10 µm.

The *I–V* current–voltage characteristics were recorded using an HP4156b measurement unit, while temperature was varied from 80 K to 350 K. The channel length difference  $\Delta L$  between effective and on mask channel lengths, which amounted to 10 nm, was obtained by the transfer length method (TLM) [10].

#### 3. Experimental results and discussion

#### 3.1. I-V characteristics at low-temperature

Drain current ( $I_d$ ) of JLT devices for short and long gate lengths (i.e. effective length  $L_{eff}$  = 20 nm, and L = 1 µm, respectively) was measured as a function of gate voltage ( $V_g$ ), with temperature varying in the range of 80–350 K (Fig. 2a and c). The common intersection point, the so called zero-temperature coefficient (ZTC) point [11], where  $I_d$  does not depend on temperature due to the compensated temperature effects of mobility and conduction threshold voltage ( $V_{th}$ ), was found only for long gate lengths (Fig. 2c). This feature is explained from the fact that  $V_{th}$  and carrier mobility were

**Fig. 1.** Schematic architecture of the fabricated JLT devices (lower) and transmission electron microscopy (TEM) cross-section showing well defined gate stack with thinned Si body (upper). An HfSiON/TiN/Polysilicon gate stack (EOT = 1.2 nm) was used and an additional source/drain (S/D) implantation was performed to reduce S/ D access resistance.

both increased at decreasing temperature for long gate length, while they varied in opposite directions (increased and decreased, respectively) at decreasing temperature for short gate length. In contrast, for IM transistors featuring the same structure as JLT devices (Fig. 3a and c), the ZTC was found for both short and long gate lengths, consistently with an increase of  $V_{\rm th}$  and carrier mobility at low temperature, whatever the gate length.

For JLT devices, the corresponding transconductance (g<sub>m</sub>) and transconductance derivative  $(dg_m/dV_g)$  were plotted in Fig. 2b and d, respectively. Two peaks were observed on the  $dg_m/dV_g$  plots (red<sup>1</sup> curve), but for long gate length only (Fig. 2d), owing to reduced mobility degradation and series resistance effects as compared to short gate length. The existence of these two peaks in long JLTs is a clear difference with IM transistors [5], which normally show one single peak regardless of gate length as confirmed in Fig. 3b and d. As already discussed in a previous paper [5], the first peak (left-hand side peak) in Fig. 2d is representative of V<sub>th</sub>, which corresponds to the turning point from full to partial depletion in the channel, whereas the second peak (right-hand side peak) gives the flatband  $(V_{\rm fb})$  position, separating bulk neutral channel from surface accumulation. Interestingly,  $dg_m/dV_g$  plots in Fig. 2d clearly show that the  $V_{\rm fb}$  and  $V_{\rm th}$  of JLT devices were increased at decreasing temperature. The  $V_{\rm th}$  of IM transistors, derived from the peak points in  $dg_{\rm m}/dV_{\rm g}$  plots as shown in Fig. 3b and d, was also increased at low temperature.

#### 3.2. Temperature dependences of threshold and flat-band voltage

The temperature dependence of  $V_{\rm fb}$  and  $V_{\rm th}$  is displayed in Fig. 4a for JLT devices with a long gate ( $L = 1 \, \mu m$ ). The positions of the first and second peaks in the  $dg_m/dV_g$  plots (Fig. 2d) were selected for the determination of  $V_{\rm th}$  and  $V_{\rm fb}$ , respectively. It is known that the  $V_{\rm th}$  of JLT devices can be derived from the depletion approximation or the charge-based analytical model according to the following equation, valid for wide structures [3,12]:

$$V_{\rm th} = V_{\rm fb} - \frac{q \cdot N_{\rm d} \cdot t_{\rm si}^2}{2\varepsilon_{\rm si}} - \frac{q \cdot N_{\rm d} \cdot t_{\rm si}}{C_{\rm ox}} \tag{1}$$

where q,  $N_{\rm d}$ ,  $\varepsilon_{\rm si}$  and  $C_{\rm ox}$  denote electronic charge, doping concentration in the channel, silicon permittivity and gate oxide capacitance per unit area, respectively. From Eq. (1), threshold voltage variation with temperature  $(dV_{\rm th}/dT)$  should be equal to the flat-band voltage variation  $(dV_{\rm fb}/dT)$ , because the  $V_{\rm th}$  term in Eq. (1) contains temperature independent parameters only, except for  $V_{\rm fb}$ . This explains why there was no significant difference between the variations of  $V_{\rm th}$  and  $V_{\rm fb}$  with temperature in Fig. 4a. In addition, the  $V_{\rm fb}$  and  $dV_{\rm fb}/dT$  of JLT devices can be written as an explicit function of temperature, as:

$$V_{\rm fb} = \Phi_{\rm MS} = \Phi_{\rm M} - \left[\chi + \frac{E_{\rm g}}{2} - \frac{k \cdot T}{q} \cdot \ln\left(\frac{N_{\rm d}}{n_{\rm i}}\right)\right]$$

(2)

$$\frac{dV_{\rm fb}}{dT} = \frac{dV_{\rm th}}{dT} = \frac{k}{q} \cdot \ln\left(\frac{N_{\rm d}}{n_{\rm i}}\right) - \frac{k \cdot T}{q} \cdot \frac{1}{n_{\rm i}} \cdot \frac{dn_{\rm i}}{dT}$$

(3)

where  $\Phi_{M}$ ,  $\chi$ , k and  $n_i$  denote metal work function, electron affinity, Boltzmann constant and intrinsic carrier density, respectively. The  $n_i$  is also affected by temperature according to following relationship [13]:

$$n_i \approx n_{i0} \cdot T^{\frac{3}{2}} \cdot e^{-\frac{L_g}{2kT}} \tag{4}$$

where  $E_{\rm g}$  is the energy band-gap and  $n_{\rm i0}$  is around  $3.9 \times 10^{16} \, {\rm cm^{-3}}$ in silicon. The  $dV_{\rm fb}/dT$  value of  $\approx$ -0.56 mV/K which was extracted

<sup>&</sup>lt;sup>1</sup> For interpretation of color in Fig. 2, the reader is referred to the web version of this article.

Download English Version:

# https://daneshyari.com/en/article/748377

Download Persian Version:

https://daneshyari.com/article/748377

Daneshyari.com