Solid-State Electronics 53 (2009) 181-184

Contents lists available at ScienceDirect

Solid-State Electronics

journal homepage: www.elsevier.com/locate/sse

# RF performance of GaAs pHEMT switches with various upper/lower $\delta\text{-doped}$ ratio designs

# Hsien-Chin Chiu\*, Jeffrey S. Fu, Chung-Wen Chen

Department of Electronics Engineering, Chang Gung University, 259 Wen-Hwa 1st Road, Kwei-Shan T..., Taoyuan, Taiwan 333, Taiwan, ROC

#### ARTICLE INFO

Article history: Received 9 January 2008 Received in revised form 25 August 2008 Accepted 1 November 2008 Available online 17 December 2008

The review of this paper was arranged by Prof. A. Zaslavsky

Keywords: High electron mobility transistor Switch Linearity Harmonics Isolation Insertion loss

## ABSTRACT

AlGaAs/InGaAs pseudomorphic high-electron-mobility transistor (pHEMT) single-pole-single-throw (SPST) switches with various upper/lower  $\delta$ -doped ratio designs were fabricated and investigated for the first time. Both off-state capacitance and the specific on-resistance ( $R_{on}$ ) of pHEMT are dominated factors and showed characteristics of sensitive to upper/lower  $\delta$ -doped ratio for RF switch applications. By adopting the series-shunt architecture, upper/lower ratio of 3:1 switch achieved the lowest insertion loss compared to 4:1 design owing to the device shunt to ground (M2) of 4:1 design exhibited a worse fundamental signal isolation especially at high power level. As to the isolation under same architecture, newever, due to the lowest  $R_{on}$  can be obtained, the 4:1 design provided better isolation performance. In addition, the M2 also dominated the second and third harmonics suppression and meanwhile, the lowest  $R_{on}$  of 4:1 design was found to be beneficial to the reduction of the harmonics power transmitted to the output terminal.

© 2008 Elsevier Ltd. All rights reserved.

#### 1. Introduction

Transmitter and receiver switches have become important components in microwave system because of the growing demand for RF switches in time division duplexing systems such as wireless LAN and broadband systems. Complex switching functions, such as those required in 3G and 4G phones (SP5T or SP6T), are easier to be realized in GaAs pHEMT MMIC technologies than traditional MIC PIN diode technologies due to the faster switching speed. Furthermore, the lower power consumption of GaAs pHEMT switch increases the usage time of portable devices. However, the insertion loss of switch will affect the sensitivity of receiver and the output power of transmitter. Therefore, improving insertion loss of GaAs pHEMT switches in order to improve transceiver overall noise figure and output power has become an important requirement for commercial products [1,2]. In modern GaAs pHEMT industry, uniform doping profile in Schottky layer is widely replaced by planar  $\delta$ -doped structure in order to obtain higher carrier injection efficiency into 2-DEG (two dimensional electron gas) [3]. In addition, compared to traditional single planar  $\delta$ -doped design in pHEMTs, double planar  $\delta$ -doped design achieved a higher current drive capability, wider dynamic range, and better linearity. Doping modifications in the Schottky layer (Schottky layer doped) and in the

channel layer (channel doped) of the conventional δ-doped In-GaP/InGaAs pHEMT have been investigated for amplifier applications [4]. However, the doping profiles discussed were not suitable for explaining the linearity of switch pHEMT because the RF switches were only operated at on-state and off-state. The voltage drops between drain and source terminals were usually small. The maximum transmit power of conventional series-shunt pHEMTs switches is directly related to the RF voltages swing across the drain-source and gate of the off-state pHEMTs. High power and low distortion switch operation can only be achieved by higher pinch-off voltage pHEMT, higher control voltage and uniform off-state capacitance distribution of pHEMTs. To increase the pinch-off voltage will sacrifice the switch Ron performance and result in a higher insertion loss due to shallow channel profile [5]. In order to obtain the low Ron and enhanced pinch-off voltage of pHEMT simultaneously, this report investigated various upper/ lower δ-doped ratio designs systematically. The RF switch performance with optimum upper/lower  $\delta$ -doped ratios was then demonstrated.

## 2. Device structure and fabrication

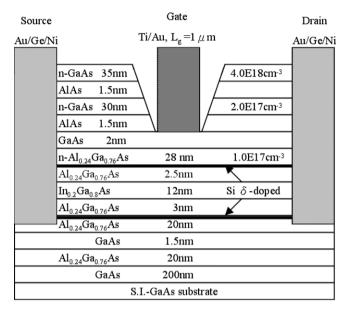

Fig. 1 shows the epitaxy structure of double heterostructure Si  $\delta$ -doped pHEMTs with various upper/lower  $\delta$ -doped designs. Two Si planar  $\delta$ -doped layers sandwiched the 12 nm InGaAs undoped channel layer for high power consideration. Then the n<sup>-</sup> doped

<sup>\*</sup> Corresponding author. Tel.: +886 3 2118800x3350; fax: +886 3 2118507. *E-mail address:* hcchiu@mail.cgu.edu.tw (H.-C. Chiu).

<sup>0038-1101/\$ -</sup> see front matter @ 2008 Elsevier Ltd. All rights reserved. doi:10.1016/j.sse.2008.11.001

Fig. 1. The cross-sectional structure of 1  $\mu m$ -long gate double Si  $\delta$ -doped AlGaAs/ InGaAs pHEMTs.

28 nm AlGaAs layer was grown beneath 2 nm intrinsic GaAs for Schottky layer, which is beneficial for avoiding the AlGaAs exposed in the moisture after gate recess process. Finally, a double recess cap layer design consisted of a 30 nm n<sup>-</sup>-GaAs and a 35 nm n<sup>+</sup>-GaAs was grown on the Schottky layer. The upper Si  $\delta$ -doped layer is doped with four different concentrations, i.e.,  $1 \times 10^{12} \text{ cm}^{-2}$ ,  $2 \times 10^{12} \text{ cm}^{-2}$ ,  $3 \times 10^{12} \text{ cm}^{-2}$  and  $4 \times 10^{12} \text{ cm}^{-2}$ , respectively, and the lower Si  $\delta$ -doped concentration is kept at  $1 \times 10^{12}$  cm<sup>-2</sup>. The lower Si  $\delta$ -doped concentration for pHEMTs is to maintain both gate-to-channel control ability and suitable pinch-off voltage, because these effects are very sensitive to the  $\delta$ -doped concentration when layer is far away from gate electrode. Devices were processed by conventional optical lithography and lift-off technology. Ohmic contacts were realized by using Au/Ge/Ni alloy followed by a 430 °C, 2 min RTA annealing in N<sub>2</sub> ambient. In order to define an active region and switch device, an NH<sub>4</sub>OH/H<sub>2</sub>O<sub>2</sub>/H<sub>2</sub>O solution was used for 200 nm depth mesa etching solution. As to the critical gate-recessed process, a high selective succinic acid solution was applied for high uniformity consideration and then a Ti/Au metal gate was deposited for gate electrode [6]. After a surface treatment, a 150 nm SiO<sub>2</sub> was deposited on the devices, and via holes connecting all the source pads were defined by photolithography. Finally, a 1 µm thick top Au layer was evaporated for bridging the source pads and interconnections.

## 3. Results and discussion

Several 1.0 µm-long gate AlGaAs/InGaAs double heterostructure Si  $\delta$ -doped pHEMTs on GaAs substrate with various upper/ lower  $\delta$ -doped were evaluated on-wafer. The  $R_{\rm on}$  values were 6.8  $\Omega$  mm, 4.1  $\Omega$  mm, 2.9  $\Omega$  mm and 2.3  $\Omega$  mm for upper/lower  $\delta$ -doped ratio from 1:1 to 4:1 designs, respectively. The higher upper  $\delta$ -doped concentration achieved a lower  $R_{\rm on}$  which is beneficial for improving device current density and switches insertion loss. The maximum drain-to-source current ( $I_{\rm d}$  max) was also achieved at the higher upper  $\delta$ -doped concentration. The current density values were 240 mA/mm, 345 mA/mm, 475 mA/mm and 541 mA/mm from 1:1 to 4:1 designs, respectively. In addition, by defining the device pinch-off voltage ( $V_{\rm p}$ ) at  $I_{\rm ds}$  of 1 mA/mm, the higher upper  $\delta$ -doped design performed a deeper  $V_{\rm p}$ . The pinchoff voltages were -0.3 V, -0.7 V, -1.1 V and -1.2 V from 1:1 to

| Table 1                                                                        |

|--------------------------------------------------------------------------------|

| The intrinsic parameters of various upper/lower $\delta$ -doped ratio designs. |

| Parameters $C_{\rm gs}({\rm fF})$ $C_{\rm gd}({\rm fF})$ $C_{\rm ds}({\rm fF})$ $R_{\rm i}(\Omega)$               | g <sub>mi</sub> (mS)             | τ (ps)               |

|-------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------|

|                                                                                                                   |                                  |                      |

| 1:1 197.1 23.43 33.24 31.31   2:1 213.4 26.35 34.32 6.32   3:1 327.9 24.66 35.76 6.12   4:1 364.3 21.95 35.8 6.17 | 14.53<br>18.82<br>24.32<br>29.66 | 5<br>4.2<br>4<br>3.9 |

4:1 designs, respectively. Table 1 listed the intrinsic parameters of various devices by extracting the measured S-parameters. The gate-to-source capacitance ( $C_{gs}$ ) increased with the upper  $\delta$ -doped concentration owing to the suppression of depletion layer at the high doping profile. Therefore, the thin depletion region of high upper  $\delta$ -doped concentration provided a lower isolation characteristic and the depletion region distribution was influenced easily at high power swing. However, no obvious changes were found at gate-to-drain capacitance  $(C_{gd})$  and drain-to-source capacitance  $(C_{ds})$  with various upper/lower  $\delta$ -doped designs. The channel resistance  $(R_i)$  and intrinsic transconductance  $(g_{mi})$  both showed the same trends with their dc performance. The transit time was also improved following with the upper  $\delta$ -doped concentration which was beneficial for improving the switch charge and discharge delay time for RF switch applications. To achieve high power handling capability and low harmonics for SPST switch circuits, the series-

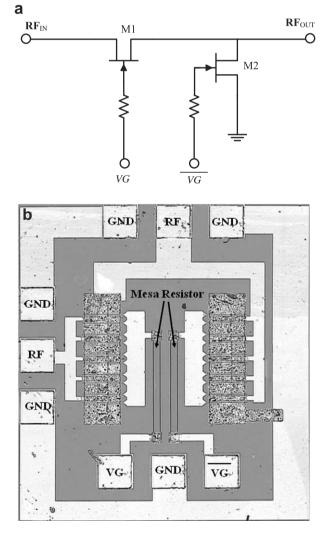

Fig. 2. The series-shunt SPST switch, (a) circuit diagram and (b) chip photography.

Download English Version:

https://daneshyari.com/en/article/748905

Download Persian Version:

https://daneshyari.com/article/748905

Daneshyari.com