Contents lists available at ScienceDirect

# Solid-State Electronics

journal homepage: www.elsevier.com/locate/sse

# Origin of flat band voltage shift in HfO<sub>2</sub> gate dielectric with La<sub>2</sub>O<sub>3</sub> insertion

K. Kakushima <sup>a,\*</sup>, K. Okamoto <sup>b</sup>, M. Adachi <sup>b</sup>, K. Tachi <sup>b</sup>, P. Ahmet <sup>b</sup>, K. Tsutsui <sup>a</sup>, N. Sugii <sup>a</sup>, T. Hattori <sup>b</sup>, H. Iwai <sup>b</sup>

<sup>a</sup> Interdisciplinary Graduate School of Science and Engineering, Tokyo Institute of Technology, S2-20 4259, Natgatsuta, Midori-ku, Yokohama 226-8502, Japan

#### ARTICLE INFO

Article history:

Available online 12 May 2008

The review of this paper was arranged by Jurriaan Schmitz

Keywords: Metal gate High-k Flat band voltage HfO<sub>2</sub> La<sub>2</sub>O<sub>3</sub> Electronegativity

#### ABSTRACT

The origin of flat band voltage ( $V_{\rm FB}$ ) shift with La<sub>2</sub>O<sub>3</sub> insertion for HfO<sub>2</sub> gate dielectrics has been carefully examined. By separating the effect of the fixed charges located at each interface by thickness-dependent  $V_{\rm FB}$  evolution, total voltage shifts (dipole) at metal/high-k and high-k/SiO<sub>2</sub> interfaces have been estimated. Using stacked capacitors of La<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub>, it can be concluded that  $V_{\rm FB}$  is mainly determined by the high-k on SiO<sub>2</sub>. Therefore, the dipole at La<sub>2</sub>O<sub>3</sub> and the interface has an additional dipole of 0.36 eV compared with that of HfO<sub>2</sub>/SiO<sub>2</sub>. The same trend has also been obtained with a high-k on a Si substrate without a SiO<sub>2</sub> layer. A simple model using electronegativity has been proposed to explain the  $V_{\rm FB}$  shift.

© 2008 Elsevier Ltd. All rights reserved.

#### 1. Introduction

While Si-based oxide films have been used as a gate dielectric for more than 30 years, further thinning of these films has already reached its limit owing to a large direct tunneling current [1]. Therefore, alternative gate dielectrics with a high permittivity (high-k) have been extensively examined [2]. Among them, Hfbased oxides, such as HfSiON, have been one of the promising candidates for next-generation gate dielectrics, owing to their high permittivity with a wide band gap and a good thermal stability. One of the issues of HfO2-based materials is the difficulty in controlling the threshold voltage ( $V_{\rm th}$ ), as a relatively high  $V_{\rm th}$  is obtained irrespective of the type of electrode used [3]. It has also been reported that the choice of a high-k has a large impact on V<sub>th</sub> shift, for example, an ultra-thin La<sub>2</sub>O<sub>3</sub> capping layer on a HfO<sub>2</sub> layer can negatively shift  $V_{\rm th}$  to an ideal nMOSFET value [4]. On the other hand, the atomic composition of HaLaO<sub>x</sub> also showed a large impact on flat band voltage  $(V_{FB})$  shift in capacitance-voltage (CV) characteristics [5]. Recently, it has been reported that a dipole at the HfLaOx/SiO2(IL) interface plays an important role in determining  $V_{\rm FB}$  [6,7].

In this study, firstly, the relative voltage shifts existing at metal/high-k and high-k/SiO<sub>2</sub> interfaces are estimated using a thickness-dependent  $V_{\rm FB}$  relation. Then, the  $V_{\rm FB}$  value of stacked oxides of La<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> with various thickness orders are examined to observe the  $V_{\rm FB}$  shift and to clarify which interface is dominant for the

$V_{\rm FB}$  shift. Finally, the origin of the  $V_{\rm FB}$  shift at an interface is explained by electronegativity.

### 2. Experimental methods

#### 2.1. Device fabrication

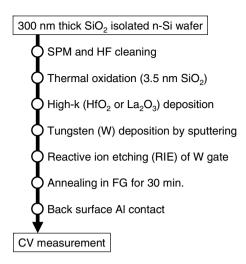

Fig. 1 shows the fabrication flow of MOS capacitors. High-k dielectrics were deposited on a 300-nm-thick  $SiO_2$  isolated n-Si(100) wafer with a thermally grown interfacial oxide layer (IL) with a thickness of 3.5 nm. HfO2 and La2O3 were deposited by electron beam evaporation with an  $O_2$  partial pressure of  $10^{-4}$  Pa. The substrate temperature during the deposition was set to be 300 °C and the deposition rate of the high-k dielectrics was controlled to be 0.3 nm/min. After high-k deposition, 60-nm-thick tungsten (W) was in situ deposited by sputtering without exposing the wafers to air to prevent moisture or carbon absorption. W was patterned by reactive ion etching (RIE) using SF<sub>6</sub> chemistry to form a gate electrode for the MOS capacitors. The wafers were then post-metallization annealed (PMA) in a rapid thermal annealing (RTA) furnace in forming gas (FG) (N<sub>2</sub>:H<sub>2</sub> = 97%:3%) ambient at 420 °C for 30 min. Back surface Al was deposited as a bottom electrode by thermal evaporation. CV characteristics of the MOS capacitors were measured at 100 k and 1 MHz using an Agilent 4284A precision LCR meter. The thickness of IL (3.5 nm) is chosen to be sufficient for suppressing the formation of oxygen vacancies in high-k dielectrics [8]. Moreover, as the annealing temperature studied in this work is low, the effect of Fermi level pining on  $V_{\rm FB}$ can be neglected.

<sup>&</sup>lt;sup>b</sup> Frontier Research Center, Tokyo Institute of Technology, S2-20 4259, Natgatsuta, Midori-ku, Yokohama 226-8502, Japan

<sup>\*</sup> Corresponding author. Tel.: +81 45 924 5847; fax: +81 45 924 5846. E-mail address: kakushima@ep.titech.ac.jp (K. Kakushima).

Fig. 1. Fabrication flow of MOS capacitors.

#### 2.2. Estimation of fixed charges and dipoles at each interface

Fixed charges and dipoles presented at each interface in a simple  $SiO_2/Si$  MOS structure can be expressed with equivalent oxide thickness (EOT) and  $V_{FB}$  as [9]

$$V_{\rm FB} = -{\rm EOT} \Big( \frac{Q_0}{\varepsilon_0 \varepsilon_{\rm ox}} \Big) + \frac{\varphi_{\rm ms}}{q} + \Big( \varDelta_{\rm metal/SiO_2} + \varDelta_{\rm SiO_2/Si} \Big), \tag{1}$$

where  $Q_0$  is the fixed charge at the SiO<sub>2</sub>/Si interface,  $\phi_{\rm ms}$  is the difference between work functions of the metal and Si substrate, and  $\Delta_{\rm metal/SiO_2}$  and  $\Delta_{\rm SiO_2/Si}$  are dipoles at the metal/SiO<sub>2</sub> and SiO<sub>2</sub>/Si interfaces, respectively. The fixed charges inside the oxide layer are neglected as the effects of these charges are small. When a SiO<sub>2</sub> IL with a thickness of EOT<sub>IL</sub> is inserted under a high-k oxide, Eq. (1) can be modified as

$$\begin{split} V_{\rm FB} &= -{\rm EOT}(\frac{Q_0 + Q_1}{\varepsilon_0 \varepsilon_{\rm ox}}) + \frac{Q_1 \cdot {\rm EOT_{IL}}}{\varepsilon_0 \varepsilon_{\rm ox}} + \frac{\varphi_{\rm ms}}{q} + (\varDelta_{\rm metal/high-k} \\ &+ \varDelta_{\rm high-k/IL} + \varDelta_{\rm IL/Si}). \end{split} \tag{2}$$

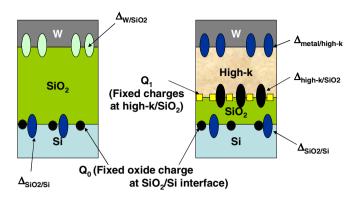

Here,  $Q_1$  is the fixed charge located at the high-k/SiO<sub>2</sub> interface and  $\Delta_{\rm metal/high-k}$  and  $\Delta_{\rm high-k/SiO_2}$  are dipoles at the metal/high-k and high-k/SiO<sub>2</sub> interfaces, respectively. A schematic model of the charge locations and dipoles in a metal/high-k/SiO<sub>2</sub>/Si stack is illustrated in Fig. 2.

#### 3. Results

# 3.1. Fixed charges and dipole extraction of HfO<sub>2</sub>/SiO<sub>2</sub> and La<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> capacitors

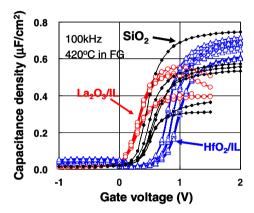

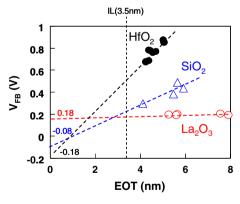

Fig. 3 shows the CV characteristics of MOS capacitors with different HfO<sub>2</sub> or La<sub>2</sub>O<sub>3</sub> thicknesses on SiO<sub>2</sub> IL (3.5 nm). The thicknesses of La<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> vary from 5 to 10 nm. Capacitors with different SiO<sub>2</sub> thicknesses are also shown. It is clear that the  $V_{\rm FB}$  values of the CV curves with HfO<sub>2</sub>/IL stacks reside in the positive direction compared with those of SiO<sub>2</sub> and La<sub>2</sub>O<sub>3</sub>/IL stacks. Fig. 4 shows the  $V_{\rm FB}$ -EOT plot of the fabricated HfO<sub>2</sub>/SiO<sub>2</sub>/Si and La<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/Si stacks. Using Eq. (1), a  $V_{\rm CM}$ 0 of  $V_{\rm CM}$ 1 values for La<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> using Eq. (2) are estimated to be  $V_{\rm CM}$ 1 values for La<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> using Eq. (2) are estimated to be  $V_{\rm CM}$ 2 values for La<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> using Eq. (2) are estimated to be 1.6 × 10<sup>12</sup> and  $V_{\rm CM}$ 3 and  $V_{\rm CM}$ 4 values for La<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> using Eq. (2) are estimated to be 1.6 × 10<sup>12</sup> and  $V_{\rm CM}$ 3 and  $V_{\rm CM}$ 4 and  $V_{\rm CM}$ 5 values for La<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> using Eq. (2) are estimated to be 1.6 × 10<sup>12</sup> and  $V_{\rm CM}$ 5 and  $V_{\rm CM}$ 6 and  $V_{\rm CM}$ 7 and  $V_{\rm CM}$ 8 and  $V_{\rm CM}$ 9 hotoelectron spectroscopy (XPS), was neglected as the effect of such presence on  $V_{\rm CM}$ 8 was small.

**Fig. 2.** Schematic model of fixed charges and dipole locations used in Eqs. (1) and (2).

Fig. 3. CV curves of  $HfO_2/SiO_2/Si$  and  $La_2O_3/SiO_2/Si$  with different high-k thicknesses. Capacitors with different  $SiO_2$  thicknesses are also shown.

Fig. 4. V<sub>FB</sub>-EOT plot of fabricated HfO<sub>2</sub>/SiO<sub>2</sub>/Si and La<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>/Si stacks.

The difference in total dipole between the capacitors, which is the difference between  $q(\varDelta_{\text{W/HfO}_2} + \varDelta_{\text{HfO}_2/\text{IL}})$  and  $q(\varDelta_{\text{W/La}_2\text{O}_3} + \varDelta_{\text{La}_2\text{O}_3/\text{IL}})$ , is calculated to be 0.36 eV. The dipole differences at the W/high-k interface cannot be separated at this point. In the next subsection, this contribution will be discussed using stacked MOS capacitors.

### 3.2. Flat band voltage behavior on stacked high-k MOS capacitors

To separate the contribution of metal/high-k and high-k/SiO<sub>2</sub> from the obtained total dipole difference, capacitors with La<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> stacks with various thicknesses and stacking orders were

## Download English Version:

# https://daneshyari.com/en/article/748992

Download Persian Version:

https://daneshyari.com/article/748992

Daneshyari.com