SOLID-STATE ELECTRONICS

www.elsevier.com/locate/sse

# Bias-stress induced threshold voltage and drain current instability in 4H–SiC DMOSFETs

T. Okayama a, S.D. Arthur b, J.L. Garrett b, M.V. Rao a,\*

Department of Electrical and Computer Engineering, George Mason University, Fairfax, VA 22030-4444, USA

Semiconductor Technology Division, GE Global Research Center, Niskayuna, NY 12309-1027, USA

Received 11 May 2007; accepted 23 July 2007 Available online 4 September 2007

The review of this paper was arranged by Prof. E. Calleja

#### **Abstract**

In this work, the instability of n-channel 4H–SiC double-implanted metal–oxide–semiconductor field-effect-transistors (DMOSFETs) was studied, in terms of threshold-voltage ( $V_{\rm TH}$ ) shifts and drain–source current ( $I_{\rm DS}$ ) transients, for different gate bias stress durations of range 100–5500 s. At room temperature, for positive gate bias stress, the  $V_{\rm TH}$  shift and  $I_{\rm DS}$  decay increase with increasing stress time. The  $V_{\rm TH}$  shift and the  $I_{\rm DS}$  decay were recovered by negative gate bias stress. It is believed that the instability in device behavior during positive gate bias stress is due to capture of electrons by the SiC/gate dielectric interface traps and the gate dielectric near interface traps. Elevated temperature measurements have indicated a decrease in  $V_{\rm TH}$  and an increase in  $I_{\rm DS}$  with increasing stress time possibly due to mobile positive ions in the gate dielectric. © 2007 Elsevier Ltd. All rights reserved.

PACS: 71.20.Nr

Keywords: SiC; DMOSFET; Threshold-voltage shift; Drain current transient; Interface traps; Mobile ions

#### 1. Introduction

Silicon carbide (SiC) has several potential material advantages over Si for the development of high-power solid-state devices. These advantages include a wide bandgap, a large critical field, and a large thermal conductivity, which all together make SiC as an attractive material for high power and high frequency applications [1–3]. Though, SiC DMOSFETs are beginning to be commercialized [4], there are still a number of issues that need to be solved to improve the performance of SiC DMOSFETs. The issues, attributed to the high density of SiC/SiO<sub>2</sub> interface traps and near-interface traps [5,6], are a negative threshold voltage (normally-on) [7–9], a low inversion-channel carrier

mobility [10], reliability issues [11–13], and threshold-voltage instability [14,15].

In this work, the threshold voltages of SiC DMOSFETs were measured after different bias stress durations to determine if the bias stress induces a shift in the threshold voltage. The bias stress measurements were also performed at elevated temperatures. The problem with using threshold-voltage drift measurements alone as an indicator of magnitude of device instability is the lack of consensus on the definition of threshold voltage for SiC DMOSFETs (as described in the next paragraph). In addition, if measurement sweep time to acquire transfer curves at the conclusion of bias stress is long, the electrons may be trapped or detrapped during the sweep also, which may result in altered transfer curves and consequently an erroneous extraction of  $V_{\rm TH}$ . Recent measurements by Gurfinkel et al. [16], driven by the interest in faster measurement,

<sup>\*</sup> Corresponding author. Tel.: +1 703 993 1612; fax: +1 703 993 1601. *E-mail address:* rmulpuri@gmu.edu (M.V. Rao).

have shown a clear dependence between the measured magnitude of instability and the speed of the measurement. Due to this reason, in this work, in addition to studying the threshold-voltage drift, we have also concentrated on studying the drain current transients during the stressing period at both room temperature and elevated temperatures to see if monitoring of the drain current transient during stressing can be used to study the SiC DMOSFET instability. A detailed description of DMOSFET's device operation is given in Ref. [17].

Since SiC DMOSFET's turn-on drain current  $(I_{\rm DS})$  increase with increasing gate–source voltage  $(V_{\rm GS})$  is rather gradual, unlike in Si MOSFET's, there is not a widely accepted threshold-voltage  $(V_{\rm TH})$  definition available for SiC DMOSFETs. Thus, in this work, based on the  $i_{\rm DS}-v_{\rm GS}$  transfer characteristics obtained at  $V_{\rm DS}=0.1~\rm V$ , the  $V_{\rm TH}$  is defined in three ways: (1)  $V_{\rm TH\_SQRT}$ , which is the  $v_{\rm GS}$ -axis intercept of a linear fit to the 90% and the 60% values of  $V_{\rm DS}$  at  $V_{\rm GS}=15~\rm V$ , (2)  $V_{\rm TH\_LIN}$ , which is the  $v_{\rm GS}$ -axis intercept of a linear fit to the 90% and the 60% values of  $I_{\rm DS}$  at  $V_{\rm GS}=15~\rm V$ , and (3)  $V_{\rm TH\_LOG}$ , which is defined as the  $V_{\rm GS}$  value at a drain current of  $1\times 10^{-8}~\rm A$ .

#### 2. Experiment

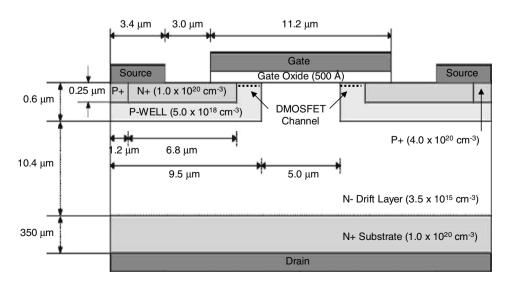

The SiC DMOSFETs were fabricated on a 11  $\mu$ m thick n-type epitaxial layer (3.5 × 10<sup>15</sup> cm<sup>-3</sup>) grown on an n-type 4H–SiC substrate. A schematic of the DMOSFET cell structure is shown in Fig. 1. Each DMOSFET of this work has 625 such cells. The p-well is formed with a multiple energy aluminum implant. Source region was implanted with nitrogen, and a body contact region was co-implanted with aluminum and carbon. The wafer was capped with graphite and annealed for 30 min at 1675 °C for activating the implants. The graphite was removed with an ashing process and the SiC surface was further prepared by thermally growing a 300 Å thick sacrificial oxide. The sacrificial

oxide is thermally grown to remove (consume) a thin ( $\sim$ 130 Å) layer of SiC wafer surface, which may have defects created in it during graphite cap deposition, implant annealing, and cap removal steps. A 50 nm thick gate oxide was grown by successive 1250 °C (in N<sub>2</sub>O) and 1175 °C (in NO) oxidation steps immediately after etching the sacrificial oxide. A liftoff process was used to form nickel ohmic contacts to both n<sup>+</sup>-type and p<sup>+</sup>-type regions. A 0.6  $\mu$ m thick molybdenum gate metal was deposited and patterned and then the ohmic contacts were annealed at 1050 °C for 3 min. The devices were passivated with a silicon nitride film.

Bias stress measurements on the SiC DMOS devices were performed using a Hewlett Packard (Agilent) 4142B Modular DC Source/Monitor Unit and the Metrics Interactive Characterization Software (ICS), version 3.6.0.

A typical cycle used for the bias-stress induced threshold voltage and drain current instability measurements, shown in Fig. 2a, consists of four different gate biasing steps in the order: (1) keeping the gate-source voltage ( $V_{GS}$ ) at +15 V (positive-stress) for a certain duration, (2)  $V_{GS}$  sweep from +15 V to -15 V (sweep-down), (3) keeping  $V_{GS}$  at -15 V(negative-stress) for the same amount of duration as the positive-stress, and (4)  $V_{GS}$  sweep from  $-15 \,\mathrm{V}$  to  $+15 \,\mathrm{V}$ (sweep-up). During the entire cycle the drain-source voltage  $(V_{DS})$  was kept small at 0.1 V, which ensures operation of the device in linear region. The Hewlett Packard 4142B with fast integration setting takes about 2 s to perform sweep-down and sweep-up (from +15 V to -15 V and -15 V to +15 V, respectively, with increments of 0.1 V). The sweep time of 2 s is relatively slow compared to ones reported for the threshold instability measurements  $(10 \mu s-1 s)$  [14–16]. At the end of each step in the bias-stress cycle, all terminals were returned to 0 V and it took about 2 s to setup and start the subsequent step.

First, the bias-stress induced threshold-voltage instability measurement was performed for a 180 s of stress dura-

Fig. 1. Schematic of the DMOSFET cell structure.

### Download English Version:

## https://daneshyari.com/en/article/749321

Download Persian Version:

https://daneshyari.com/article/749321

<u>Daneshyari.com</u>