Contents lists available at ScienceDirect

# Solid-State Electronics

journal homepage: www.elsevier.com/locate/sse

#### Letter

# Performance improvement of normally off AlGaN/GaN FinFETs with fully gate-covered nanochannel

Ki-Sik Im <sup>a</sup>, Dong-Hyeok Son <sup>a</sup>, Ho-Kyun Ahn <sup>b</sup>, Sung-Bum Bae <sup>b</sup>, Jae-Kyoung Mun <sup>b</sup>, Eun-Soo Nam <sup>b</sup>, Sorin Cristoloveanu <sup>c</sup>, Jung-Hee Lee <sup>a,\*</sup>

- <sup>a</sup> School of Electronics Engineering, Kyungpook National University, Daegu, Republic of Korea

- b Convergence Components and Materials Research Laboratory, Electronics and Telecommunications Research Institute (ETRI), Daejeon, Republic of Korea

- <sup>c</sup> IMEP-LAHC, Grenoble Institute of Technology, Minatec, BP 257, 38016 Grenoble Cedex 1, France

#### ARTICLE INFO

Article history:

Received 8 April 2013

Received in revised form 22 July 2013

Accepted 1 August 2013

Available online 28 August 2013

The review of this paper was arranged by Prof. E. Calleja

Keywords: GaN Normally off FinFET Triple gate Nanochannel HEMT

#### ABSTRACT

Normally-off AlGaN/GaN FinFETs have been fabricated by fully covering the nanochannel region with a metal gate. Removing the source/drain extensions (gate underlap regions) greatly decreases the access resistance of the device, which results in an order of magnitude higher on-current and transconductance. As compared with earlier HEMT FinFETs, where the nanochannel is only partially covered by the gate, the carrier trapping at the surface and in the buffer layer is effectively reduced, improving the gate and the drain lags.

© 2013 Elsevier Ltd. All rights reserved.

#### 1. Introduction

AlGaN/GaN-based FinFETs with nanowire structures have been recently fabricated [1–5]. They exhibited promising performance due to the 3-dimensional (3-D) gate configuration which greatly improves the gate control of the nanosize channel. For example, Zimmermann et al. [1], Lu et al. [2], and Ohi and Hashizume [5] showed very low subthreshold slope (SS) and high maximum drain current ( $I_{\rm d,max}$ ) can be obtained from AlGaN/GaN nano-devices.

In addition, as suggested and demonstrated by several groups [1-5], normally-off operation with positive threshold voltage  $(V_{\rm th})$ , which is very important for power switching applications, can be achieved by reducing the fin width to less than 100 nm. From a device-processing viewpoint, the simplicity of this approach (fin size reduction) is very attractive. By comparison conventional planar AlGaN/GaN HFETs or MISHFETs require additional technology steps to achieve a normally-off operation [6-10].

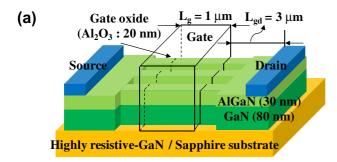

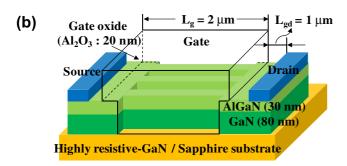

The HEMTs and FinFETs fabricated to date featured gate underlap regions. In this paper, we have fabricated, characterized, and compared normally-off AlGaN/GaN nanochannel FinFETs with partially-covered (Fig. 1(a)) and fully-covered (Fig. 1(b)) gate

\* Corresponding author. Tel.: +82 53 950 6555; fax: +82 53 950 7489. E-mail address: jlee@ee.knu.ac.kr (J.-H. Lee). structure. The latter device exhibits a positive  $V_{\rm th}$  and significantly enhanced performances, compared to more usual AlGaN/GaN transistor (normally-off HFETs or MISHFETs [6–10]) with either planar or underlap FinFET architechture.

#### 2. Growth and device fabrication

The AlGaN/GaN heterostructure was grown on sapphire (0001) substrates by metal-organic chemical vapor deposition (MOCVD). The detailed growth processes, epitaxial structures, and layers thickness are the same as those of conventional AlGaN/GaN HFETs. The two-dimensional electron gas (2DEG) density  $(8.8 \times 10^{12})$  $cm^{-2})$  and electron mobility (  $\sim\!1500\,cm^2\,V^{-1}\,s^{-1})$  at the AlGaN/ GaN heterointerface were measured by Hall effect. The fin-shaped active region of the device, with fin height of 120 nm and variable width (from 60 to 120 nm), was defined by electron-beam lithography followed by transformer-coupled plasma-reactive ion etching (TCP-RIE). The etching depth was controlled such as to remove the 2DEG in the trench regions. In order to smooth the surface and remove the plasma damage from the etched GaN surface, surface treatment was directly followed in a tetramethyl ammonium hydroxide (TMAH) solution for 30 min (25% solution at 85 °C) [4,9,11]. The gate-dielectric consisted of 20 nm-thick Al<sub>2</sub>O<sub>3</sub> deposited by atomic layer deposition at 450 °C. After contact hole

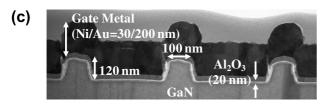

**Fig. 1.** Schematic illustrations of nanochannel AlGaN/GaN FinFETs with (a) partially gate-covered nanochannel (reference device) and (b) fully gate-covered nanochannel (proposed device). The gate insulator is 20 nm-thick  $Al_2O_3$  (not shown). (c) The cross-sectional TEM image. Both devices have  $H_{\rm fin}$  = 120 nm,  $W_{\rm fin}$  = 60–120 nm, and 3 parallel fins.

opening for the source and drain, Ti-based ohmic-contact metals were deposited using an electron-beam evaporator, followed by rapid thermal annealing (RTP) at 900 °C for 30 s in nitrogen ambient. Finally, Ni/Au was deposited as the gate metal. Fig. 1(a) and (b) show the schematic configurations for the AlGaN/GaN FinFETs with partially gate-covered nanochannel (reference device) and fully gate-covered nanochannel (proposed device free of gate underlap). The reference device (partially gated) has gate length of  $L_{\rm g}$  = 1  $\mu$ m and gate metal-to-drain pad distance of 3  $\mu$ m. The corresponding length and distance for the proposed device (fully gated) are 2 and 1  $\mu$ m, respectively. Image of the cross-sectional transmission electron microscopy for the fabricated device with multi-channel array is shown in Fig. 1(c).

### 3. Results and discussion

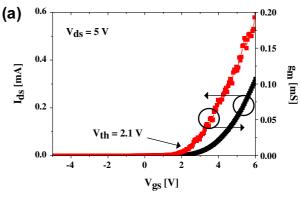

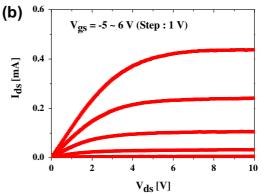

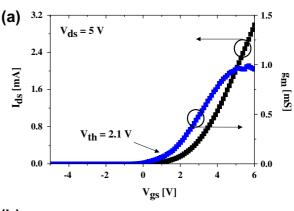

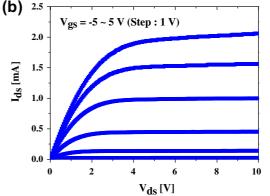

The threshold voltage,  $V_{\rm th}$ , was defined as the gate voltage at 1% of maximum drain current, which roughly corresponds to the value obtained from the intercept of the linear  $\sqrt{I_{\rm ds}}$  vs.  $V_{\rm gs}$  curves in saturation region. Both devices exhibit normally-off operation with  $V_{\rm th}\approx 2.1~V$  at  $V_{\rm ds}=5~V$ , as shown in the  $I_{\rm ds}-V_{\rm gs}$  curve of Figs. 2(a) and 3(a), even though they have a horizontal 2DEG channel near the top of the fin. The normally-off operation in these nanostructured devices is due to the depletion (pinch-off) of the 2DEG channel at  $V_{\rm gs}<0$ , caused by the fringing field from the sidewall sections of the gate [1–5]. As a matter of fact, in our wider fins the lateral fringing field is no longer able to fully deplete the 2DEG and  $V_{\rm th}$  becomes negative; this implies that in narrow

**Fig. 2.** (a) Transfer curve of the reference device at  $V_{\rm ds}$  = 5 V and (b) corresponding  $I_{\rm ds}$ – $V_{\rm ds}$  characteristics.  $L_{\rm g}$  = 1  $\mu$ m,  $W_{\rm fin}$  = 60 nm, 3 fingers.

**Fig. 3.** (a) Transfer curve of the newly proposed underlap-free device at  $V_{\rm ds}$  = 5 V and (b)  $I_{\rm ds}$ – $V_{\rm ds}$  characteristics.  $L_{\rm g}$  = 2  $\mu$ m,  $W_{\rm fin}$  = 60 nm, 3 fingers.

## Download English Version:

# https://daneshyari.com/en/article/752742

Download Persian Version:

https://daneshyari.com/article/752742

Daneshyari.com