ELSEVIER ELSEVIER

Contents lists available at ScienceDirect

# Solid-State Electronics

journal homepage: www.elsevier.com/locate/sse

# The effect of photodiode shape on charge transfer in CMOS image sensors

Bhumjae Shin a, Sangsik Park a,\*, Hyuntaek Shin b

<sup>a</sup> Department of Electronics Engineering, Sejong University, Seoul 143-747, Republic of Korea

#### ARTICLE INFO

Article history:

Received 24 February 2010

Received in revised form 31 May 2010

Accepted 9 June 2010

Available online 3 July 2010

The review of this paper was arranged by

Prof. A. Zaslavsky

Keywords: Image sensor CMOS Photodiode Charge transfer Depletion

#### ABSTRACT

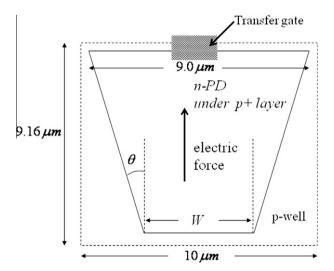

The output signal of a CMOS image sensor is derived from the electrons generated by light incident on the pinned photodiode in each pixel. The output voltage depends on the transfer of the signal electrons from the pinned photodiode to the readout node. In large photodiodes it becomes difficult to fully extract the generated electrons because of the reduction in lateral electric field that pushes the electrons to the transfer transistor. To enhance the transfer, a triangular shaped photodiode was proposed which increases the lateral electric field applied to the photo generated electrons. Compared with a conventional rectangular shaped pixel, the electrons are extracted more easily in a triangular shape since the narrow tail end forms an increased potential gradient. A VGA type image sensor chip showed that the triangular photodiode had 50% higher output voltage than a conventional rectangular photodiode. It was verified that the output voltage is enhanced more by the electric force than the light receiving area. The noise due to the residual electrons was not seen in the image acquired from image sensor having triangular photodiode.

© 2010 Elsevier Ltd. All rights reserved.

#### 1. Introduction

The CMOS image sensor (CIS) market is now larger than the market of the CCD image sensor, principally because CISs have various advantages over CCDs. The advantages of CISs are lower power consumption, increased integration, lower cost and versatile random access. The inferiority of the picture quality of the CIS compared to CCD is overcome by the CDS (Correlated Double Sampling) operation in the 4-transistor pixel [1,2]. It is expected that the market share of the CISs will increase commensurate with the rapid growth of the mobile phone industry.

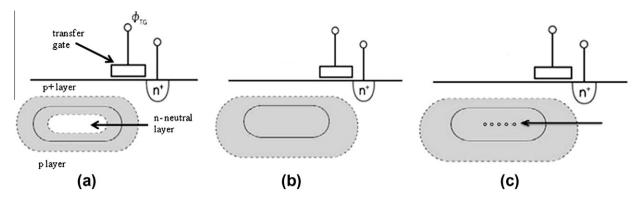

Fig. 1 shows the operation of the pinned photodiode in a 4-transistor CIS pixel [3]. The pinned photodiode is composed of an n-layer within a p-well, and a p-layer covering the n-layer [4–6]. The pinned photodiode has no contacts, and the signal electrons are transferred to the read out node by the operation of the transfer gate (TG) [7]. Fig. 1a is the equilibrium state of the pn junction, where the neutral n-region is formed. After the integration time, a pulse  $\varphi_{\rm TG}$  is applied on the gate of TG to read out the signal electrons. The electrons in the n-neutral region are fully extracted out to the n-type floating diffusion. At this point the neutral region of the n-type has disappeared and the n-type region becomes completely depleted state as shown in Fig. 1b.

The complete transfer of the signal electrons from the photodiode to the readout node is very important. The voltage signal is formed by the electrons from the photodiode charging the readout node and forming a signal exactly proportional to the number of electrons present. Any divergence from this introduces error.

Recently a large photodiode and a small photodiode are used together to achieve the wide dynamic range, where the former is for high sensitivity in low illumination and the later is for high saturation characteristics in high illumination [8–11].

In large photodiodes it becomes difficult to fully deplete the nregion because of the reduction in the lateral electric field pushing the electrons to the transfer transistor as shown in Fig. 1c. In low voltage operation, the lateral electric field forcing the electrons is very weak since the distance to the transfer transistor is longer in larger photodiodes. Finally, the electrons can be left behind if there is a potential barrier or pocket in the photodiode. Any of these effects can cause electrons to stay in the photodiode, these remaining electrons create image lag [12].

An incomplete depletion creates random noise since the number of the remaining electrons varies with each transfer operation. These remnant electrons are equivalent to charging a capacitor (n-layer of the photodiode) and therefore behave like kTC noise of an equivalent smaller capacitance [13,14]. This kTC noise appears as irregular sparkling dots which change from picture to picture.

In Section 2, the electron transfer in the large photodiode is analyzed with regards to output voltage. The improvement of electron transfer with the proposed triangular photodiode is discussed in Section 3.

<sup>&</sup>lt;sup>b</sup> ClairPixel Co., Ltd., Republic of Korea

<sup>\*</sup> Corresponding author. Tel.: +82 2 3408 3733; fax: +82 2 3408 4329. E-mail address: sspark@sejong.ac.kr (S. Park).

Fig. 1. Operation of the pinned photodiode in a 4-transistor CIS pixel. The black region is the depleted layer: (a) equilibrium state, (b) completely depleted state and (c) incompletely depleted state of the pn junction.

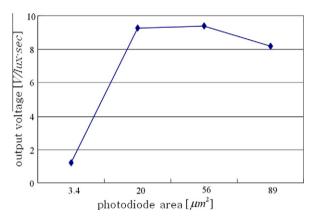

**Fig. 2.** Dependence of the output voltage on the area of photodiode. The shape of n-layer is square, and the width of the transfer gate is 1.0  $\mu$ m.

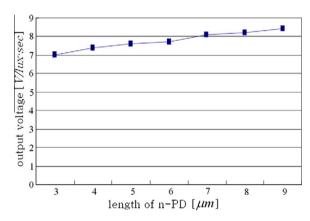

Fig. 4. Dependence of the output voltage on the length of photodiode.

**Fig. 3.** The test patterns with various length *L*.

Fig. 5. Plane view shape of the proposed photodiode. The angle  $\theta$  makes the field enhancing the charge transfer.

### 2. Electron transfer in large photodiodes

The performance of each photodiode was verified using a VGA format  $(640(H) \times 480(V) \text{ pixels})$  image sensor which is composed of 4-transistor pixels, timing generation circuits, A/D converters and data buffer registers. The image sensor was manufactured using

0.18  $\mu m$  design rules in a CMOS process. The doping concentration of the p-well is  $5\times 10^{16}/cm^3$  on the surface and  $3\times 10^{16}/cm^3$  within the first 1  $\mu m$  from the silicon surface. The n and p-layer of the photodiode was formed by implantation with a dose of  $3\times 10^{12}/cm^2$  and  $5\times 10^{13}/cm^2$ , respectively.

Fig. 2 shows the output voltage of image sensors having different photodiode areas. The measured output voltage is normalized

## Download English Version:

# https://daneshyari.com/en/article/753197

Download Persian Version:

https://daneshyari.com/article/753197

<u>Daneshyari.com</u>