Contents lists available at ScienceDirect

### **Energy Conversion and Management**

journal homepage: www.elsevier.com/locate/enconman

## New cascaded multilevel inverter topology with minimum number of switches

### Ebrahim Babaei\*, Seyed Hossein Hosseini

Faculty of Electrical and Computer Engineering, University of Tabriz, Iran

#### ARTICLE INFO

Article history: Received 29 November 2008 Accepted 29 June 2009 Available online 28 July 2009

Keywords: Multilevel inverter Cascaded multilevel inverter Sub-multilevel inverter Full-bridge H-bridge

#### ABSTRACT

In this paper, a new topology of cascaded multilevel inverter using a reduced number of switches, insulated gate driver circuits and voltage standing on switches is proposed. The proposed topology results in reduction of installation area and cost and has simplicity of control system. This structure consists of series connected sub-multilevel inverters blocks. Three algorithms for determination of magnitudes of dc voltage sources have been presented, too. Validity of the analysis has been proved by simulation and experimental results.

Crown Copyright © 2009 Published by Elsevier Ltd. All rights reserved.

ENERGY Conversion and Management

#### 1. Introduction

A multilevel inverter is a power electronic system that synthesizes a desired output voltage from several levels of dc voltages as inputs. Recently, multilevel power conversion technology has been developing the area of power electronics very rapidly with good potential for further developments. The most attractive applications of this technology are in the medium to high voltage ranges.

The concept of utilizing multiple small voltage levels to perform power conversion was presented by a MIT researcher [1,2]. Advantages of this multilevel approach include good power quality, good electro-magnetic compatibility, low switching losses and high voltage capability.

The first introduced topology is the series H-bridge design [1]. This was followed by the diode-clamped inverter [2–4] which utilizes a bank of series capacitors to split the dc bus voltage. The flying-capacitor (or capacitor clamped) [5] topology followed diode-clamped after few years, instead of series connected capacitors, this topology uses floating capacitors to clamp the voltage levels. Another multilevel design, slightly different from the previous one, involves parallel connection of inverter phases through interphase reactors [6]. In this design the semiconductors must block the entire voltage, but share the load current. Also, several combinatorial designs have emerged [7], implemented cascading the fundamental topologies [8–12]; they are called hybrid topologies. These designs can create power quality for a given number of

semiconductor devices higher than the fundamental topologies alone due to a multiplying effect of the number of levels [13]. Also, some soft-switching methods can be implemented for different multilevel inverters to reduce the switching loss and to increase efficiency [14,15]. Recently, several multilevel inverter topologies have been developed [16–19].

Unfortunately, multilevel inverters have some disadvantages. One particular disadvantage is the great number of power semiconductor switches needed. Although low voltage rate switches can be utilized in a multilevel inverter, each switch requires a related gate driver circuits. This may cause the overall system to be more expensive and complex. So, in practical implementation, reducing the number of switches and gate driver circuits is very important.

This paper suggests a new topology for cascaded multilevel inverters with a high number of steps associated with a low number of switches and gate driver circuits for switches. In addition, for producing all levels (odd and even) at the output voltage, three procedures for calculating the required dc voltage sources are proposed. Finally, the paper includes simulation and experimental results to prove the feasibility of the proposed multilevel inverter.

#### 2. Conventional cascaded multilevel inverters

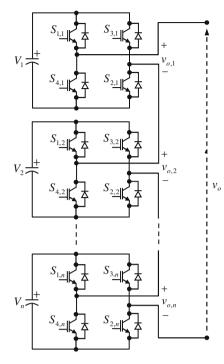

The full-bridge topology with four switches is used to synthesize a three-level square-wave output voltage waveform. The cascaded multilevel inverter consists of series connections of n fullbridge topology. Fig. 1 shows the configuration of cascaded multilevel inverter. The overall output voltage of multilevel inverter is given by:

<sup>\*</sup> Corresponding author. Address: Faculty of Electrical and Computer Engineering, University of Tabriz, Tabriz 51664, Iran. Tel./fax: +98 411 3300819.

*E-mail addresses*: e-babaei@tabrizu.ac.ir, babaeiebrahim@yahoo.com (E. Babaei), hosseini@tabrizu.ac.ir (S.H. Hosseini).

<sup>0196-8904/\$ -</sup> see front matter Crown Copyright © 2009 Published by Elsevier Ltd. All rights reserved. doi:10.1016/j.enconman.2009.06.032

Fig. 1. Configuration of cascaded multilevel inverter.

$$v_{o} = v_{o,1} + v_{o,2} + \dots + v_{o,n} \tag{1}$$

If all dc voltage sources in Fig. 1 equal to  $V_{dc}$ , the inverter is known as symmetric multilevel inverter. The effective number of output voltage steps ( $N_{step}$ ) in symmetric multilevel inverter may be related to the number of full-bridges (n) by:

$$N_{\text{step}} = 2n + 1 \tag{2}$$

and the maximum output voltage  $(V_{o,max})$  of this *n* cascaded multilevel inverter is:

$$V_{o,\max} = n \times V_{dc} \tag{3}$$

To provide a large number of output steps without increasing the number of inverters, asymmetric multilevel inverters can be used. In [20,21], the dc voltages sources are proposed to be chosen according to a geometric progression with a factor of two or three. For *n* cascaded multilevel inverters, the number of voltage steps is given as follows:

$$N_{\text{step}} = 2^{n+1} - 1 \quad \text{if } V_j = 2^{j-1} V_{\text{dc}} \quad \text{for } j = 1, 2, \dots, n \tag{4}$$

$$N_{\text{step}} = 3^n$$

if  $V_j = 3^{j-1}V_{\text{dc}}$  for  $j = 1, 2, ..., n$  (5)

The maximum output voltages of these *n* cascaded multilevel inverters are:

$$V_{o,\max} = (2^n - 1)V_{dc}$$

if  $V_j = 2^{j-1}V_{dc}$  for  $j = 1, 2, \dots, n$  (6)

$$V_{o,\max} = \left(\frac{3^{n}-1}{2}\right) V_{dc} \quad \text{if } V_{j} = 3^{j-1} V_{dc} \quad \text{for } j = 1, 2, \dots, n \tag{7}$$

Comparing the Eqs. (2)–(7), it can be seen that the asymmetric multilevel inverters can generate more voltage steps and higher maximum output voltage with the same number of bridges.

#### 3. Suggested topology

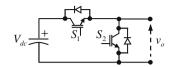

Fig. 2 shows the suggested basic unit for a sub-multilevel inverter. This consists of a capacitor (with dc voltage equal to  $V_{dc}$ ) with two switches  $S_1$  and  $S_2$ . Table 1 indicates the values of  $v_0$  for states of switches  $S_1$  and  $S_2$ . It is clear that both switches  $S_1$  and  $S_2$  can not

Fig. 2. Suggested basic unit for a sub-multilevel inverter.

**Table 1** Values of  $v_0$  for states of switches  $S_1$  and  $S_2$ .

| State | Switches states       |                       | vo              |

|-------|-----------------------|-----------------------|-----------------|

|       | <i>S</i> <sub>1</sub> | <i>S</i> <sub>2</sub> |                 |

| 1     | On                    | Off                   | V <sub>dc</sub> |

| 2     | Off                   | On                    | 0               |

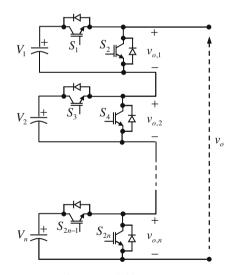

be on simultaneously because a short circuit across the voltage  $V_{dc}$  would be produced. It is noted that two values can be achieved for  $v_o$ . The basic unit shown in Fig. 2 can be cascaded as shown in Fig. 3.

Although this topology requires multiple dc sources, in some systems they may be available through renewable energy sources such as photovoltaic panels or fuel cells or with energy storage devices such as capacitors or batteries. When ac voltage is already available, multiple dc sources can be generated using isolated transformers and rectifiers [22].

The overall output voltage of the suggested cascaded multilevel inverter is given by Eq. (1). Table 2 shows the values of  $v_o$  for state of switches  $S_1, S_2, \ldots, S_{2n-1}, S_{2n}$ . As can be seen,  $2^n$  different values can be obtained for  $v_o$ . Fig. 4 shows a 5-level typical output

Fig. 3. Cascaded basic units.

**Table 2** Values of  $v_0$  for state of switches.

| State          | Switches states |       |                |                |  |            |          | $v_0$                |

|----------------|-----------------|-------|----------------|----------------|--|------------|----------|----------------------|

|                | $S_1$           | $S_2$ | S <sub>3</sub> | S <sub>4</sub> |  | $S_{2n-1}$ | $S_{2n}$ |                      |

| 1              | Off             | On    | Off            | On             |  | Off        | On       | 0                    |

| 2              | On              | Off   | Off            | On             |  | Off        | On       | $v_1$                |

| 3              | Off             | On    | On             | Off            |  | Off        | On       | $v_2$                |

| 4              | On              | Off   | On             | Off            |  | Off        | On       | $V_1 + V_2$          |

| :              | :               | ;     | :              | -              |  | :          | -        | :                    |

| 2 <sup>n</sup> | On              | Off   | On             | Off            |  | On         | Off      | $\sum_{i=1}^{n} v_1$ |

Download English Version:

# https://daneshyari.com/en/article/764859

Download Persian Version:

https://daneshyari.com/article/764859

Daneshyari.com