#### ARTICLE IN PRESS

Superlattices and Microstructures xxx (2017) 1-7

Contents lists available at ScienceDirect

### Superlattices and Microstructures

journal homepage: www.elsevier.com/locate/superlattices

# A dual channel three-terminal np-LDMOS with both majorities for conduction

Moufu Kong\*, Bo Yi, Bingke Zhang

State Key Laboratory of Electronic Thin Films and Integrated Devices, University of Electronic Science and Technology of China, Chengdu, 610054, China

#### ARTICLE INFO

Article history:

Received 26 October 2017

Received in revised form 13 December 2017

Accepted 13 December 2017

Available online xxx

Keywords: Breakdown voltage (BV) np-LDMOS SOA Specific on-resistance

#### ABSTRACT

A novel dual channel three-terminal np-LDMOS power device with both electrons and holes for conduction is proposed in this paper. Based on a new approach of inducing a large-signal which is processed by a simple circuit for controlling the gate of p-LDMOS inside the device, the new np-LDMOS only requires one external gate controlling voltage signal that can be performed as an n-LDMOS device. The SOA of the new device is improved in comparison with the n-LDMOS device, since the counteracting of electric flux density produced by the both type of carriers' currents. Furthermore, the specific onresistance of the np-LDMOS device is reduced by about 19% when comparing with that of the conventional one. The control method and performances of the proposed power device are investigated and authenticated by numerical simulations.

© 2017 Elsevier Ltd. All rights reserved.

#### 1. Introduction

The lateral double-diffused metal-oxide semiconductor (LDMOS) devices are crucial components in many power amplifiers and intelligent power applications with its compatible manufacturing process [1,2]. However, at present the contradiction between higher breakdown voltage (BV) and lower specific on-resistance ( $R_{SP}$ ) is still existent in LDMOS devices, although some measures, such as REduced SURface Field (RESURF) [3–7] and OPTimum Variable Lateral Doping (OPTVLD) are employed [8–11]. The OPTVLD technique is regarded as an excellent trade-off performance between the BV and  $R_{SP}$  of unipolar LDMOS devices. But, it is always expected that the  $R_{SP}$  is to be infinitely low for any given BV of the devices. Moreover, there is a "sharp rise" in the current-voltage characteristics (I–V curves) when an unipolar LDMOS device operates on the status of a high voltage and a large current, which results in a significant reducing of the reliability and safe operating area (SOA) [12,13].

In order to alleviate the problems stated above, a new LDMOS device with the idea of employing majority carriers of both electrons and holes for conduction was proposed [12]. The device (known as np-LDMOS) is a double-gate structure which a high voltage OPTVLD n-LDMOS device is integrated with a high voltage PMOS device by using the same drift region. Thus, the holes of the PMOS can counteract the effect induced by the electrons of the n-LDMOS on the drift region when the device is working on the condition of a high voltage and a large current. After that, some feasible approaches have been proposed to develop the four-terminal device to be a three-terminal one [13,14]. However, there are some drawbacks in these approaches: the self-generated gate controlling signal of PMOS is very weak resulting in a high probability of noise distribution and a very

\* Corresponding author.

E-mail address: kongmoufu@163.com (M. Kong).

https://doi.org/10.1016/j.spmi.2017.12.028

0749-6036/© 2017 Elsevier Ltd. All rights reserved.

Please cite this article in press as: M. Kong et al., A dual channel three-terminal np-LDMOS with both majorities for conduction, Superlattices and Microstructures (2017), https://doi.org/10.1016/j.spmi.2017.12.028

M. Kong et al. / Superlattices and Microstructures xxx (2017) 1–7

complicated low voltage signal processing circuit [13], or the PMOS is only turned on when the device is working on the state of the drain to source voltage more than  $9 \text{ V } (V_{DS} > 9 \text{ V})$ , which cannot lead to a lower  $R_{SP}$  [14]. At the same time, like other dual-channel LDMOS structures presented in Refs. [15–18], the devices are all four-terminal ones, which bring new challenges to application and cannot be used for substituting the conventional three-terminal n-LDMOS or p-LDMOS power devices directly.

In order to achieve a dual channel three-terminal np-LDMOS device with an ultralow  $R_{SP}$  and a better SOA, a novel internal signal generating approach and a very simple low voltage CMOS signal processing circuit for controlling the gate of PMOS are proposed in this paper. And the specifics are depicted in the subsequent sections.

#### 2. Device structure and controlling method

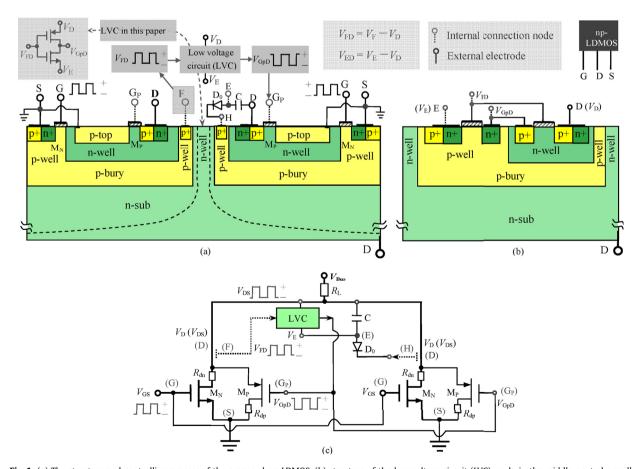

The structure of the proposed np-LDMOS device is based on OPTVLD technique [12–14], which is shown in Fig. 1(a) (The electrodes or connection nodes with the same name are connected together inside the chip in Fig. 1). The p-top region, n-well region and p-bury region constitute an OPTVLD voltage-sustaining region (or drift region). The n-LDMOS  $M_N$  consists of source (S), gate (G), n-well region and drain (D); and the high voltage PMOS  $M_P$  is composed of the drain (D), gate ( $G_P$ ), p-top region and the source (S). It is apparent that both the n-LDMOS  $M_N$  and the PMOS  $M_P$  share the same voltage sustaining region, so they have the same BV. The two dashed lines of the structure are the depletion boundaries when the drain to source voltage  $V_{DS}$  is applied with the breakdown voltage ( $G_P$ ) in this paper) of the device. Meantime, it is easy to see that the left side and the right side of the structure are almost symmetrical, and the only difference between the two sides is the connections of electrodes F and F in this paper is utilized to generate a pulse voltage signal referred to electrode F (the generated pulse voltage signal  $V_{FD} = V_F - V_D$ ) while F is utilized to generate a pulse voltage signal referred to electrode F is utilized to generate a pulse voltage signal  $V_{FD} = V_F - V_D$ , while  $V_{FD} = V_F - V_D$ , the potential difference between electrodes  $V_{FD} = V_D - V_D - V_D$ , the potential difference between electrodes  $V_{FD} = V_D - V_D - V_D$ , the potential difference between electrodes  $V_{FD} = V_D - V_D - V_D$ , the potential difference between electrodes  $V_{FD} = V_D - V_D - V_D$ , the potential difference between electrodes  $V_{FD} = V_D - V_D - V_D$ , the potential difference between electrodes  $V_{FD} = V_D - V_D - V_D$ , the potential difference between electrodes  $V_{FD} = V_D - V_D - V_D - V_D$ .

**Fig. 1.** (a) The structure and controlling process of the proposed np-LDMOS, (b) structure of the low voltage circuit (LVC) made in the middle neutral n-well region shown in (a) and (c) the equivalent circuit of the proposed structure. (The electrodes or connection nodes with the same name are connected together inside the chip.)

Please cite this article in press as: M. Kong et al., A dual channel three-terminal np-LDMOS with both majorities for conduction, Superlattices and Microstructures (2017), https://doi.org/10.1016/j.spmi.2017.12.028

#### Download English Version:

## https://daneshyari.com/en/article/7939086

Download Persian Version:

https://daneshyari.com/article/7939086

Daneshyari.com