Contents lists available at ScienceDirect

## Solar Energy Materials & Solar Cells

journal homepage: www.elsevier.com/locate/solmat

# Forming openings to semiconductor layers of silicon solar cells by inkjet printing

Alison J. Lennon\*, Roland Y. Utama, Martha A.T. Lenio, Anita W.Y. Ho-Baillie, Nicole B. Kuepper, Stuart R. Wenham

The University of New South Wales, ARC Photovoltaics Centre of Excellence, Sydney 2052, Australia

#### ARTICLE INFO

Article history: Received 27 March 2008 Received in revised form 21 May 2008 Accepted 24 May 2008 Available online 15 July 2008

Keywords: Inkjet Etch Silicon Solar cell

#### ABSTRACT

An inkjet printing method for forming openings to buried semiconductor layers of silicon solar cells is described. The method uses an overlying resist as a sacrificial layer onto which a plasticiser for the resist polymer is deposited in a programmed pattern using inkjet printing. At the locations where the plasticiser is printed, the resist becomes permeable to aqueous etching solutions, enabling openings to be created in underlying dielectric or silicon layer(s). The formed openings can be used to create metal contacts to the buried silicon layers of the solar cell. The permeability of the resist to aqueous etchants can be reversed, thus enabling a single resist layer to be used to create more than one set of openings in the underlying layers. The proposed method may also be applied more generally to the formation of patterns of openings in layers of semiconductor or microelectromechanical devices.

Crown Copyright © 2008 Published by Elsevier B.V. All rights reserved.

#### 1. Introduction

Patterning of dielectric and semiconductor surfaces is a critical step for many device fabrication processes. Although many new micropatterning approaches have been described [1,2], typically industrial patterning of dielectric and semiconductor materials is achieved using photolithography [3,4]. For high-resolution applications, such as microelectronic circuit boards, the expenses of implementing a clean room photolithographic process are often justified. However, for many other applications such as solar cells, the use of photolithography is generally considered too complex and expensive for large-scale implementation despite its capability to form well-defined small-area dielectric openings which leads to higher conversion efficiencies.

Most commercially available silicon solar cells use screen printing to form metal contacts [5]. Commercial screen-printed solar cells typically can reach efficiencies as high as 17% [6]. Although new commercially viable developments based on the basic screen-printed design have reported cell efficiencies as high as 18–19% [7–9], these recently reported values are still considerably lower than the current laboratory record for silicon solar cell efficiency of 24.7%, which was achieved in 1999 [10]. In general, higher efficiencies in silicon solar cells (i.e. >20%) have

been largely achieved by using photolithography to form patterns of small-area openings for metal contacts [10,11].

One patterning method which is gaining some interest in the area of solar cells is inkjet printing [12-14]. Although more commonly considered as an additive patterning technology, inkjet printing has been used to form openings in thin polymer layers [15-18]. This technique has been used to form via-hole interconnects in printed electronic structures [15] and polymer relief structures [18]. Of particular interest to solar cell manufacturing methods, CSG Solar [19] recently have implemented an inkjet resist-based patterning method for forming openings to both p-type and n-type semiconductor layers of thin film crystalline silicon solar cells [16,17]. In the latter method, the surface, in which openings are to be formed, is coated with a novolac resist layer. An inkjet device is then used to deposit drops of a caustic solution onto the resist layer, causing the polymer to dissolve and form openings where the deposited solution contacts. The resist is then used as a mask (except in regions where holes have been created) through which the underlying silicon is etched. This technique has been implemented in a thin film silicon solar cell production line. However, because it operates by making openings in the resist layer, the method shares a limitation with photolithographic patterning, in that a single resist layer can only be used for a single set of patterned openings if extensive etching is required. In the case of the CSG solar process, this limitation is circumvented by using a very quick etching time for the second etching pattern, which results in only slightly increased etching of the first pattern of openings. However, this approach, which relies

<sup>\*</sup> Corresponding author. Tel.: +61293856057.

E-mail addresses: alison.lennon@unsw.edu.au (A. Lennon),

s.wenham@unsw.edu.au (S.R. Wenham).

on limited further etching of the first set of openings, is not always possible, especially with higher-efficiency solar cell structures which also involve the etching of dielectric passivating layers.

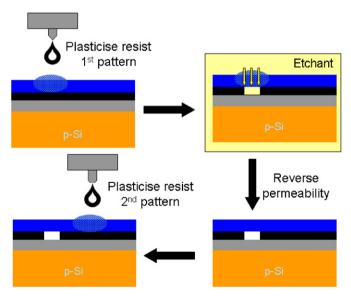

In this paper, we present results of a new method which can be used to form patterns of openings in dielectric and semiconductor layers. Instead of forming openings in the resist layer, this method uses an inkjet device to deposit a solution which causes the formation of localised regions in a resist layer though which etching solutions can permeate, as shown in Fig. 1. Once a pattern of openings has been etched in the underlying dielectric and/or silicon layers, the permeability of the localised regions in the resist can be reversed, thus protecting the formed openings from subsequent etching steps. The ability to reverse the permeability of the patterned regions of the resist enables a single resist layer to be used for multiple patterning steps. The permeable regions are formed by depositing a solution containing a plasticiser for the resist polymer. Plasticisers are small, non-volatile molecules that can push their way between polymer chains, setting the chains apart from one another and thus allowing the polymer to become more mobile and elastic.

This inkjet patterning method is currently being used to enable the fabrication of a new generation of rear-contacted buried-contact silicon solar cells (e.g., [20]). The ability to use a single resist layer to form contact openings to both p-type and n-type silicon on a dielectric-passivated rear surface of a silicon solar cell leads to a significant cost improvement over traditional photolithographic patterning methods. Furthermore, the inkjet patterning method has applications beyond solar cell fabrication, especially in digital fabrication applications where numerous patterning steps are required.

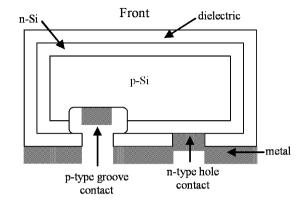

We describe the application of the inkjet patterning method to the formation of openings required for the rear-contacted buried-contact silicon solar cell design described by Kuepper et al. [20]. Unlike the current commercial single-sided buried-contact cell [21], where the buried contacts are located on the front side of the cell, the rear-contact design leaves the front side free of metal contacts. Instead, metal contacts to both polarities are located on the rear side of the solar cell, as shown in Fig. 2. Advantages of contacting both silicon polarities on the rear surface include:

**Fig. 1.** Overview of the method of forming transient permeable regions in a resist layer (blue region) by inkjetting a plasticiser for the resist. Aqueous etching solutions can permeate these regions to etch the underlying dielectric (black region) and/or semiconductor material (e.g., the n-Si grey region). Then the permeability of the regions can be reversed enabling a single resist layer to be used for more than one patterning step.

**Fig. 2.** Schematic cross-section of the rear-side buried-contact solar cell showing both the p-type groove and the n-type hole metal contacts. Metal deposited, by a line-of-sight deposition method, in the base of the p-type groove is electrically isolated from that on the rear surface of the cell.

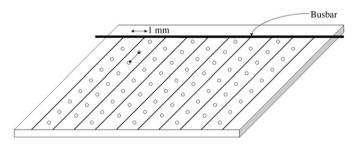

**Fig. 3.** Schematic cross-section showing the arrangement of groove and hole openings on the rear surface of the solar cell depicted in Fig. 2. The p-type groove metal contacts are connected to a busbar (top of cross-section), and the n-type hole metal contacts are positioned in rows between the p-type grooves.

(i) zero shading on the front illuminated surface; (ii) thinner device design which reduces silicon material cost; and (iii) potential for simpler cell interconnection, thus lowering the overall cost in module production.

In the target rear-surface design (Fig. 3), the n-type silicon is contacted via an array of individual hole openings in the dielectric layer, whereas the p-type silicon is contacted via continuous groove openings whose depths extend beyond both the dielectric layer and the n-type silicon layer. To successfully collect the solarcell-generated current, the metal contacts deposited at the bottom of the grooves must connect to a busbar, as shown in Fig. 3, but be electrically isolated from the n-type silicon exposed at the base of all the holes. This electrical isolation can be achieved by using an isotropic silicon etchant to create a dielectric overhang structure in the p-type grooves. Because the isotropic etchant will etch silicon at the same rate in all directions and not significantly etch the dielectric layer, the silicon etch process results in a dielectric overhang on the groove edges, as depicted in Fig. 2. If metal is then deposited using a line-of-sight deposition method, the dielectric overhang acts as a shadow mask, allowing metal to only deposit onto the base of the grooves, thus electrically isolating the metal in the grooves from that on the rear surface.

It is not possible to achieve both sets of patterned n-type holes and p-type grooves using only a single resist layer with previously reported methods. If the n-type holes are formed first, then the exposed silicon at the base of the holes will be further etched by the silicon etch during the isotropic p-type groove etching step of the second patterning process. On the other hand, if the p-type grooves are formed first, then the dielectric overhang structure, necessary for electrical isolation between the p-type and n-type silicon, in the grooves will be destroyed during the

### Download English Version:

# https://daneshyari.com/en/article/80331

Download Persian Version:

https://daneshyari.com/article/80331

<u>Daneshyari.com</u>