ELSEVIER

Contents lists available at ScienceDirect

# Thin Solid Films

journal homepage: www.elsevier.com/locate/tsf

# Transport property improvements of amorphous In–Zn–O transistors with printed Cu contacts via rapid temperature annealing

Ju Yeon Won <sup>a</sup>, Young Hun Han <sup>a</sup>, Hyun Ju Seol <sup>b</sup>, Ki June Lee <sup>b</sup>, Rino Choi <sup>a</sup>, Jae Kyeong Jeong <sup>b,\*</sup>

- <sup>a</sup> Department of Materials Science and Engineering, Inha University, Incheon 402-751, South Korea

- <sup>b</sup> Department of Electronic Engineering, Hanyang University, Seoul 133-791, South Korea

#### ARTICLE INFO

Article history:

Received 4 December 2015

Received in revised form 16 February 2016

Accepted 17 February 2016

Available online 20 February 2016

Keywords:

Printed contacts

Copper

Rapid temperature annealing

Indium-zinc-oxide

Semiconductor

Tantalum

Diffusion barrier

Thin-film transistors

#### ABSTRACT

The device performance of amorphous In–Zn–O (a-IZO) thin-film transistors (TFTs) with printed Cu contacts was significantly improved by the insertion of a diffusion barrier Ta layer and rapid thermal process (RTP) annealing. Furnace-annealed a-IZO TFTs with Cu/Ta contacts exhibited mobility values of 21.3 cm $^2$ /Vs, subthreshold gate swing (SS) values of 1.9 V/decade, and  $I_{ON/OFF}$  of ~10 $^6$ . In contrast, the SS, mobility, and  $I_{ON/OFF}$  ratio of RTP-annealed a-IZO TFTs with Cu/Ta contacts were 30.6 cm $^2$ /Vs, 0.68 V/decade, and 3 × 10 $^7$ , respectively. We attributed the performance improvement of devices with Cu/Ta contacts to the suppression of Cu in-diffusion within the a-IZO channel due to the rapid heating associated with RTP annealing.

© 2016 Elsevier B.V. All rights reserved.

## 1. Introduction

Amorphous oxide semiconductor (AOS) thin-film transistors (TFTs) are widely used as pixel drivers for advanced active-matrix liquid crystal displays and organic light-emitting displays due to reasonable mobility values of ~10 cm<sup>2</sup>/Vs, good substrate size scalability, and extremely low leakage currents [1–2]. The RC delay time for backplane electronics must be aggressively reduced to meet the current stringent requirements for high pixel densities ( $\geq 2000 \times 4000$ ), high frame rates (≥240 Hz), and 3-dimensional visual effects [3]. With this regard. high-speed AOS transistors with low resistivity wiring interconnections are being intensively investigated. Cu interconnections compatible with AOS thin-film transistors (TFTs) are highly desirable due to the low resistivity of Cu (1.68  $\mu\Omega$  cm). However, the migration of Cu atoms into the AOS layer during contact annealing serves to degrade transfer characteristics [4–5]. Therefore, diffusion barriers such as titanium (Ti) [6], molybdenum (Mo) [7], tantalum (Ta) [8], and molybdenum titanium (MoTi) [9] are being used in TFTs with Cu contacts.

Thus far, Cu films as contact layers for TFTs have been primarily prepared via expensive vacuum-based sputtering deposition methods [4–10]. On the other hand, solution-based processes may reap potential benefits such as simplified processes, low costs, and high throughput. Despite these benefits, the use of printed Cu films as contact layers in

\* Corresponding author. E-mail address: jkjeong1@hanyang.ac.kr (J.K. Jeong). AOS TFTs has been limited due to the difficulty of proper ink formation and the anti-oxidation of Cu films during thermal annealing [11–12]. Furthermore, few studies have investigated which diffusion barriers and contact annealing processes are most optimal for AOS TFTs.

In this study, we report on the device performance of a-IZO TFTs with reverse offset printed Cu contacts. To suppress Cu diffusion into the a-IZO channel during contact annealing, rapid thermal processing (RTP) and Ta layer diffusion barrier insertion were employed. Furnace annealing of a-IZO TFTs with Cu/Ta contacts resulted in TFTs with reasonable transport properties. However, RTP-annealed a-IZO TFTs exhibited superior mobility values ( $\mu_{FE}$ ), smaller subthreshold gate swing (SS) factors, and larger  $I_{ON/OFF}$  ratios than furnace-annealed a-IZO TFTs. The  $\mu_{FE}$ , SS, threshold voltage ( $V_{TH}$ ), and  $I_{ON/OFF}$  ratios of RTP-annealed devices were 30.6 cm²/Vs, 0.68 V/decade, 1.0 V, and 3  $\times$  10², respectively. We determined reasons for these improvements based on Cu distribution profiles and contact resistance analysis.

#### 2. Experimental

A 100-nm-thick  $SiO_2$  layer was grown via thermal oxidation and a heavily doped p-type Si wafer was used as the gate electrode. A 28 nm thick IZO film (AOS channel) was prepared for bottom gate TFTs via magnetron sputtering of the  $SiO_2/Si$  substrate with In:Zn at an atomic ratio of 6:4. The distance between the IZO substrate and target was  $\sim 16$  cm and the DC sputtering power was fixed to 100 W. The working pressure was 0.26 Pa and the relative oxygen ratio ( $[O_2]/[Ar + O_2]$ ) was

0.30. A 10 nm thick Ta diffusion barrier layer was deposited via DC sputtering onto the IZO/SiO<sub>2</sub>/Si substrate. A Cu film source/drain (S/D) electrode was prepared via low-cost reverse offset printing. Cu inks were obtained from Dongjin SemiChem. Inc.; these inks consisted of Cu nanoparticles, binders, additives, and solvents. The Cu ink mass density and wt.% of Cu nanoparticles within the Cu ink were 1.21 g/ml and 44.1%, respectively. Cu films as the S/D electrode were prepared via reverse offset processes [13]. Cu inks were coated onto a blanket and then transferred to the cliché by rolling with an inverse S/D pattern. The cliché, which removed unnecessary parts on the blanket, was made from a 100 µm thick stainless steel foil. The remaining S/D pattern on the blanket was manually printed onto the IZO/SiO<sub>2</sub>/Si substrate. The printed Cu film was sintered in a furnace for 10 min at 250 °C under an ambient N<sub>2</sub> atmosphere. The ramp rate of the furnace was approximately 5 °C/min. To effectively reduce the sintering time, RTP annealing was also carried out. The annealing conditions used for RTP were the same as those used for furnace annealing with the exception of the ramp rate (60 °C/min). The physical thickness of the printed Cu film onto the IZO/SiO<sub>2</sub>/Si substrate was approximately 1.3 µm, irrespective of the sintering methods. The contact resistance of both device types was determined using the transmission line method (TLM). Devices with channel lengths of 100, 150, 200, and 250 µm were used for TLM analysis. Transfer characteristics of the a-IZO TFTs were measured at room temperature using a Keithley 2636 source meter. The thickness of the ZTO channel layer and Cu film was evaluated by ellipsometry (K-Mac, STER) and scanning electron microscopy (SEM, Hitachi, S-4300), respectively, which was confirmed by cross-sectional transmission electron microscopy (XTEM, FEI, Tecnai F20) operating at 200 kV. The crystalline quality of Cu films was analyzed by theta/2theta X-ray diffraction (XRD, PANalytical, X'Pert-PRO,) using Cu Kα radiation operating at 40 kV. Cu depth profiles for the Cu/Ta/IZO stacks were examined via XTEM and energy dispersive X-ray spectroscopy (EDS).

### 3. Results and discussion

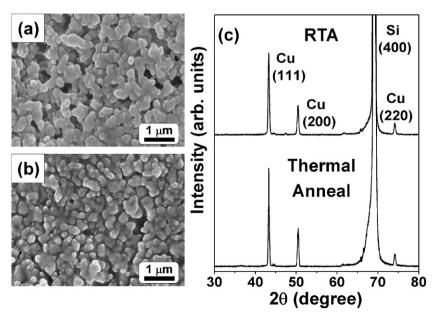

Fig. 1a and b shows the SEM images of the furnace- and RTP-annealed printed Cu films on the SiO<sub>2</sub>/Si substrate, respectively. Both films exhibited well-dispersed spherical morphologies, suggesting that Ostwald ripening-induced sintering occurred during the annealing process. Peaks at 43.3, 50.5, and 74.2° in the X-ray diffraction patterns for both films were identified as Cu (111), (200), and (220) reflections,

respectively (Fig. 1c) [14]. No copper oxide peaks were detected in either film type. Cu grain coalescence was more pronounced in the furnace-annealed Cu films over the RTP-annealed films, which was attributed to a higher thermal budget for furnace-annealing due to a lower ramp rate.

Fig. 2a and b presents the representative transfer characteristics of furnace- and RTP-annealed a-IZO TFTs, respectively. The  $\mu_{FE}$  was determined by the maximum transconductance at a drain voltage  $(V_{DS})$  of 0.1 V. The  $V_{TH}$  was determined by the gate voltage ( $V_{GS}$ ), which induced a drain current of L/W  $\times$  10 nA at a  $V_{DS}$  of 5.1 V. The SS (SS =  $dV_{GS}$ /  $dlogI_{DS}$  [V/decade]) was extracted from the linear component of the  $log(I_{DS})$  vs.  $V_{GS}$  plot. The bulk trap density  $(N_{SS})$  of the TFTs was calculated from the following equation:  $SS = qk_BT \cdot N_{SS}t_{ch}/[C_i\log(e)]$ , where q is the charge of an electron,  $k_B$  is Boltzmann's constant, T is the absolute temperature, and  $t_{ch}$  is the channel layer thickness [15]. The furnaceannealed device exhibited a  $\mu_{FE}$  value of 21.3  $\pm$  5.0 cm<sup>2</sup>/Vs, SS of 1.88  $\pm$  0.4 V/decade,  $V_{TH}$  of 5.5  $\pm$  1.0 V, and an  $I_{ON/OFF}$  ratio of 1  $\times$  10<sup>6</sup>. By contrast, the RTP-annealed a-IZO TFTs exhibited a  $\mu_{FE}$  of 30.6  $\pm$ 4.0 cm<sup>2</sup>/Vs, SS of 0.68  $\pm$  0.2 V/decade,  $V_{TH}$  of 3.4  $\pm$  1.0 V, and  $I_{ON/OFF}$ ratio of 3  $\times$  10<sup>7</sup>. It was noted that non-negligible variations in the  $\mu_{FE}$ , SS, and  $V_{TH}$  values of the a-IZO TFTs were due to manual printing of the S/D pattern blanket onto the IZO/SiO<sub>2</sub>/Si substrate. The  $\mu_{FF}$  values reported for AOS TFTs with printed Cu and lacking a diffusion barrier were limited to 0.4–1.4 cm<sup>2</sup>/Vs [11–12]. Therefore, the high  $\mu_{FF}$  values (21.3– 30.6 cm<sup>2</sup>/Vs) in this study could be attributed to both the adoption of proper Ta diffusion barriers and the low effective electron mass of the a-IZO films, which were comparable or superior to those of AOS TFTs (4.8–18.7 cm<sup>2</sup>/Vs) with vacuum-based Cu contacts [5–10]. Contact resistance  $(R_C)$  values for the furnace- and RTP-annealed devices were approximately 212 and 103  $\Omega$  cm, respectively, as determined via TLM analysis shown in Fig. 3.  $R_C$  corrected intrinsic channel mobility  $(\mu_{intrinsic})$  values for thermally-annealed and RTA-treated TFTs were 31.0 and 35.3 cm<sup>2</sup>/Vs, respectively. This indicated that higher  $\mu_{FE}$  values for the RTP-annealed a-IZO TFTs over the furnace-annealed a-IZO TFTs were due to the lower  $R_C$  values of the former devices. The superior  $\mu_{FE}$  values of the RTP-annealed a-IZO TFTs were reflected in high  $I_{DS}$ levels (Fig. 2d) compared with those of furnace-annealed a-IZO TFTs (Fig. 2c).

In-diffusion of Cu impurities into the underlying *a*-IZO channel layer through the Ta diffusion layer was analyzed via EDS. Fig. 4 presents cross-sectional TEM images for the furnace- and RTP-annealed Cu/Ta/

Fig. 1. SEM images of (a) furnace- and (b) RTP-annealed printed Cu films on SiO<sub>2</sub>/Si substrates. (c) XRD patterns of both Cu films.

# Download English Version:

# https://daneshyari.com/en/article/8033788

Download Persian Version:

https://daneshyari.com/article/8033788

Daneshyari.com