EL SEVIER

Contents lists available at ScienceDirect

### Thin Solid Films

journal homepage: www.elsevier.com/locate/tsf

# Sn-induced low-temperature (~150 °C) crystallization of Ge on insulator

A. Ooato <sup>a</sup>, T. Suzuki <sup>a</sup>, J.-H. Park <sup>a,b</sup>, M. Miyao <sup>a</sup>, T. Sadoh <sup>a,\*</sup>

- <sup>a</sup> Department of Electronics, Kyushu University, 744 Motooka, Fukuoka 819-0395, Japan

- <sup>b</sup> JSPS Research Fellow, 8 Ichiban-cho, Chiyoda-ku, Tokyo 102-8472, Japan

#### ARTICLE INFO

Available online 11 September 2013

Keywords: Ge Metal-induced crystallization Layer-exchange growth Thin-film transistors Solar cell

#### ABSTRACT

Low-temperature formation ( $\sim$ 150 °C) of Ge films on insulator is investigated for realization of advanced flexible devices. We propose utilization of Sn as catalyst to enhance the crystallization at low-temperatures. By annealing (150–200 °C) of a-Ge/Sn stacked structures formed on insulators, the composition distributions of Ge/Sn layers are inverted, and Sn/poly-Ge stacked structures are obtained. The results demonstrate that the crystallization occurs at 150 °C, which is slightly below the eutectic temperatures. This Sn-induced crystallization technique is useful to obtain poly-Ge on low-cost flexible substrates (softening temperature:  $\sim$ 200 °C).

© 2013 Elsevier B.V. All rights reserved.

#### 1. Introduction

A technique for low-temperature formation of poly-Ge films is essential to realize advanced flexible devices such as high-speed thin-film transistors and high-efficiency solar cells on low-cost flexible plastic substrates (softening temperature: ~200 °C) [1]. By conventional solid-phase crystallization (SPC), high-temperature annealing at 500 °C is necessary to induce crystallization [2]. To obtain poly-Ge films on insulator at low temperatures, metal-induced crystallization techniques, such as Ni-induced lateral crystallization [3–5], Ni-imprint-induced crystallization [6,7], and Al-induced crystallization (AIC) [8,9] were developed. In these processes, the crystal nucleation and subsequent nucleus growth are enhanced by the catalytic effects of metals.

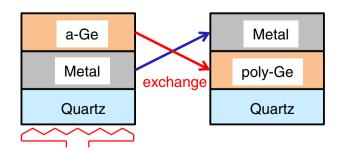

Recently, the AIC processes of Si, SiGe, and Ge are intensively investigated, where a-Si/Al, a-SiGe/Al, and a-Ge/Al stacked structures are employed [8–12]. In these AIC processes, layer-exchange of the stacked structures results in formation of poly-crystal films on insulator, as schematically shown in Fig. 1. Kurosawa et al. comprehensively investigated the effects of the interfacial Al-oxide layer formed between the a-Si and Al layers on the growth features of Si [9]. As a result, they realized selective formation of (100) or (111)-oriented large crystal grains (~50–100 µm) by optimizing the interfacial oxide thickness [9]. These efforts decreased the growth temperature of poly-Si to ~450 °C, which was lower compared with other metal-induced crystallization techniques of Si employing Ni as the catalyst (~550 °C) [3–7]. Consequently, growth of poly-Si films on glass substrates (softening temperature: ~500 °C) has become possible.

Kurosawa et al. also investigated AIC growth of a-SiGe, where they encountered phenomena of inhomogeneous layer-exchange, due to enhanced nucleation in a-SiGe with high Ge concentrations ( $\geq$ 50%) [8].

They solved this problem by controlling the thickness of interfacial Aloxide layers and realized complete layer-exchange crystallization of SiGe with high Ge concentrations (50%–100%) at 410 °C [8]. On the other hand, Toko et al. recently investigated effects of the annealing temperature on AIC of Ge and achieved poly-Ge at ~325 °C [12]. However, the crystallization temperatures should be further decreased in order to employ flexible plastic substrates.

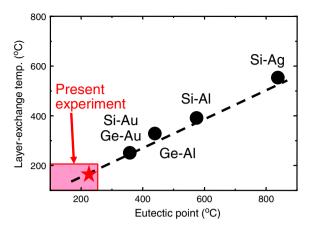

Such layer-exchange growth was also reported for the a-Si/Ag structures, though high temperature annealing (530 °C) is necessary [13]. We previously employed Au instead of Al or Ag and decreased the crystallization temperature of Si, SiGe, and Ge to ~250 °C [14,15]. It is noted that these metals (Al, Ag, and Au) form eutectics with Si and Ge. The layer-exchange growth temperatures of these reported data are summarized as a function of the eutectic temperatures in Fig. 2. It is found that the layer-exchange growth temperatures are slightly lower than the eutectic temperatures [361 °C (Au–Ge), 363 °C (Au–Si), 420 °C (Al–Ge), 577 °C (Al–Si), 845 °C (Ag–Si)] [16] and decrease with decreasing eutectic temperature. This trend clearly indicates that the layer-exchange growth of Ge occurs in the combination with metals, which form eutectics with Ge. Moreover, the layer-exchange growth should

Fig. 1. Schematic of metal-induced layer-exchange crystallization.

<sup>\*</sup> Corresponding author. Tel.: +81 92 802 3737; fax: +81 92 802 3724. E-mail address: sadoh@ed.kyushu-u.ac.jp (T. Sadoh).

**Fig. 2.** Summary of reported layer-exchange-growth temperature as a function of eutectic temperature. The data of Ge/Au [15], Si/Au [14], Ge/Al [12], Si/Al [9], and Si/Ag stacked structures [13] are plotted. The experimental conditions of the present study are also shown by hatching.

be generated at temperatures slightly below the eutectic temperatures. In line with this, we have focused our attention on the catalytic effects of Sn. Sn forms a eutectic system with Ge, and the eutectic temperature (231 °C) [16] is very low. Thus, low-temperature layer-exchange growth is expected to be possible for a-Ge/Sn stacked structures.

In this study, we examine the Sn-induced crystallization technique to achieve low-temperature crystallization of Ge. The effects of annealing temperature on the growth characteristics are investigated. As a result, low-temperature growth (~150 °C) of poly-Ge films on insulators is realized.

#### 2. Experimental procedure

In the experiment, quartz substrates were employed. After an ultrasonic-cleaning of the substrates in acetone at room temperature for 3 min, Sn films (thickness: 100 nm) and a-Ge films (thickness: 100 nm) were sequentially deposited at room temperature by a molecular beam deposition technique (base pressure:  $\sim 7 \times 10^{-8}$  Pa, deposition rate: 0.01 nm/s). The samples were annealed (100–200 °C, 20–200 h) in dry N<sub>2</sub> ambient to induce crystallization.

The grown layers were analyzed by Nomarski optical microscopy, Auger electron spectroscopy (AES) (diameter of detection area:  $\sim\!40~\mu m$ ), and micro-probe Raman scattering spectroscopy (excitation-laser spot-diameter:  $\sim\!1~\mu m$ , wavelength: 532 nm). The Raman measurements were carried out from the back sides of the samples through the transparent quartz substrates in order to characterize the bottom layers.

#### 3. Results and discussion

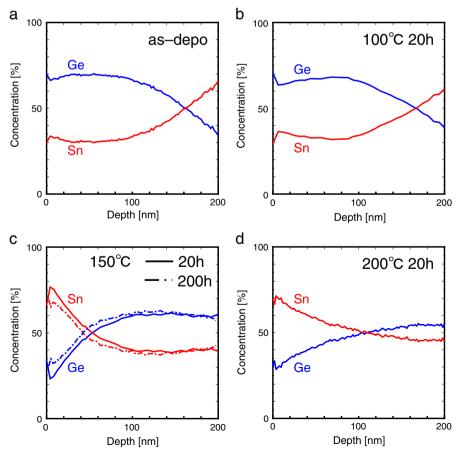

To examine the change in composition induced by annealing, AES measurements were performed. The concentration profiles of Ge and Sn atoms in the samples before and after annealing (100–200 °C) are shown in Fig. 3. Fig. 3(a) indicates that Ge and Sn are dominant near the surface and the bottom, respectively, in the sample before annealing. Here, it is noted that the profiles of Sn and Ge are grading, and sharp interface between Ge and Sn layers is not observed. Further investigation is needed to reveal the phenomena.

As shown in Fig. 3(b), the concentration profiles do not change after annealing at 100 °C for 20 h. On the other hand, the dominant constituents of the top and bottom layers have changed into Sn and Ge,

Fig. 3. Concentration profiles of Ge and Sn in samples before (a) and after annealing at 100 °C (b), 150 °C (c), and 200 °C (d).

## Download English Version:

# https://daneshyari.com/en/article/8035148

Download Persian Version:

https://daneshyari.com/article/8035148

<u>Daneshyari.com</u>