ELSEVIER

Contents lists available at ScienceDirect

## **Precision Engineering**

journal homepage: www.elsevier.com/locate/precision

# Experimental investigation of the optimal laser-induced microbridges

Kuan-Jung Chung<sup>a,\*</sup>, Joseph B. Bernstein<sup>b</sup>

- <sup>a</sup> Department of Mechatronics Engineering, National Changhua University of Education, No.2 Shida Rd., Changhua 500, Taiwan, ROC

- <sup>b</sup> Department of Mechanical Engineering, University of Maryland, College Park, MD 20742, USA

#### ARTICLE INFO

Article history:

Received 16 September 2008

Received in revised form

21 September 2009

Accepted 12 February 2010

Available online 20 February 2010

Keywords: Microbbridges Laser processing materials IC interconnects Laser energy window ASICs

#### ABSTRACT

Three new microbridge structures, which are able to form lateral-and-vertical links simultaneously in the metal layers of ICs for low resistance interline connections, are presented in order to solve the issue of undesirable links occurred after laser processing. Comprehensive laser processing experiments were performed to verify these designs. The results show that there exits different performance (electrical resistances) and laser energy windows for these structures. There is no perfect design so that one structure (S2) is selected as an optimal structure by considering of the production reality with respect to the highest yield first and then wider energy window, though it only presents the second low resistance.

In addition, the same experiments were performed with the scaled-down structure sizes and two additive factors, relative process window and minimum resistance and its variation, are applied as the criteria to evaluate the scalability of these structures. The structure (S2) is selected as an optimal structure since it is the best design for scalability and it has a low resistance in the small scale. Therefore, structure 2 is determined to be the optimal microbridge design for all structures and scales due to the wide laser energy window, low resistance, high yield, and the best scalability. Moreover, it is able to achieve the fundamental requirements of low power consumption and current leakage for most applications of ASICs.

© 2010 Elsevier Inc. All rights reserved.

#### 1. Introduction

Laser processing techniques have presented widespread applications in the repair of integrated circuit on semiconductor chips for yield enhancement, and in certain custom-made ones. A focused laser pulse is employed to cut the polysilicon "fuses" in defective cells to alter the signal paths to the other functional redundancy ones. The fuses are generally fabricated by heavily doped polycrystalline silicon lines connected by vias to the metal signal buses, and covered with the glass passivation layer in order to adopt standard semiconductor manufacturing processes [1]. The cutting lines in these fuses have been widely applied with dynamic and static RAMs to improve yields [2].

An alternative laser defect avoidance (redundancy) technique is to connect the collection of digital inverters, gates, counters, and other customized circuit blocks to create a specific or new function for the IC. Cook et al. are one of these pioneers to develop connect and disconnect conductors on FET chips using nanosecond nitrogen dye laser pulses, and showed promise for high yield and reliability [3]. Cohen et al. [4] developed the theoretical model of the laser melting thin conducting lines, and it agreed well with

Nowadays the integrated circuits are getting dense and complicated to drive the metallization process toward fine pitch conductors. The laser cutting technique has become increasingly difficult to obtain high yield due to the lower corner cracks at the metal lines after processing since they use more laser energy than linking technique. Bernstein et al. [8] showed that the unfavorable cracks by cutting lines damage the intermetal layer to lead the reliability issue such as current leakage and cross-talk between conductors. Hence, the laser energies are limited in order to obtain a clean cut. Later, they developed a only laser formed connection

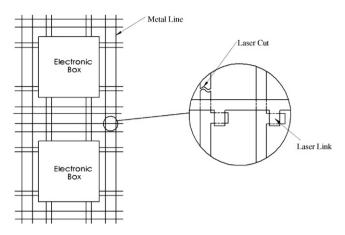

the experimental results. They designed a large area restructurable VLSI circuit that used laser radiation for both cutting lines and forming links, shown in Fig. 1 (schematic description). The cutting line is to cut lower metal aluminum lines to open the electrical routes, and the forming-link used a metal-to-metal layer is to connect lines. These structures are generally made by the last step of semiconductor device manufacturing called metallization processes, involved a first layer of 1  $\mu m$  Al–Cu pad, an intermetal layer of 1.5  $\mu m$  SiO<sub>2</sub>, a second layer of 1.5  $\mu m$  Al–Cu pad, and top layer of 2  $\mu m$  glass layer [5]. Later more devices have been developed using laser additive redundancy techniques to connect the programmable logic arrays (PLAs) [6,7], and now these devices are called application specific integrated circuits (ASICs).

<sup>\*</sup> Corresponding author. Tel.: +886 4 7232105x7815; fax: +886 4 7211149. E-mail address: kjchung@cc.ncue.edu.tw (K.-J. Chung).

**Fig. 1.** Schematic description of programmable VLSI circuits using laser radiation, developed by Cohen et al. [4].

without any cutting line, called MakeLink<sup>®</sup>, <sup>1</sup> and showed much greater promise with wide laser energies and high yields in redundant and programmatic devices [9–12].

The design of MakeLink is classified by lateral-link and vertical-link. The first structure of lateral-link is a direct metal-to-metal connection between two adjacent metal lines on the same level of metallization. The energy of a pulsed laser absorbed mostly by the metal generates enormous thermal stress to break the surrounded dielectrics, then the molten metal fills the crack to form the link [11,13]. The second vertical-link is formed by the same mechanism but the link connection is between two different levels of metallization. The vertical-link structure has several advantages such as smaller size design and higher reliability [14,15]. Many applications such as Laser PROM, laser field programmable gate array (LFPGA), and analog array (LFPAA) have been developed using MakeLink structure as the connections between circuit blocks [16,17].

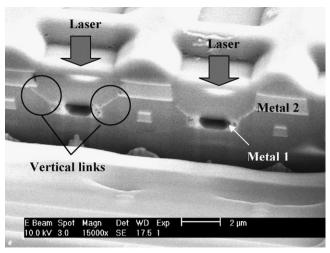

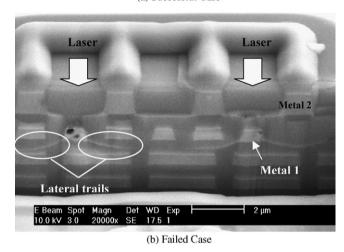

Although MakeLink has demonstrated its advantages in many ASIC designs, the low yield was still found in certain devices after laser processing. This is because the preceding design did not form desirous of links by an orientation for all applications due to the variation of metallization process and material selection in different wafer manufacturers. Fig. 2 presents the cross-section pictures of failed case occurred in our previous work. Section (a) and (b) are the same vertical link design, but the chip provided by two wafer manufacturers for different applications. Section (a) has been demonstrated to succeed in forming desirous of vertical links, but section (b) shows that the vertical link was being substituted by lower corner lateral trail after laser processing so that the low yield occurred. To avoid the issue of different orientations (vertical and lateral) obtained by different suppliers at the same design (one type of link allowable), we develop three novel MakeLink-like structures, called Microbridge, which is capable of forming a successful link whatever lateral, vertical or laterally-and-vertically oriented. The aim of the study is to evaluate these candidates by a series of laser zapping experiments, and then an optimal structure was selected for different applications.

The verification experiments were performed to find laser energies windows under an optimal laser spot size, performance of microbridges (electrical resistance), and yield among these candidates. In addition, the same experiments were performed with the scaled-down structure sizes and two additive factors, relative process window and minimum resistance and its variation, are applied

(a) Successful Case

Fig. 2. The cross-sectional picture of vertical-link design (after processing).

as the criteria to evaluate the scalability of these structures. According to experimental results, an optimal microbridge structure is determined to convince of all requirements for the applications of microelectronic devices.

### 2. Experimental

#### 2.1. Structure parameters

Three types of new structures are designed in this study, schematically shown in Fig. 3. The top layer, called metal 2 (M2), is a rectangular metal frame, and maintains the same size for three designs. Compared to the previous single-line design, the second layer, called metal 1 (M1), is a two-line design for structures 1 and 2 (S1, S2), and three-line design for structure 3 (S3). The pitch of lines is 2.2  $\mu$ m for all of structures. The multi-line design of metal 1 layer involves one line (S1, S2) or a pair of lines (S3) connected to the metal frame by several vias (vertical columns), and another line is the target of laser processing where it is capable of forming a lateral-link with adjacent lines (P1) or a vertical link with the metal frame (P2), or a lateral-and-vertical link (P1 plus P2). Compared to S2, S1 has a wider metal line and no lateral gap with the upper metal frame in order to estimate the yield due to the effect of lateral gap.

To evaluate the yield of mass production by processing as many as links, each structure was repeatedly laid out to form two unique chains, schematically shown in Fig. 4 (in case of structure 2). Links were connected in series chains of 2016 connections. Every link had

<sup>&</sup>lt;sup>1</sup> MakeLink® is a US registered trademark for laser programmed 'microbridge' connections, owned by Professor Joseph B. Bernstein from the University of Maryland.

## Download English Version:

# https://daneshyari.com/en/article/805303

Download Persian Version:

https://daneshyari.com/article/805303

Daneshyari.com