#### Available online at www.sciencedirect.com

Nuclear Instruments and Methods in Physics Research B 237 (2005) 62-67

www.elsevier.com/locate/nimb

### Application of ultra-high energy boron implantation for superjunction power (CoolMOS<sup>TM</sup>) devices

J. von Borany <sup>a,\*</sup>, M. Friedrich <sup>a</sup>, M. Rüb <sup>b</sup>, G. Deboy <sup>c</sup>, J. Butschke <sup>d</sup>, F. Letzkus <sup>d</sup>

<sup>a</sup> Forschungszentrum Rossendorf e.V., Institute of Ion Beam Physics and Materials Research Dresden, P.O. Box 51 01 19, D-01314 Dresden, Germany

<sup>b</sup> Infineon Technologies Austria AG, Villach, Austria

<sup>c</sup> Infineon Technologies AG, München, Germany

<sup>d</sup> Institut für Mikroelektronik, Stuttgart, Germany

Available online 15 June 2005

#### **Abstract**

Superjunction devices (SJDs) are a novel class of power devices which break the physical limit of silicon with respect to the area-specific turn-on-resistance. SJDs consist of a modified vertical MOSFET structure which is characterized by additional deep pillar-like p-type regions formed inside the n<sup>(-)</sup> epi-layer below the transistor gate. In the present investigation ultra-high energy boron ion implantation of 2-25 MeV was applied for forming the deep p-type regions laterally structured using Si stencil masks. For energies above 12 MeV the incident ions exceed the Coulomb barrier for Si which leads (i) to a significant gamma and neutron emission during implantation and, (ii) an activation of the wafer and the mask material. However, the most relevant reaction for activation ( $^{11}B + ^{28}Si \rightarrow ^{39}K(n\alpha) \rightarrow ^{34m}Cl(\beta, EC) \rightarrow ^{34}S)$ has a half-life time of only 32 min, hence the radiation level of the wafers drops below the critical limit within the processing time. Based on the described technology Infineon Technologies successfully prepared a set of prototype wafers with fully functional high-voltage transistors. Typical blocking capability was approx. 560 V with an area-specific turnon-state resistance of about 3.85  $\Omega$  mm<sup>2</sup>.

© 2005 Elsevier B.V. All rights reserved.

PACS: 61.72.Tt; 61.80.Jh; 81.05.Cy; 85.30.Tv; 85.40.Ry

Keywords: Power devices; Silicon; Ion implantation; Doping; Accelerator; Radiation

Corresponding author. Tel.: +49 351 260 3378; fax: +49 351 260 3438. E-mail address: j.v.borany@fz-rossendorf.de (J. von Borany).

#### 1. The device concept

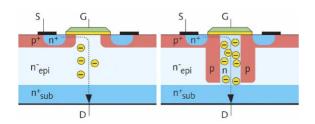

High-voltage superjunction devices (SJDs), firstly realized by Infineon's CoolMOS<sup>TM</sup> technology, are a novel class of power devices which break the physical limit of silicon with respect to the area-specific turn-on-resistance value ( $R_{\rm on} \times A$ ) [1]. Such SJDs consist of a modified vertical MOS-FET structure characterized by additional deep pillar-like p-type regions formed inside the  $n^{(-)}$  epi-layer below the transistor gate, see Fig. 1. Charge compensation between p- and n-type regions leads to an electron accumulation in the drift layer between the p-type columns which results in a reduction of ( $R_{\rm on} \times A$ ) up to a factor of 10 without any loss in the blocking capability. SDJs were introduced into the market between 1998 and 2000

Fig. 1. Schematic cross-sections of a classical MOSFET and a  $CoolMOS^{TM}$  power device.

[2–4]. On a commercial scale the vertical stack is presently fabricated with a high effort by repeated cycles of n-type epi-layer growth, masked boron implantation at common energies and subsequent diffusion. There are numerous suggestions for alternative technologies, most of them involving a deep trench structure [5,6]. The novel approach described in this contribution uses ultra-high energy boron implantation to form the p-type pillars. This concept represents a major simplification of SJDs fabrication since the overall number of process steps is drastically reduced.

## 2. Device preparation including masked ultra-high energy ion implantation

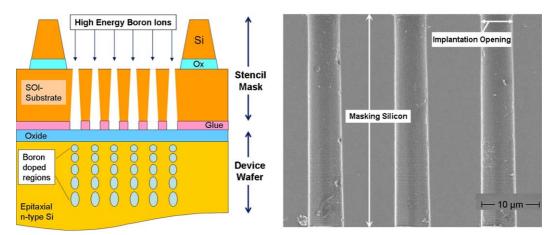

The fabrication of CoolMOS<sup>TM</sup> devices including high-energy boron implantation has been investigated based on the conventional Infineon's MOSFET power device technology.  $\emptyset$  6" Si(001) wafers with a n<sup>(-)</sup>-type epi-layer ( $\rho \sim 2~\Omega$  cm) of approx. 40  $\mu$ m thickness have been used. For the patterned implantation of high-energetic boron ions, reusable Si stencil hardmasks were developed by IMS Stuttgart [7]. The hardmasks were fabricated from SOI wafers (500 nm buried oxide, 22  $\mu$ m SOI). In order to ensure safe masking even

Fig. 2. Sketch of the wafer/mask stack as used for ultra-high energy boron implantation; the right part of the figure shows a cross-sectional SEM-image of the etched Si stencil mask with the implantation openings.

### Download English Version:

# https://daneshyari.com/en/article/9817721

Download Persian Version:

https://daneshyari.com/article/9817721

<u>Daneshyari.com</u>