| Article ID | Journal | Published Year | Pages | File Type |

|---|---|---|---|---|

| 709696 | IFAC Proceedings Volumes | 2012 | 6 Pages |

Abstract

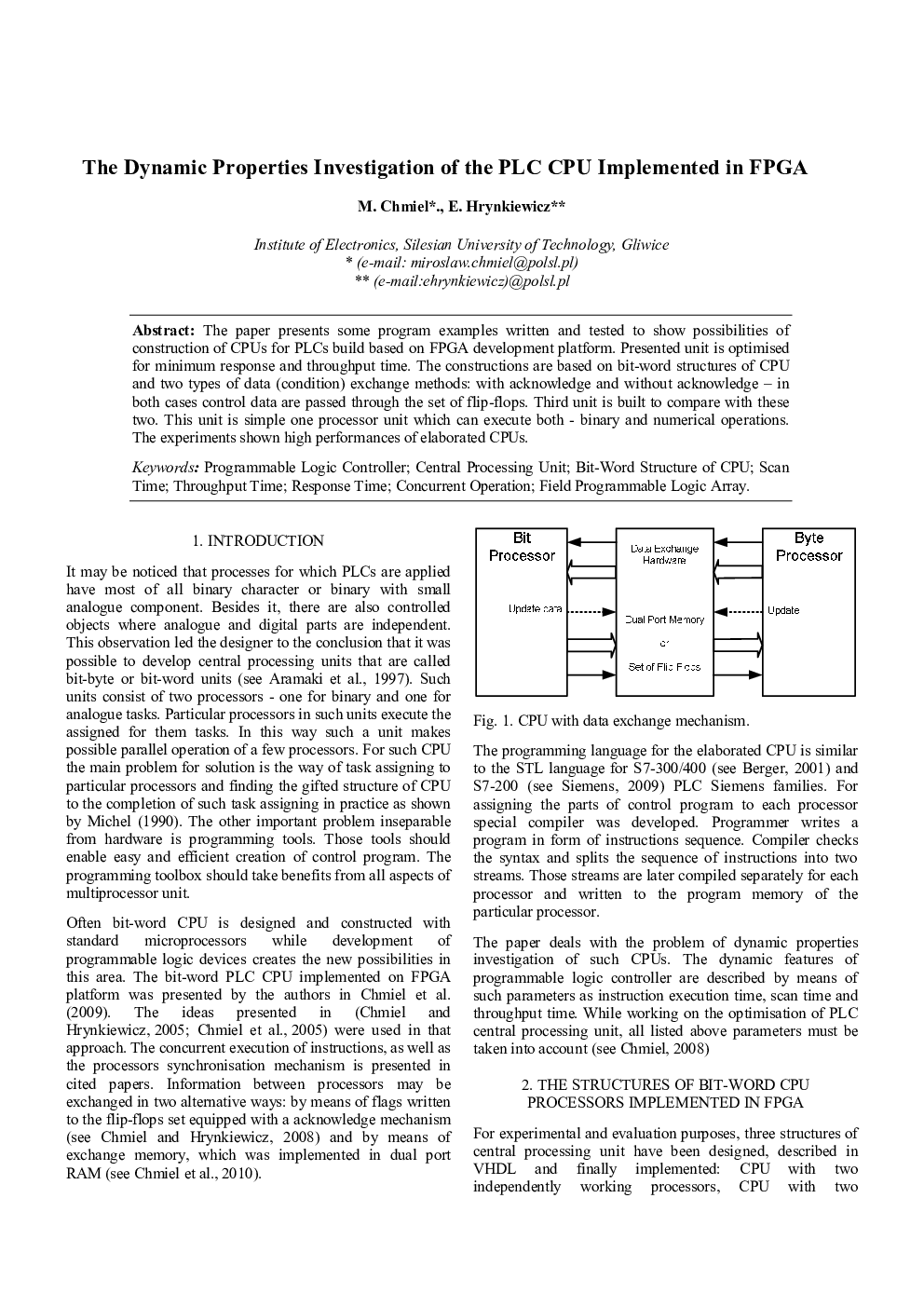

The paper presents some program examples written and tested to show possibilities of construction of CPUs for PLCs build based on FPGA development platform. Presented unit is optimised for minimum response and throughput time. The constructions are based on bit-word structures of CPU and two types of data (condition) exchange methods: with acknowledge and without acknowledge – in both cases control data are passed through the set of flip-flops. Third unit is built to compare with these two. This unit is simple one processor unit which can execute both - binary and numerical operations. The experiments shown high performances of elaborated CPUs.

Related Topics

Physical Sciences and Engineering

Engineering

Computational Mechanics