| Article ID | Journal | Published Year | Pages | File Type |

|---|---|---|---|---|

| 709879 | IFAC Proceedings Volumes | 2012 | 6 Pages |

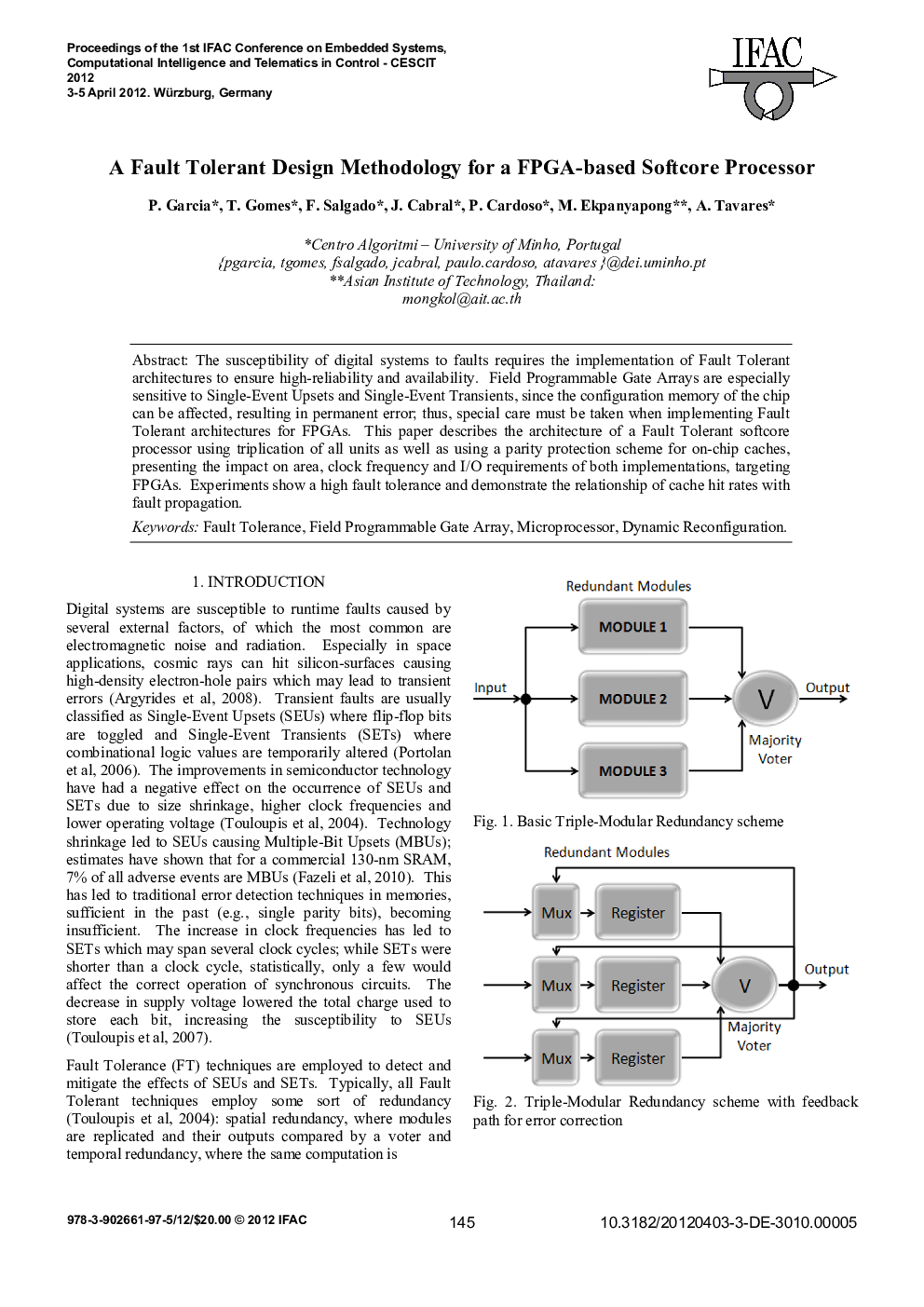

The susceptibility of digital systems to faults requires the implementation of Fault Tolerant architectures to ensure high-reliability and availability. Field Programmable Gate Arrays are especially sensitive to Single-Event Upsets and Single-Event Transients, since the configuration memory of the chip can be affected, resulting in permanent error; thus, special care must be taken when implementing Fault Tolerant architectures for FPGAs. This paper describes the architecture of a Fault Tolerant softcore processor using triplication of all units as well as using a parity protection scheme for on-chip caches, presenting the impact on area, clock frequency and I/O requirements of both implementations, targeting FPGAs. Experiments show a high fault tolerance and demonstrate the relationship of cache hit rates with fault propagation.