| Article ID | Journal | Published Year | Pages | File Type |

|---|---|---|---|---|

| 719516 | IFAC Proceedings Volumes | 2010 | 6 Pages |

Abstract

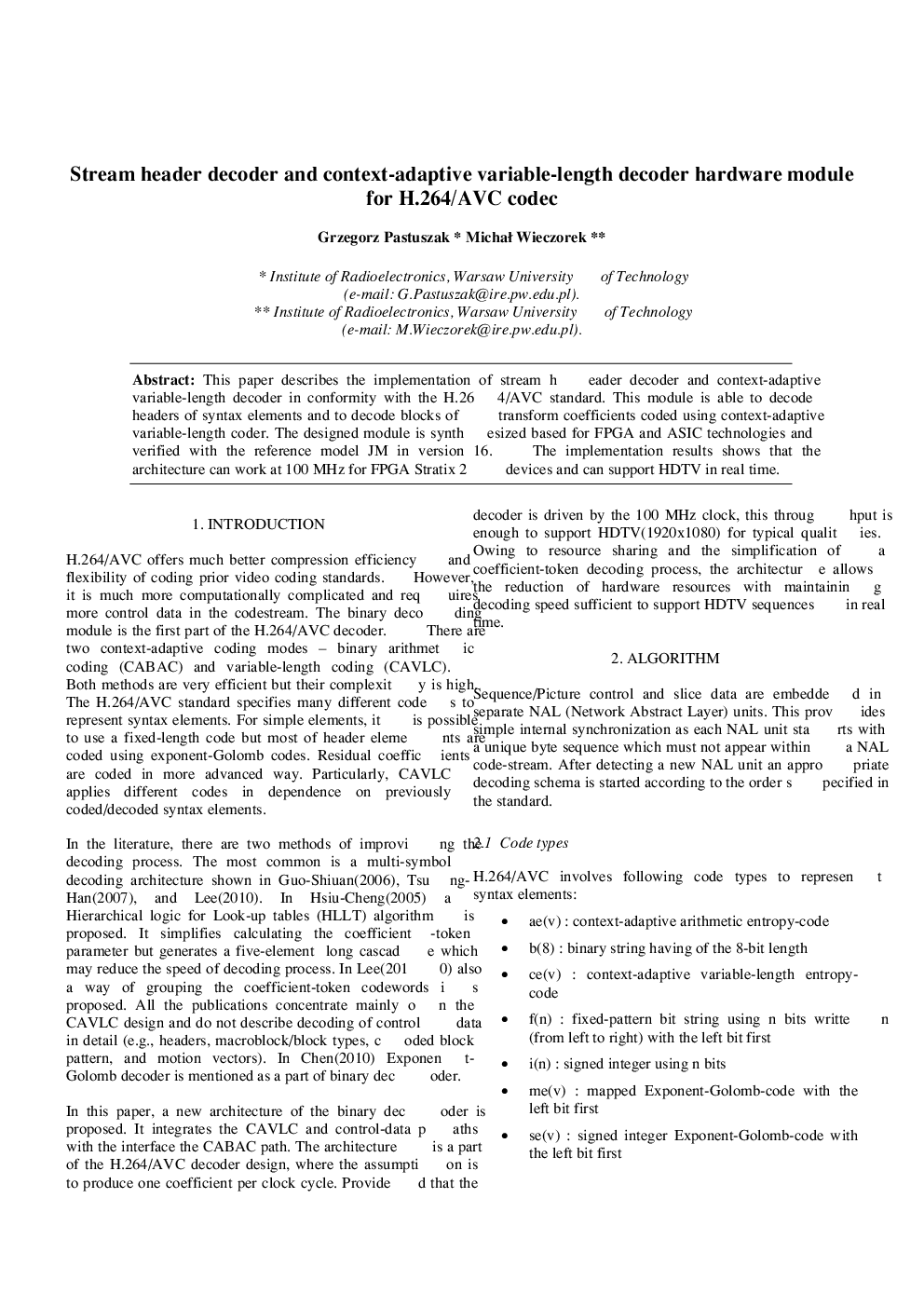

This paper describes the implementation of stream header decoder and context-adaptive variable-length decoder in conformity with the H.264/AVC standard. This module is able to decode headers of syntax elements and to decode blocks of transform coefficients coded using context-adaptive variable-length coder. The designed module is synthesized based for FPGA and ASIC technologies and verified with the reference model JM in version 16. The implementation results shows that the architecture can work at 100 MHz for FPGA Stratix 2 devices and can support HDTV in real time.

Related Topics

Physical Sciences and Engineering

Engineering

Computational Mechanics

Authors

Grzegorz Pastuszak, Michal Wieczorek,