| Article ID | Journal | Published Year | Pages | File Type |

|---|---|---|---|---|

| 719542 | IFAC Proceedings Volumes | 2010 | 4 Pages |

Abstract

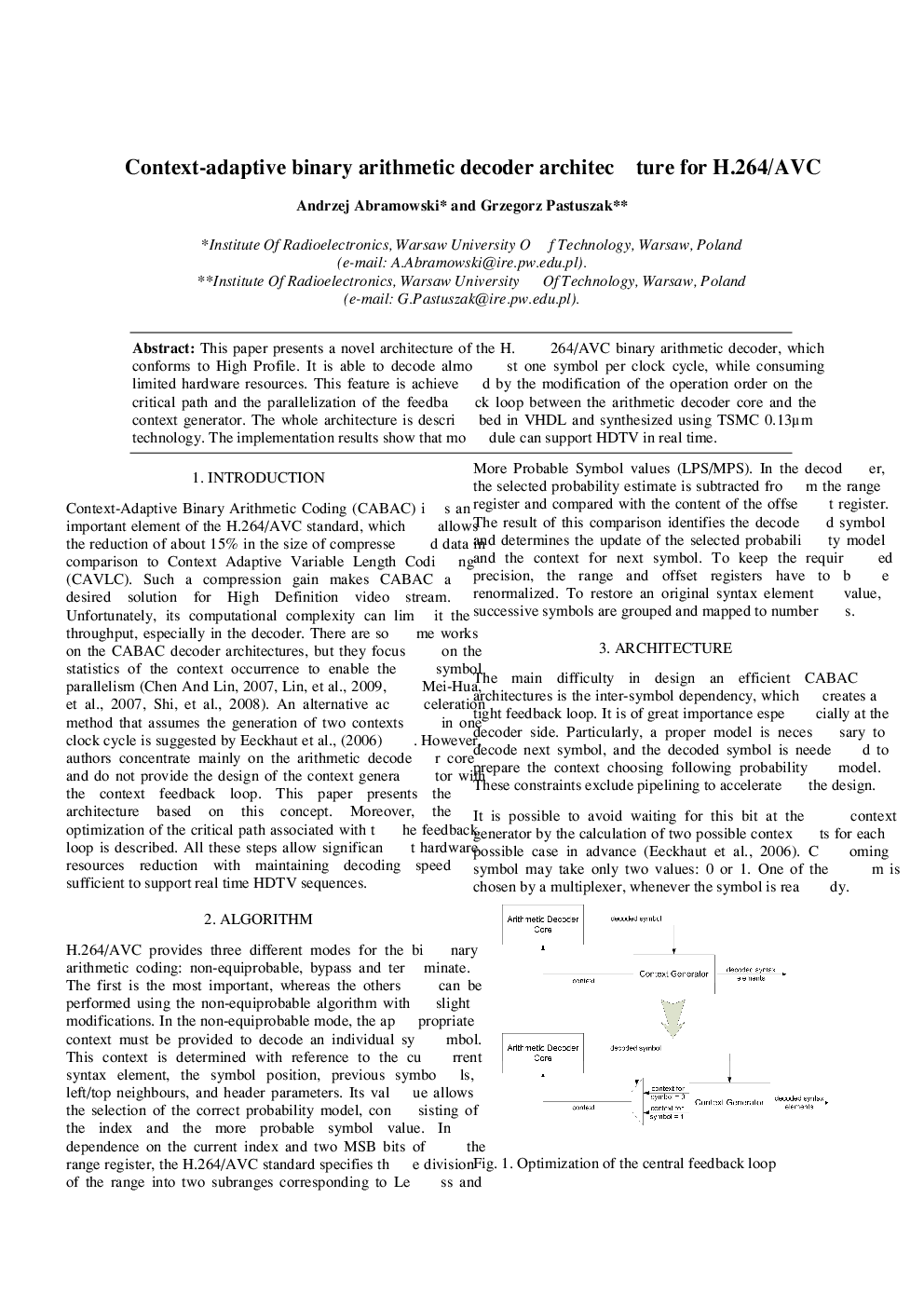

This paper presents a novel architecture of the H.264/AVC binary arithmetic decoder, which conforms to High Profile. It is able to decode almost one symbol per clock cycle, while consuming limited hardware resources. This feature is achieved by the modification of the operation order on the critical path and the parallelization of the feedback loop between the arithmetic decoder core and the context generator. The whole architecture is described in VHDL and synthesized using TSMC 0.13μm technology. The implementation results show that module can support HDTV in real time.

Related Topics

Physical Sciences and Engineering

Engineering

Computational Mechanics

Authors

Andrzej Abramowski, Grzegorz Pastuszak,