| Article ID | Journal | Published Year | Pages | File Type |

|---|---|---|---|---|

| 1659698 | Surface and Coatings Technology | 2010 | 5 Pages |

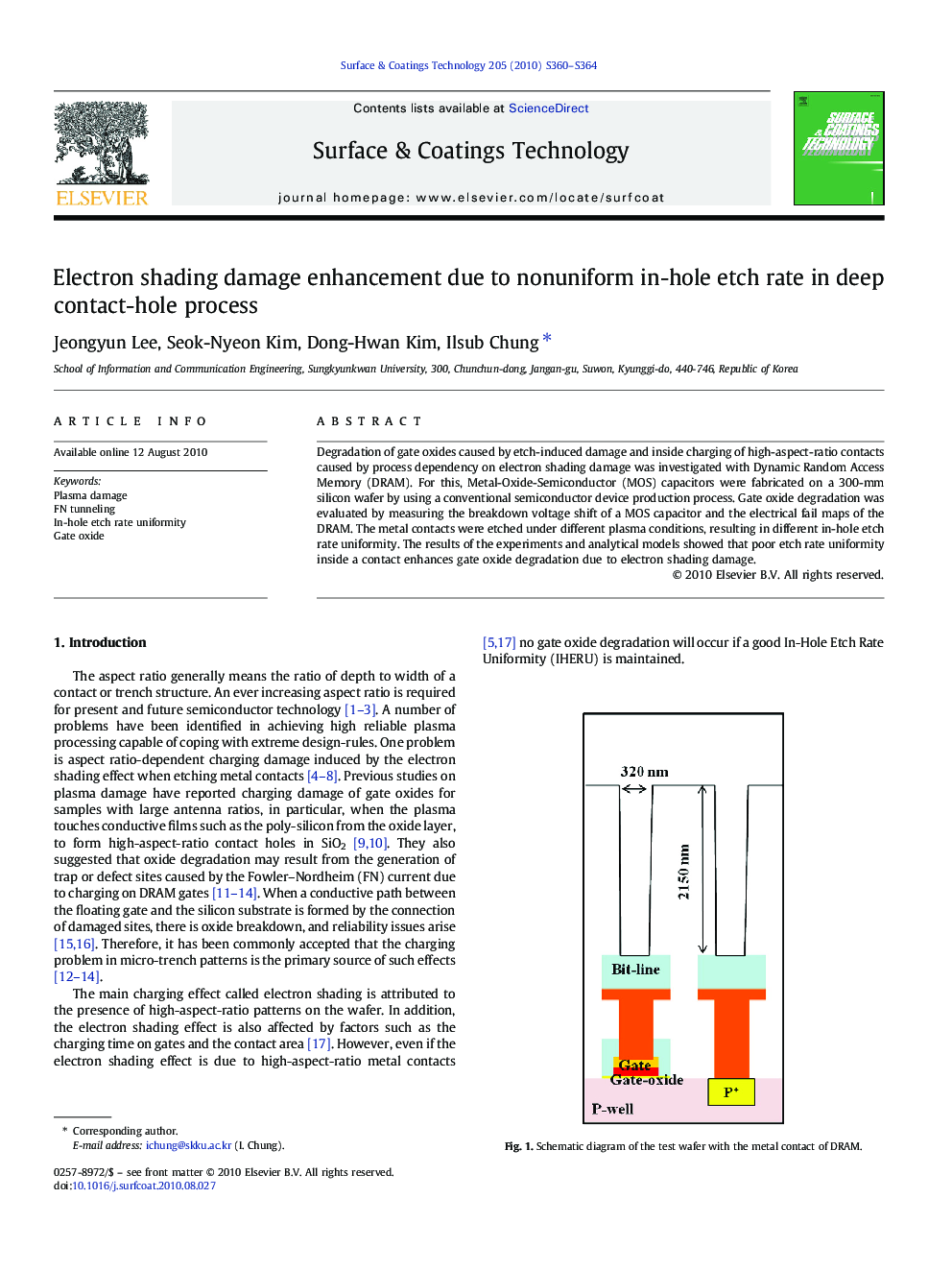

Degradation of gate oxides caused by etch-induced damage and inside charging of high-aspect-ratio contacts caused by process dependency on electron shading damage was investigated with Dynamic Random Access Memory (DRAM). For this, Metal-Oxide-Semiconductor (MOS) capacitors were fabricated on a 300-mm silicon wafer by using a conventional semiconductor device production process. Gate oxide degradation was evaluated by measuring the breakdown voltage shift of a MOS capacitor and the electrical fail maps of the DRAM. The metal contacts were etched under different plasma conditions, resulting in different in-hole etch rate uniformity. The results of the experiments and analytical models showed that poor etch rate uniformity inside a contact enhances gate oxide degradation due to electron shading damage.